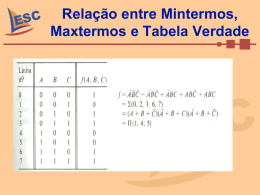

Hardware Description Language Aula 2 Prof. Afonso Ferreira Miguel, MSc Digital System Design Requirements Functional Design Behavioral Simulation Register Transfer Level Design RTL Simulation Logic Design Logic Simulation Circuit Design Timing Simulation/Circuit Analysis Physical Design Description for Manufacture Design Rule Checking Digital System Design Modelo de negócio: Retorno x Tempo Digital Logic Circuit Definitions • • • • MOS: metal-oxide-silicon (primeira tecnologia); TTL: transistor–transistor logic; CMOS: complementary MOS; Gates: unidade de medida de densidade de CIs (twoinput NAND gate/ four CMOS transistors); • SSI, MSI, LSI, VLSI: Small, Medium, Large, Veri Large Scale Integration (de portas TTL/CMOS até processadores 64 bits); • ULSI: Ultra Large Scale Integration; Digital Logic Circuit Definitions • ASIC (“a-sick”) application-specific integrated circuit:different types of ICs different types of applications; (sometimes called ASSPs) • not ASICs: memory chips ROMs, DRAM, and SRAM; microprocessors; TTL or TTL-equivalent ICs at SSI, MSI, and LSI levels; • are ASICs: a chip for a toy bear that talks; a chip for a satellite; a chip designed to handle the interface between memory and a microprocessor for a workstation CPU; and a chip containing a microprocessor as a cell together with other logic. “If you can find it in a data book, then it is probably not an ASIC, but there are some exceptions.” Digital Logic Circuit Definitions • PLD: Programmable logic devices PLD HCPLD SPLD High Capacity PLD Simple PLD PLA PAL Programmable Array Logic CPLD Complex PLD FPGA Field Programmable Gate Array Digital Logic Circuit Definitions • PLD > SPLD – ROM, PROM, EPROM, EEPROM Digital Logic Circuit Definitions • PLD > SPLD > PLA (programmable-logic-array): may be configure or programmed to create a part customized to a specific application Gera funções do tipo SDP – Soma de Produto Digital Logic Circuit Definitions Digital Logic Circuit Definitions • PLD > SPLD > PAL (programmable-array-logic) • Também gera funções na forma SDP; • Tecnologia + barata que a PLA, pois são programados apenas as colunas (termos de produto); Digital Logic Circuit Definitions • Tecnologia para interconexão lógica – – – – – – – MASC; Fuse; Anti-fuse; open gate (UV-EPROM); EEPROM; FLASH; SRAM. Digital Logic Circuit Definitions • PLD > HCPLD > CPLD: Complex PLD (multiple interconnected SPLDs). Digital Logic Circuit Definitions • PLD > HCPLD > FPGA: Field programmable gate array Logic Block I/O Block Interconnect Digital Logic Circuit Definitions • PLD > HCPLD > FPGA: Field programmable gate array Digital Logic Circuit Implementation options • Componentes SSI, MSI, LSI – Custo elevado devido ao grande número de peças; – Tempo de primeira falha muito pequeno. • Full-custom VLSI devices (ASIC); • FPGAs. Digital Logic Circuit Implementation • ASIC vs. FPGA – ASIC • • • • + Lower cost per function for high volume + Better functional fit - Design Time - Nonrecurring engineering cost – FPGA • • • • + Short design cycle + Lower cost per function at low volume - Area penalty - Slower performance Digital Logic Circuit Implementation • ASIC vs. FPGA Nonrecurring engineering cost FPGA ASIC Volume • Less expensive at low volume Digital Logic Circuit Implementation FPGA Applications – – – – – – Glue Logic (replace SSI and MSI parts); Prototype design; Dynamic reconfiguration (ISP); Rapid turnaround; Emulation; Custom computing. HDL - Introdução • O mundo antes das HDLs HDL - Introdução • Tradicional x HDLs Conversão manual da descrição do projeto HDL - Introdução • HDL - benefícios • Aplicado a vários níveis de abstração (Interoperability); • Reutilização de código; • Independente de tecnologia - Application-specific Integrated Circuits (ASICs); - Simple Programmable Logic Devices (SPLDs); - Complex PLDs (CPLDs); - Field-Programmable Gate Arrays (FPGAs). HDL - Linguagens • As HDLs mais conhecidas – – – – – – VHDL Verilog HDL AHDL Abel HDL PHDL Handel-C (http://www.celoxica.com) HDL - Ferramentas • Algumas ferramentas para HDL (síntese e simulação) – – – – – – – – – MAXPLUS II QUARTUS Verilog Mode Cypress Warp Silos Verilog HDL Active-HDL Model-Sim Synopsys Fusion/ViewSim AHDL – Design Tools Exclusivamente MAXPLUS II QUARTUS II AHDL • Modularização AHDL • Assinatura (Subdesignd Section) AHDL • Assinatura (Subdesignd Section) AHDL • Implementado funções lógicas AHDL • Pontos intermediários (NÓS) AHDL • Exercício 1 Implementar e simular um Semi-Somador e um Somador-Completo no ambiente Quartus II. Lembrando... •Semi somador: S = A XOR B C = A AND B •Somador Completo S = (A XOR B) XOR Cin Cout = ((A XOR B) AND Cin) OR (A AND B) AHDL • Criando o símbolo de um projeto Tools > Create Symbol Files for Entities in Current File AHDL • Truth Table A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 C 0 0 0 1 AHDL • Exercício 2 – – – Modificar o Somador-Completo para utilizar Truth Table; Criar o símbolo deste módulo; Criar um Block Diagram (chamado de SOMA) e incluir um Semi-Somador e dois SomadoresCompletos para implementar a função de soma de 3 bits: – – – entradas: A2,A1,A0 e B2,B1,B0; saídas: Cout, S2,S1,S0. Compilar e simular o circuito final; AHDL • Incluindo módulos em um arquivo AHDL 1) Abrir arquivo SemiSomador; 2) Tools > Create AHDL Include Files for Entities in Current File; 3) Repetir para o arquivo SomadorCompleto; 4) Incluir no arquivo destino a diretiva “include “nome_do_arquivo.inc”; 5) Adicionar módulos importados na seção Variable. AHDL • Array – Entradas e saídas podem ser vetores – Módulos podem ser vetores também AHDL • Array – As atribuições devem ser com índice AHDL • Operação com vetores – Vetores podem ser operados entre vetores do mesmo tamanho... – ou com um bit. AHDL • Concatenando bits em vetores – Os parênteses podem ser utilizados para concatenar vetores AHDL • Exercício 3 Implementar e simular um circuito que multiplique dois valores de 4 bits (A[3..0] e B[3..0]) gerando um resultado de 8 bits (S[7..0]). Lembrando...

Download

![[ A MARCA ]](http://s1.livrozilla.com/store/data/000069664_1-08c9d391595c8742bfe104f70ad88ecc-260x520.png)