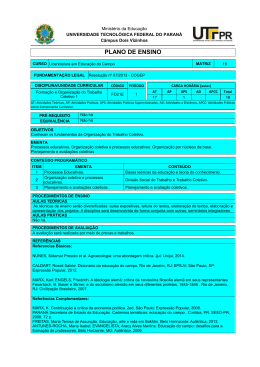

Ministério da Educação UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ Campus Pato Branco PLANO DE ENSINO CURSO 202 - Engenharia Elétrica MATRIZ 510 FUNDAMENTAÇÃO LEGAL Resolução do COEPP No 155-09 de 10/12/09 DISCIPLINA/UNIDADE CURRICULAR CÓDIGO PERÍODO ARQUITETURA E ORGANIZAÇÃO DE AO27EL COMPUTADORES 7 o AT 34 CARGA HORÁRIA (aulas) AP APS AD APCC Total 34 04 00 00 72 AT: Atividades Teóricas, AP: Atividades Práticas, APS: Atividades Práticas Supervisionadas, AD: Atividades a Distância, APCC: Atividades Práticas como Componente Curricular. PRÉ-REQUISITO EQUIVALÊNCIA SD25EL AO26CP OBJETIVOS Estudar os componentes de sistemas computacionais atuais (processadores, memória e periféricos) e investigar as arquiteturas e as relações destes componentes entre si. EMENTA Aritmética para computadores; arquiteturas gerais de computadores; arquiteturas RISC e CISC; unidade central de processamento; unidade lógica e aritmética; instruções e linguagem de máquina; modos de endereçamento; sistemas de memória; pipeline; mecanismos de interrupção; interface com periféricos; arquiteturas paralelas e não convencionais. CONTEÚDO PROGRAMÁTICO ITEM EMENTA Arquiteturas gerais de computadores. 1 Aritmética para computadores. Unidade Lógica e Aritmética. 2 4 5 2.1. 2.2. Sistemas de memória. 3 1.1. 1.2. 1.3. 1.4. 2.3. 3.1. 3.2. 3.3. Interface com periféricos. Mecanismos de 4.1. interrupção. 4.2. 4.3. 4.4. Unidade Central de Processamento. Instruções e linguagem de máquina. Modos de endereçamento. Pipeline. Arquiteturas RISC e CISC. 5.1. 5.2. 5.3. 5.4. CONTEÚDO Histórico dos computadores. Modelo de Von Neumann. Componentes e funções dos computadores. Estruturas de interconexão dos componentes: modelo de barramento do sistema. Representação de dados: números de ponto fixo, números de ponto flutuante e códigos de caracteres. Aritmética computacional: operações aritméticas para números de ponto fixo e números de ponto flutuante. Unidade Lógica Aritmética. Hierarquia do sistema de memória interna: ROM, RAM e memória cache. Conceitos de memória virtual. Sistemas de memória externa: memória de massa. Dispositivos externos. Módulos de E/S. Interrupções. Formas de acesso a dispositivos externos: E/S programada, E/S dirigida por interrupção, acesso direto à memória. Organização do processador e de registradores. Conjunto de instruções: características das instruções, operandos, operações e modos de endereçamento. Ciclo de execução de instruções: busca e execução, interrupções e pipeline. Arquiteturas CISC e RISC. CONTEÚDO PROGRAMÁTICO Arquiteturas Paralelas e não Convencionais. 6 6.1. Processadores superescalares. 6.2. Processamento paralelo: múltiplos processadores, multiprocessadores simétricos, clusters e computação vetorial. PROFESSOR TURMA André Macário Barros 6CP ANO/SEMESTRE 2012/1 AT 36 CARGA HORÁRIA (aulas) APS AD 4 00 AP 38 APCC 00 Total 78 AT: Atividades Teóricas, AP: Atividades Práticas, APS: Atividades Práticas Supervisionadas, AD: Atividades a Distância. DIAS DAS AULAS PRESENCIAIS Dia da semana Segunda Número de aulas no 36 semestre Terça Quarta Quinta Sexta Sábado --- 38 --- --- --- PROGRAMAÇÃO E CONTEÚDOS DAS AULAS (PREVISÃO) Dia/Mês ou Conteúdo das Aulas Semana Apresentação da disciplina. Histórico dos computadores. Modelo de Von Neumann. Março Componentes e funções dos computadores. Estruturas de interconexão dos componentes: modelo de barramento do sistema. Organização do processador e de registradores. Conjunto de instruções: características das instruções, operandos, operações e modos de endereçamento. Abril Ciclo de execução de instruções: busca e execução, interrupções e pipeline. Arquiteturas CISC e RISC. Representação de dados: números de ponto fixo, números de ponto flutuante e códigos de caracteres. Maio/Junho Aritmética computacional: operações aritméticas para números de ponto fixo e números de ponto flutuante. Unidade Lógica Aritmética. Hierarquia do sistema de memória interna: ROM, RAM e memória cache. Junho/Julho Conceitos de memória virtual. Sistemas de memória externa: memória de massa. Dispositivos externos. Módulos de E/S. Junho/Julho Interrupções. Formas de acesso a dispositivos externos: E/S programada, E/S dirigida por interrupção, acesso direto à memória. Junho/Julho Arquiteturas paralelas e não convencionais Número de Aulas 4 16 18 22 16 2 PROCEDIMENTOS DE ENSINO AULAS TEÓRICAS A maioria das aulas teóricas serão expositivas-dialogadas, relatando os conceitos referentes aos conteúdos da ementa e utilizando sistema multimídia e quadro. Algumas aulas teóricas serão feitas através da leitura e discussão de textos. As aulas teóricas são, em geral, expositivas e dialogadas, com pausas para perguntas a serem realizadas pelos alunos ou, na falta delas, pelo professor, a cada unidade de raciocínio concluída. São compostas pelas seguintes partes: breve revisão do assunto abordado nas aulas anteriores; verificação - da parte ou do todo - de exercícios propostos da aula anterior; exposição do tópico principal do encontro; e proposição de exercícios práticos e analíticos a serem realizados durante e/ou depois da aula. Os principais recursos didáticos previstos será o datashow e o quadro negro. ATENÇÃO: há partes constituintes do material que estão no idioma inglês. Não é permitida a saída ou entrada da sala de aula sem o prévio (logo no início da aula ou antes da mesma) consentimento do professor. Alunos em atraso deverão aguardar pelo início do próximo tempo de aula. AULAS PRÁTICAS Durante as aulas práticas os alunos desenvolverão exercícios de fixação dos conteúdos, na forma de lista de exercícios e aulas de laboratório com o uso de ferramentas de simulação e/ou módulos didáticos. Também poderão ser realizados trabalhos de pesquisa com temas propostos pelo professor, além da escrita de artigos científicos e apresentação de seminários. As atividades práticas, dependendo do conteúdo trabalhado, poderão utilizar os seguintes recursos: Plataforma Moodle – Lista de exercícios e material de pesquisa; Ferramentas de simulação – ARC, simuladores de hierarquia de memórias (Universidade de Iowa) e simuladores de memória cache (Universidade de Massachusetts); Módulos didáticos da Digilent – modelos Basys2 e Spartan 3E Starter Kit, ambos da Xilinx. ATIVIDADES PRÁTICAS SUPERVISIONADAS Há duas APS (Atividades Práticas Supervisionadas) previstas. A primeira APS abrangerá conceitos trabalhados nos meses de março e abril e deverá ser entregue neste período. A segunda APS abrangerá conceitos trabalhados nos meses de maio a julho e deverá ser entregue neste período. A primeira e segunda APS serão detalhadas em edital específico ao longo do semestre. ATIVIDADES A DISTÂNCIA Não aplicável. ATIVIDADES PRÁTICAS COMO COMPONENTE CURRICULAR Não aplicável. PROCEDIMENTOS DE AVALIAÇÃO Provas dissertativas e/ou objetivas para avaliação dos conteúdos teóricos e conceituais; atividades práticas presenciais para avaliação dos conteúdos práticos e exercícios; pesquisa, preparação e apresentação de artigo científico e seminário. Bimestres Letivos O conteúdo será trabalhado em dois bimestres letivos: o 1 bimestre: de 05/03 a 07/05/2012; e o 2 bimestre: de 09/05/2012 a 11/07/2012. Avaliação A avaliação é contínua e composta por: a) fator disciplinar; b) participação; c) atividades; e d) provas teóricas. Fator Disciplinar - D: O fator disciplinar é uma nota que inicia o bimestre em 1,0 e recebe ou não decrementos ao longo do bimestre a depender de infrações disciplinares cometidas previstas no regimento disciplinar da instituição. Prova Teórica Bimestral - PRT: Individual e sem consulta. Não é permitido o uso de aparelhos eletrônicos. A primeira prova teórica bimestral ocorrerá em 07/05/2012 e a segunda ocorrerá em 02/07/2012. O conteúdo de cada uma destas provas bimestrais corresponderá ao bimestre que foi concluído. Entretanto o conteúdo é cumulativo, isto é, o conteúdo do segundo bimestre necessita como pré-requisito o que foi visto no primeiro bimestre. Atividades – ATV: São práticas laboratoriais, seminários, trabalhos, testes teóricos e as APS e outras dinâmicas consideradas pelo professor necessárias ao aprendizado. O professor poderá, a seu critério, designar alguma atividade que esteja sendo necessária para que determinado aluno compreenda algum aspecto da matéria que lhe esteja sendo deficitário. Cada uma destas atividades receberá uma nota de zero a dez. Ao final do bimestre, a média aritmética ponderada (algumas atividades poderão valer mais que outras) destas notas corresponderá à média de atividades. Participação - PTC: cada aluno recebe uma nota de zero a dez em cada encontro correspondente à sua participação. Encontro é aqui definido como o conjunto de aulas práticas (2) ou teóricas (2) que ocorrer no dia. O aluno receberá a nota 10,0 em participação em um encontro se, durante todo este encontro: a) chegar no horário de início do encontro; b) sair no horário em que o professor o dispensar os alunos do encontro; c) não se ausentar da sala durante o encontro; d) não utilizar note(net)books, celulares ou quaisquer equipamentos eletrônicos durante o encontro, exceto os momentos em que forem explicitamente solicitados pelo professor durante a aula; e) não dormir durante o encontro; f) não conversar durante o encontro. Ao final do bimestre, a média aritmética das notas diárias de participação corresponderá à média de participação. A participação não é frequência, isto é, um aluno pode vir para a aula, o que lhe será assegurado o cômputo de frequência para a aula em que compareceu a depender do horário. No entanto isto não implica no mesmo ter recebido nota 10,0 em participação (dependerá dos itens (a) ao (f) supracitados). Ainda: da mesma form a que os conceitos associados à ética ou à moral de uma pessoa, ou um aluno participa de um encontro ou não participa, ou seja, recebe 10,0 ou zero, respectivamente. Não há, portanto, nota fracionada entre estes valores. Médias Bimestrais: Cada média bimestral será obtida através da fórumula: MB = D (0,70 PRT + 0,25 ATV + 0,05 PTC ) (1) onde: MB é a média bimestral; D é o fator disciplinar, que varia de 0,0 a 1,0; PRT é a prova teórica bimestral, que varia de zero a dez; ATV é a média das atividades, que varia de zero a dez; e PTC é uma média que corresponderá à participação do aluno nas aulas, que varia de zero a dez. Média Parcial: A média parcial é obtida a partir da fórmula: MP = (MB1 MB2) 0,5 (2) onde MB1 e MB2 são as médias bimestrais correspondentes aos 1o e 2o bimestres, respectivamente. MB1 e MB2 são obtidas a partir da equação (2). ATENÇÃO deverá ser dispensada ao desempenho em ambos os bimestres, pois a média parcial é geométrica! Frequência: O número máximo de faltas nesta disciplina é: N = 0,25 (36 + 38 + 4) = 0,25 78 = 19, 5 19. Média Final: A média final, MF, valerá a média parcial MP, o caso do aluno ter obtido uma média parcial MP 6,0. Caso a média parcial esteja abaixo deste valor, o aluno terá direito a realizar a avaliação de recuperação se tiver pelo menos uma das médias bimestrais estiver acima de 3,6. Neste caso o cômputo da média final será dada pela fórmula: 0,5 MF = (MMP * NRC ) (3) onde: MB é a média final; MMP é a maior média das duas bimestrais; e NRC é nota obtida na avaliação de recuperação. ATENÇÃO: da mesma forma que no cômputo da média parcial MP na equação (2), a média final MF dada pela equação (3) também é geométrica. Aprovação/Reprovação Será considerado aprovado o aluno que tiver: a) uma média final, MF, igual ou superior a seis; e b) um número de faltas igual ou inferior a N. Será considerado reprovado o aluno que: a) tiver as duas médias parciais, MB1 e MB2, inferiores a 3,6; ou b) tiver a média final, MF, inferior a 6,0; ou c) estiver com um número de faltas superior a N. Prova de Recuperação: será em 09/07/2012, prova escrita e individual, cujo conteúdo é a integralidade das aulas teóricas e práticas do sem estre letivo. REFERÊNCIAS Referências Básicas: HENNESSY, John L.; PATTERSON, David A. Arquitetura de computadores: uma abordagem quantitativa. 4a ed. Rio De Janeiro: Elsevier, 2008. Código: 004.22 H515a 4.ed. - 8 exemplares disponíveis no acervo do câmpus. STALLINGS, W. Arquitetura e Organização de Computadores. 8. Ed. São Paulo: Prentice Hall, 2010. TANENBAUM, A. S. Organização estruturada de computadores. 3. ed. Rio de Janeiro: Prentice Hall, c1992. Referências Complementares: HENNESSY, J. L.; PATTERSON, D. A. Organização e projeto de computadores: a interface hardware / software. 2. ed. Rio de Janeiro: LTC, 2000. MURDOCA, M. J.; HEURING, V. P. Introdução à arquitetura de computadores. Rio de Janeiro: Campus, 2000. SEGAL, B.; NAKAJUNE, C. K.; CELESTINO, S. A. Conhecendo a família 80486: hardware e software. 10. ed. São Paulo: Érica, 1992. TAUB, H. Circuitos digitais e microprocessadores. São Paulo: Ed. UTFPR, c1984. xv, 510 p. ZELENOVSKY, R.; MENDONÇA, A. PC: um guia prático de hardware e interfaceamento. 2. ed. rev. atual. Rio de Janeiro: MZ, 1999. ORIENTAÇÕES GERAIS Assinatura do Professor Assinatura do Coordenador do Curso

Download