MICHEL KONESKI JOSÉ ROBERTO BORTOLOTTO JUNIOR SISTEMA DE AVALIAÇÃO DA QUALIDADE DA REDE ELÉTRICA Monografia apresentada ao Curso de Engenharia Elétrica da Universidade Positivo, para obtenção de avaliação da disciplina de Trabalho de Conclusão de Curso (TCC), como requisito à obtenção do grau de Engenheiro Eletricista. Prof. Orientador: Dr. Anselmo Rodrigues. CURITIBA 2008 Agradecemos primeiramente pela oportunidade e o privilégio de cursar e realizar o sonho de se tornar um engenheiro eletricista. Através de uma grande dedicação, não podemos deixar de mencionar os professores Anselmo Rodrigues, Solivan Arantes Valente e Salmo Pustilnick que sempre estiveram presentes e nos auxiliaram nas etapas finais do processo de formação acadêmica. Obrigado a todos os que acreditaram e incentivaram para que este sonho se tornasse realidade. (Michel e José Roberto) ii Dedico este trabalho a minha mãe, Cristina Alves de Souza, que sempre esteve ao meu lado, apoiando e indicando os melhores caminhos a seguir e a minha esposa Claudia Cristina dos Santos que me incentivou em todos os momentos de dificuldades, entendendo e compreendendo minhas escolhas e decisões. (Michel) Agradeço a todos que me apoiaram, depositando confiança e todo o apoio necessário para esta realização, principalmente meu irmão Fábio Prando Bortolotto e meus pais, José Roberto Bortolotto e Oneide Maria Prando, que foram essenciais durante toda esta jornada. Que o grande Arquiteto os ilumine da mesma forma que eu os amo. (José Roberto) iii “Uma mente que se expande com uma nova idéia jamais retornará ao seu tamanho original” (Albert Einstein) iv SUMÁRIO 1 2 3 4 5 INTRODUÇÃO ....................................................................................................................................... 10 1.1 PROBLEMA ................................................................................................................................. 10 1.2 JUSTIFICATIVA .......................................................................................................................... 10 1.3 OBJETIVOS ESPECÍFICOS ........................................................................................................ 11 FUNDAMENTAÇÃO TEÓRICA .......................................................................................................... 12 2.1 POTÊNCIA COMPLEXA E FATOR DE POTÊNCIA ................................................................ 12 2.2 HARMÔNICOS E THD ................................................................................................................ 13 2.3 TRANSIENTES E INTERFERÊNCIA DE RF ............................................................................. 14 2.4 AMOSTRAGEM ........................................................................................................................... 14 ESPECIFICAÇÃO TÉCNICA PRELIMINAR .................................................................................... 15 3.1 DESCRIÇÃO DOS PRINCIPAIS COMPONENTES................................................................... 17 3.2 TRANSFORMADOR DE CORRENTE (TC)............................................................................... 18 3.3 AMPLIFICADOR ......................................................................................................................... 18 3.4 CONDICIONAMENTO DO SINAL ............................................................................................ 19 3.5 DSPIC 33FJ128GP710 .................................................................................................................. 19 3.6 DISPLAY LCD GRÁFICO ........................................................................................................... 20 3.7 MEMÓRIA MMC/SD ................................................................................................................... 20 IMPLEMENTAÇÃO .............................................................................................................................. 22 4.1 DESCRIÇÃO DA MONTAGEM ................................................................................................. 22 4.2 TESTE, MEDIÇÕES E CONFIGURAÇÕES PARA O HARDWARE ........................................ 24 4.3 TESTE, MEDIÇÕES E CONFIGURAÇÕES PARA O SOFTWARE ......................................... 24 4.4 PLACAS DE CIRCUITO IMPRESSO (PCB) .............................................................................. 25 4.5 CUSTOS DO PROJETO ............................................................................................................... 27 RESULTADOS ........................................................................................................................................ 29 5.1 FIRMWARE.................................................................................................................................. 29 5.2 HARDWARE ................................................................................................................................ 29 CONCLUSÃO ..................................................................................................................................................... 33 APÊNDICE A - PROBLEMAS MAIS COMUNS DA REDE ELÉTRICA, SUAS PROVÁVEIS CAUSAS E POSSÍVEIS SOLUÇÕES. ........................................................................................................................ 34 APÊNDICE B – TELAS DO DISPLAY ..................................................................................................... 35 APÊNDICE C – ESQUEMA ELÉTRICO ................................................................................................... 36 REFERÊNCIAS .................................................................................................................................................. 37 LISTA DE FIGURAS Figura 1 Diagrama em blocos de sistema.............................................................................11 Figura 2 Triângulo das potências .........................................................................................12 Figura 3 Janela deslizante.....................................................................................................15 Figura 4 Fluxograma do sistema...........................................................................................16 Figura 5 Fluxograma das rotinas do firmware......................................................................17 Figura 6 Fase de inserção dos componentes na PCB...........................................................23 Figura 7 Imagem da fase frontal do circuito principal PCB (Top Layer) ............................23 Figura 8 Imagem da fase inferior do circuito principal (Button Layer)...............................26 Figura 9 Imagem da fase frontal do circuito principal (Top Layer).....................................26 Figura 10 Imagem da fase inferior do circuito do teclado (Button Layer).............................27 Figura 11 Imagem da fase frontal do circuito do teclado (Top Layer)...................................27 Figura 12 Circuito de aquisição de tensão..............................................................................30 Figura 13 Circuito de aquisição de corrente...........................................................................30 Figura 14 Ensaios realizados..................................................................................................31 Figura 15 Circuito da fonte de alimentação............................................................................32 vi LISTA DE TABELAS Tabela 1 Detalhamento dos custos..........................................................................................28 vii APÊNDICE Apêndice A Problemas mais comuns da rede elétrica, suas prováveis causas e possíveis soluções.............................................................................................................34 Apêndice B Telas do display.................................................................................................35 Apêndice C Esquema elétrico...............................................................................................36 viii LISTA DE SÍMBOLOS/ABREVIATURAS/SIGLAS BUTTON LAYER Face lado da solda CMOS Semicondutor metal-óxido complementar DIP Dual in-line package DSP Micro-controlador especializado em processamento digital de sinais ESD Electric static discharge Fmax Freqüência máxima do espectro FPB Filtro passa baixa Fs Freqüência amostrada ou freqüência de sampling (amostragem) GLCD Grafic liquid crystal display I/O Input/Output IEC Comissão Eletrotécnica Internacional INPE Instituto Nacional de Pesquisas Espaciais MIPS Milhões de instruções por segundo MMC Memory multimedia card Msps Mega Sampling por segundo PCBA Printing component board assembler PLL Phase locked loop PLVD Programação de detecção de baixa tensão RISC Reduced instruction set SD Secure digital SI Sistema internacional de unidades SMD Surface mounted dispositive TC Transformador de corrente TOP LAYER Face lado dos componentes UART Universal asynchronous receiver transmitter WLAN Wireless local area network ix 10 1 INTRODUÇÃO Distúrbios da rede elétrica são problemas reais e inevitáveis, eles afetam o funcionamento da instalação da rede elétrica, sua qualidade e se não forem tratados corretamente, implicam no aumento de gastos em manutenção e diminuição da sua confiabilidade. 1.1 PROBLEMA O principal objetivo deste projeto é tornar possível a identificação dos distúrbios na rede elétrica. Estes distúrbios podem ser causados por: componentes defeituosos, variação de temperatura e umidade, falhas de software, descargas atmosféricas, baixo fator de potência, surtos de tensão, sensibilidade dos equipamentos devido ao fato de seus circuitos serem baseados em semicondutores que operam com baixas tensões, interferência de radio freqüência, transientes e picos, queda e elevação da tensão, presença de harmônicos (CUNHA, 2007). De acordo com estudos, o Brasil é um dos países que mais sofrem com descargas atmosféricas (cerca de 400 milhões de raios por ano), gerando descargas eletromagnéticas que podem produzir surtos de tensão na rede elétrica, danificando diversos equipamentos (INPE, 2008). Como nas instalações elétricas não existem somente cargas resistivas, mas também cargas indutivas e capacitivas, estas geram energia reativa, a maioria na forma indutiva, resultando em baixo fator de potência (ANEEL, 2008). No apêndice A, pode-se observar alguns destes problemas e possíveis soluções (CUNHA, 2007). 1.2 JUSTIFICATIVA Entre os vários problemas que podem ser analisados estão: baixo fator de potência, presença de harmônicos na rede elétrica, surtos de tensão, sub-tensão e sobre-tensão, ruídos do tipo impulsivo, além de alterações gerais de amplitude e freqüência da tensão elétrica. 11 Este analisador poderá se tornar um instrumento bastante útil para o dimensionamento e planejamento de medidas corretivas ou preventivas. A identificação de distúrbios que ocorrem na rede elétrica apresenta relevância na identificação de problemas relacionados com qualidade da energia elétrica. Mantendo-se os distúrbios presentes na rede sob supervisão através da análise dos dados coletados pelo equipamento, será possível economizar valores expressivos em manutenção de equipamentos (medidas corretivas ou preventivas). 1.3 OBJETIVOS ESPECÍFICOS O objetivo deste projeto é o desenvolvimento de um sistema capaz de detectar e identificar distúrbios e problemas que podem ocorrer, como: potência reativa capacitiva e indutiva, baixo fator de potência, sub-tensão, sobre-tensão, presença de harmônicos e THD. O hardware será constituído de: aquisição do sinal, conversão analógico-digital, tratamento dos dados coletados por um DSP (microprocessador especializado em processamento digital de sinais), armazenamento das informações em cartão de memória e apresentação dos dados visualizados em um display gráfico. Figura 1 – Diagrama em blocos de sistema Fonte: Própria Este trabalho utilizará os conceitos de instrumentação, eletrônica, sistemas digitais, circuitos elétricos, algoritmos e processamento digital de sinais. 12 2 FUNDAMENTAÇÃO TEÓRICA Determinados equipamentos, tais como motores elétricos, fornos a arco, transformadores, necessitam para sua operação de uma quantidade de energia reativa, que pode ser suprida por diversas fontes ligadas ao sistema elétrico, funcionando individualmente ou simultaneamente como: geradores, motores síncronos, capacitores. Esta energia precisa ser controlada e monitorada constantemente, pois em excesso na rede elétrica pode causar muitos problemas. 2.1 POTÊNCIA COMPLEXA E FATOR DE POTÊNCIA A potência real P (ativa) é a potência média em watts [W], transmitida à carga. Esta é a única potência utilizada, sendo a potência que realmente é dissipada pela carga. A potência reativa Q é a medida da energia trocada entre a fonte e a parte reativa da carga. A potência aparente S contém toda a informação sobre a potência de uma carga. A parte real de S (aparente) é a potência real P, a parte imaginária de S é a potência reativa Q (veja figura 2). Figura 2 – Triângulo das potências S Fonte: Própria . Q (1) (2) . cos P . Æ P é a parte real de S Æ Q é a parte imaginária de S (3) (4) O fator de potência pode ser definido como sendo a razão entre a componente de potência ativa (P) e a potência aparente (S), este ângulo resulta em um cosseno cujo valor que está entre 0 e 1 (BOYLESTAD, 2004). Ê Ê cos (5) 13 2.2 HARMÔNICOS E THD Os harmônicos são sinais que se constituem de múltiplos inteiros da freqüência da rede elétrica, são produzidos por retificadores, reatores de lâmpadas fluorescentes, fontes de alimentação de computadores e quaisquer dispositivo eletrônico que utilize chaveamento de corrente. Os efeitos destes harmônicos são sobrecarga na fiação de alimentação, falhas em circuitos de alarme e aquecimento de motores. Um sinal periódico qualquer pode ser decomposto em uma série de ondas senoidais, cada uma com uma determinada amplitude e uma determinada fase, mais uma componente da freqüência zero hertz (nível DC). Se a função é periódica, então podemos escrever f(t) usando a série de Fourier: ∑ . . . . (6) Onde os coeficientes a0, an e bn são calculados pelas seguintes equações: (7) . . . . Assumindo a freqüência angular como: Onde e (8) (9) (10) são as amplitudes das funções, cos n. ω. t e sen n. ω. t são o angulo e os ar- gumentos n. ω são múltiplos inteiros positivos da freqüência fundamental. A THD é a distorção harmônica total do sinal aplicado à entrada do equipamento, e medida em sua saída após o sinal ter passado pelos diversos estágios deste equipamento. Distorção harmônica é a deformação causada pela presença de harmônicos, que são múltiplos inteiros da freqüência fundamental do sinal. A THD é expressa em porcentagem, da raiz quadrada da soma dos quadrados das tensões eficazes de cada harmônico dividido pelo valor eficaz da fundamental (VEGTE, 2002). 14 .… 2.3 (11) TRANSIENTES E INTERFERÊNCIA DE RF Transientes são picos de alta tensão de curta duração (micro segundos a nano segundos) que são altamente prejudiciais e podem causar falhas nos equipamentos eletrônicos. As principais causas de transientes são descargas atmosféricas, chaveamento de cargas reativas e equipamentos de solda. As principais causas do surgimento da interferência de radiofreqüência são equipamentos de origem duvidosa, que não atendem as normas definidas pela IEC, uso de dispositivos de chaveamento sem supressão ou filtros, filtros mal dimensionados, acoplamento, falta de blindagem ou conectores impróprios (SADIKU, 2003). 2.4 AMOSTRAGEM É possível recuperar-se totalmente um sinal contínuo a partir de uma coleção de amostras do sinal original, obtidas em um determinado período de tempo. Isto é, sinais que na realidade apresentam-se como continuidades infinitesimais que podem ser recuperados em toda a sua extensão utilizando-se como ponto de partida uma coleção finita de amostras discretas daquelas continuidades. Para isso é necessário que as amostras sejam obtidas em quantidade suficiente para que a informação contida no sinal original possa ser recuperada posteriormente. De acordo com a teoria da amostragem, deve-se obedecer ao critério de Nyquist: no mínimo duas amostras para cada ciclo de um sinal (VEGTE, 2002). 2. Onde: Æ Freqüência de amostragem Æ Freqüência máxima do espectro do sinal (12) 15 3 ESPECIFICAÇÃO TÉCNICA PRELIMINAR O hardware previsto permitirá a captura das informações da rede elétrica que serão encaminhadas para um processador de sinais (DSP). Através de algoritmos implementados, estas informações serão analisadas e servirão para monitoração da rede elétrica. Será composto por um TC, que será utilizado para captar distúrbios da rede elétrica. Através de um processamento digital dos dados captados pelo analisador, será possível a análise das grandezas: V, A, W, Var, Hz, Fp, THD, detecção de harmônicos, detecção de desbalanceamento de fases, variações de freqüência para as freqüências de 60Hz. Estes dados serão armazenados em memória não volátil para a geração de relatórios. Os dados serão captados em tempo real e armazenados para posterior análise, o método de armazenamento será o de janela deslizante, onde será armazenado um frame de n bits. Se este frame apresentar alguma informação de distúrbio, o mesmo será armazenado para futura análise. Já os frames sem informações de distúrbio serão descartados. Figura 3 – Janela deslizante 1 Frame Æ n bits Fluxo de bits do A/D 1 1 0 1 0 1 0 1 1 0 1 0 1 1 1 0 1 0 1 0 0 1 1 1 0 1 0 1 0 1 1 0 1 0 1 1 0 1 Janela deslizante Fonte: Própria 16 Figura 4 – Fluxograma do sistema Modulo de aquisição e condicionamento do sinal Aquisição de dados da rede elétrica através do TC FPB anti-alising Amplificador Informações apresentadas no display de cristal líquido gráfico Conversor AD (Amostragem) Teclado para acesso ao sistema Tratamento das informações o pelo DSP Cartão de memória MMC/SD Fonte: Própria O hardware é constituído de: • Aquisição e condicionamento do sinal: TC, filtro anti-alising composto por um FPB, este sintonizado para corte acima da 32ª harmônica e amplificação do sinal. • Conversão analógico-digital: 17 Com o sinal já condicionado, o mesmo será convertido por um A/D de 10 bits para que posteriormente haja tratamento dos dados coletados. • Tratamento das informações: As informações digitalizadas serão tratadas pelo DSP através de algoritmos desenvolvidos, para a apresentação das informações foi utilizado um display gráfico e para o armazenamento dos dados utilizou-se memória não volátil. As informações serão armazenadas conforme a parametrização do sistema feita pelo usuário. Estes dados serão utilizados para análise e geração de relatórios. Na figura 5 tem-se o fluxograma das rotinas do firmware. Figura 5 – Fluxograma das rotinas do firmware Fonte: Própria 3.1 DESCRIÇÃO DOS PRINCIPAIS COMPONENTES • Transformador de Corrente (TC); • Amplificador; 18 • Condicionamento do Sinal; • DSPIC 33FJ128GP710; • Display LCD Gráfico; • Memória MMC/SD; 3.2 TRANSFORMADOR DE CORRENTE (TC) O TC utilizado é o modelo DTC200, que possui as seguintes características: • Capacidade de medição AC maior que 20-30% dos similares existentes. • Bom isolamento entre primário e secundário. • Muito confiável e desempenho estável em condições de temperaturas diferentes. • Freqüência: 50Hz/60Hz • Temperatura ambiente: -40ºC – 70ºC. 3.3 AMPLIFICADOR O circuito integrado CA3140 é um amplificador operacional que combina as vantagens de alta tensão PMOS e transistores com alta tensão bipolar em um único CI. Este operacional se caracteriza por uma impedância de entrada muito alta, alta velocidade e excelente desempenho podendo operar a uma tensão de alimentação de 4V a 36V. Sua alta impedância de entrada (Zin) típica é 1.5TΩ, baixa corrente de entrada, 10pA em 15 V. Este operacional substitui o típico 741 na maioria das aplicações. Alguns exemplos de suas aplicações são temporizadores / multivibradores (segundos até horas), corrente para instrumentação, detectores de pico, filtros ativos, comparadores, interface de 5V TTL e geradores de funções. 19 3.4 CONDICIONAMENTO DO SINAL Para um correto processamento do sinal captado através do TC, o mesmo deve ser condicionado de forma a conter somente as informações que o DSP está preparado para manipular. Este condicionamento será realizado através da filtragem da banda de freqüências que por ventura possam estar contidos neste sinal, esta banda de freqüências será limitada utilizando-se um FPB, limitando em até 1920Hz, o qual permitirá a captura até a 32ª harmônica. Com esta limitação das freqüências superiores temos também um filtro antialising (anti-alisamento) evitando assim que sinais de alta freqüência possam distorcer as informações desejadas para análise (VEGTE, 2002). Após o sinal condicionado o mesmo será amplificado e estará pronto para ser encaminhado ao conversor analógico digital do DSP. 3.5 DSPIC 33FJ128GP710 O DSP escolhido tem como principais características memória Flash de 128 kbytes para programa, 16 kbytes de memória RAM, 16 Timers de 16 bits, 2 UART’s e 2 ADC’s (um de 10 bits e outro de 12 bits). Sua arquitetura Harvard utiliza uma base de 84 instruções, opera em até 40 MIPS, com clock externo de até 40MHz, sendo possível, com o PLL ativo um clock interno de até 120MHz. Tem-se também como característica, dois conversores Analógico-Digital, 10 ou 12 bits com taxa de conversão de até 1Msps com 32 entradas AD, programação de detecção de baixa tensão (PLVD) e programação de Brown Out Reset. Suas características especiais são: memória de programa Flash pode ser escrita e apagada 10.000 vezes, memória de dados EEPROM pode ser escrita e apagada 100.000 vezes, Power-on Reset (POR), Power-up Timer (PWRT), flexibilidade no Watchdog Timer (WDT), código de proteção programável e programação serial In-Circuit. 20 Com sua tecnologia CMOS temos baixa tensão, memória Flash com tecnologia de alta velocidade, faixa de operação 3V até 3.3V e baixo consumo (TECHNOLOGY, 2007). Este DSP fará todo o controle do sistema como gerenciamento de teclado, display, memória e processamentos das informações coletadas. 3.6 DISPLAY LCD GRÁFICO O display gráfico LCD (GLCD) permite uma avançada visualização das mensagens a serem mostradas além de apenas caracteres alfanuméricos, pois pode exibir mensagens sob a forma de desenhos em bitmaps. O principal motivo da utilização deste display é a possibilidade da implementação de gráficos estatísticos que podem apresentar informações de forma visual, facilitando a compreensão dos resultados obtidos durante a medição. O display escolhido para o projeto tem a resolução de 128x64 pixels e seu contraste pode ser alterado ajustando-se um potenciômetro. O apêndice B mostra alguns dos possíveis menus e telas que poderão ser visualizadas no display do analisador. 3.7 MEMÓRIA MMC/SD O cartão de memória MMC/SD (Multimedia Card / Secure Digital) é usado em dispositivos para guardar informações como mídia de armazenamento portátil, de forma que pode ser removido para ser utilizado ou conectar a um PC, normalmente de tamanho pequeno e que se conecta via conexão USB ou serial. Os cartões de memória SD ou Secure Digital Card são uma evolução da tecnologia, além de ter capacidade de criptografia, fazem também a gestão de direitos digitais (Secure). Possuindo trava para impedir alterações ou apagamento do conteúdo presente no cartão, assim como os antigos disquetes de 3½. 21 Será utilizada uma memória SD, por apresentar o melhor custo/benefício do mercado entre os dispositivos de grande capacidade de armazenamento e fácil mobilidade, desta forma, resolvendo o problema de transferência de dados para o PC para geração de relatórios. O cartão SD utilizado terá uma memória de 4GB, este nos permitirá um tempo de gravação de 33,19 horas de informações somente de distúrbios detectados. Cálculo do tempo da capacidade de armazenamento da memória SD: . . (13) 12 .6 . 3720 267,8 (14) / ou 33,48 ã çã çã çã Onde: D Æ Dados N Æ Número de bits C Æ Número de canais T Æ Taxa de amostragem / , , . (15) (16) 119,5. 10 (17) 33,19 (18) 22 4 IMPLEMENTAÇÃO Os itens abaixo descrevem os procedimentos de configuração, instalação e montagem de software e hardware. 4.1 DESCRIÇÃO DA MONTAGEM Primeiramente, foi utilizado o Circuit Maker (programa de desenvolvimento de layout e esquemas elétricos), para desenvolvimento do hardware. Após a confecção da placa e a inserção dos seus respectivos componentes, iniciou-se a fase de testes parte a parte do circuito. Todo o hardware estava em pleno funcionamento, porém no último teste de funcionalidade que envolvia o GLCD, notou-se que o barramento de dados do display (D0-D7) estava conectado em três I/O diferentes, sendo que o barramento de dados do display deveria permanecer em somente uma porta de comunicação (I/O). Após encontrar a irregularidade no barramento que o display foi conectado e tentar corrigi-lo, percebeu-se que faltaria um conversor analógico digital (A/D), resultando no abandono deste hardware. Após observar que não havia solução para o hardware comentado, verificou-se a necessidade de re-projetar o circuito, desta vez foi utilizado o software Altium, devido a uma perda do banco de dados do software Circuit Maker. Todos os testes foram realizados com sucesso nesta nova versão do hardware, sem a necessidade de simular através da montagem em protoboard. Na figura 6 tem-se a nova PCB em fase se inserção dos componentes. 23 Figura 6 – Fase de inserção dos componentes na PBC Fonte: Própria Figura 7 – Imagem da fase frontal do circuito principal PCB (Top layer) Fonte: Própria 24 Durante o tempo de espera da serigrafia da PCI do novo projeto, iniciou-se o desenvolvimento do firmware através de um módulo de desenvolvimento para DSP, utilizandose o compilador mikroC_dsPIC. Iniciando-se a implementação do firmware, notou-se que o compilador possuía uma vasta e completa biblioteca, porém durante a utilização, o mesmo apresentou alguns problemas que resultariam em dificuldades para o desenvolvimento do projeto. Após a identificação dessa irregularidade, o desenvolvimento do firmware foi alterado para o compilador PICC (CCS – Custom Computer Service), no qual as bibliotecas não são tão completas quanto à do compilador anterior, porém, não apresentou problemas para desenvolvimento de referido firmware. 4.2 TESTE, MEDIÇÕES E CONFIGURAÇÕES PARA O HARDWARE Com a nova placa pronta, iniciou-se uma nova bateria de testes com leds nos terminais do DSP, medição da continuidade entre os periféricos e testes dos pontos de alimentação para verificação dos valores de tensão. Um ponto em destaque é a mudança do primeiro hardware para o segundo, sendo que o primeiro foi implementado manualmente (projeto e desenvolvimento da placa, com componentes convencionais). Já o segundo, somente o projeto foi feito manualmente e a placa foi impressa por terceiros. O principal motivo da PCB ter sido executada por terceiros foi devido à complexidade em se fazer a serigrafia da placa manualmente, além da mesma utilizar componentes SMD. 4.3 TESTE, MEDIÇÕES E CONFIGURAÇÕES PARA O SOFTWARE A implementação do software foi desenvolvida em partes, ou seja, primeiramente o foco foi fazer o teclado se comunicar com o DSP, em seguida implementou-se as telas a serem apresentadas no GLCD. 25 Foram configurados os conversores analógicos digitas para receber e realizar o tratamento do sinal da rede, encaminhando este sinal para que seja processado e analisado pelo DSP. Quando o DSP receber o sinal do conversor A/D, o mesmo tratará o sinal e informará os valores de tensão, corrente, potência e outros que já foram comentados, lembrando que todos esses dados serão armazenados para uma posterior análise. Um ponto importante a ser destacado é a configuração do timer para realizar as interrupções para as chamadas de funções como teclado, imagens, setups de configurações e outros. 4.4 PLACAS DE CIRCUITO IMPRESSO (PCB) A placa foi desenvolvida para utilização de componentes SMD devido à complexidade do circuito, lembrando que se fossem utilizados componentes convencionais (Trhouhg Hole), faltaria espaço para acomodar os componentes em somente uma PCB. Na figura 8 temos as imagens das placas do circuito devidamente identificadas, sendo que, a primeira imagem é a fase de trás da placa conhecida como buttom layer e a segunda imagem é a fase da frente do circuito, conhecida como top layer. 26 Figura 8 – Imagem da fase inferior do circuito principal (Button Layer) Fonte: Própria Figura 9 – Imagem da fase frontal do circuito principal (Top Layer) Fonte: Própria 27 Figura 10 – Imagem da fase inferior do circuito do teclado (Button Layer) Fonte: Própria Figura 11 – Imagem da fase frontal do circuito do teclado (Top Layer) Fonte: Própria 4.5 CUSTOS DO PROJETO Na tabela 1 temos o detalhamento de custos do projeto, componentes, materiais e serviços contratados, onde serão apresentados a listagem geral dos componentes e materiais utilizados. 28 Tabela 1 – Detalhamento dos custos Item 1 2 3 4 5 6 7 8 9 10 11 Quant. 5 2 6 4 4 1 2 2 08 Fonte: Própria Un. pç pç pç pç pç pç pç pç pç pç und Descrição dsPIC33FJ128GP710 Display GLCD 128x64 Transformador de corrente Placa de circuito impresso 176 x 156 mm Placa de circuito impresso 80 x 54 mm Componentes gerais Componentes SMD Gravador de DSP Bastidor PCBA Cabo USB Tipo A-B Impressão de manuais para pesquisa R$ /un. 60,00 38,00 7,00 146,50 35,00 160,00 400,00 170,00 -4,50 78,00 Total Geral Total 300,00 76,00 42,00 586,00 140,00 160,00 400,00 170,00 -9,00 78,00 1.961,00 29 5 RESULTADOS Os itens abaixo descrevem os resultados das implementações concluídas no firmware e no hardware. 5.1 FIRMWARE A principal relevância para dar continuidade sobre as implementações finais foi à alteração do compilador, onde novamente, o MikroC passou-se a ser utilizado. A principal justificativa para o retorno do compilador citado foi à vasta e completa lista de bibliotecas onde o antigo compilador CCS (Custom Computer Service) mostrou-se deficiente quanto à diversidade de bibliotecas necessárias para o desenvolvimento do projeto proposto. Como comentado anteriormente, os passos de implementação do firmware foram: comunicação do teclado com o micro-controlador, imagens das telas que serão apresentadas chamadas através do teclado, ativação das leituras dos conversores analógicos digitais, tratamento do sinal recebido dos conversores e por final, aplicação de cálculos e rotinas para que os valores tensão, corrente, potência, dados sobre harmônicos passem por um processo de adequação para as grandezas conhecidas de acordo com a SI. A mudança do compilador foi primordial para a obtenção dos resultados de forma satisfatória e garantir uma boa operacionalidade do projeto. 5.2 HARDWARE Após a identificação de irregularidades encontrada no hardware e o desenvolvimento do novo projeto, a PCBA não apresentou incoerências no seu funcionamento. Todos os sinais a serem analisados foram grampeados em 1,25V, pois como estes são alternados, as entradas dos conversores AD somente estão preparadas para receber e tratar sinais com amplitude positiva, de 0 a 3.3V. Nas entradas de tensão utilizou-se varístor para a proteção do circuito contra surtos de tensão além de 510V. Na figura 12 temos o projeto do circuito de aquisição de tensão juntamente com o circuito de grampeamento. 30 Figura 12 – Circuito de aquisição de tensão Fonte: Própria Na figura 13 temos o circuito de aquisição, condicionamento e grampeamento do sinal de corrente. Figura 13 – Circuito de aquisição de corrente Fonte: Própria 31 Foram realizados testes em todas as entradas de sinal variando-se a tensão e a corrente aplicada através de um variador de tensão (Varivolt). Para gerar corrente foi utilizado transformador de corrente (TC) como carga, variando de 0 à 200A sem dissipar potência, esta técnica de geração de corrente é uma boa vantagem durante os ensaios de funcionamento. Para o ensaio da FFT, foi utilizado um gerador de sinais programado para gerar uma onda quadrada, a freqüência pode ser alterada para a validação das informações apresentadas pelo equipamento. Na figura 14 temos uma visão dos ensaios realizados. Figura 14 – Ensaios realizados Fonte: Própria O circuito de fonte do sistema é totalmente independente das entradas de tensão e corrente que serão analisadas, a tensão da alimentação é retificada, filtrada e regulada. Foi implementado um sistema de Flip-Flop para o chaveamento do equipamento, ligar ou desligar. Na figura 15 temos o esquema do circuito da fonte de alimentação. 32 Figura 15 – Circuito da fonte de alimentação Fonte: Própria 33 CONCLUSÃO Sabe-se que, distúrbios da rede elétrica são problemas reais e inevitáveis, que afetam o funcionamento da instalação da rede elétrica, sua qualidade, e se não forem tratados corretamente, implicam no aumento de gastos em manutenção e diminuição da sua confiabilidade. Este projeto possibilitou a obtenção de informações reais da rede elétrica, apresentando os valores das grandezas medidas e permitindo que com os resultados obtidos, possa realizar-se a identificação de distúrbios. Mantendo-se os distúrbios sob supervisão, através da análise dos dados coletados pelo equipamento, será possível economizar valores expressivos em manutenção de equipamentos. Uma das principais barreiras para o desenvolvimento deste projeto foi à falta de suporte oferecido pelo fabricante do compilador utilizado MicroC, fazendo com que a solução de alguns conflitos se estendessem por um período elevado, lembrando que o compilador mencionado era desconhecido até o momento. Foi proposto o armazenamento das informações coletadas em um cartão de memória SD para que se pudesse ter um registro. Tal registro deixou de ser implementado devido aos problemas ocorridos com a primeira versão do hardware, gerando grande atraso para a implementação do firmware. Com um período de apenas 6 meses para desenvolver todas as funções do analisador da qualidade da rede elétrica proposto, concluímos que devido à complexidade deste projeto, o tempo necessário para atribuir todas as suas funcionalidades seria de 14 meses. Como melhorias futuras poderiam ser adicionadas outras aplicações, como por exemplo: tornar este analisador dedicado a análise de um equipamento em particular, ou seja, instalar o mesmo definitivamente em cada ponto em que se deseja monitorar. Este poderia enviar relatórios de distúrbios identificados através de comunicação sem fio (WLAN) onde um software de gerenciamento pode controlar e alarmar as irregularidades relevantes. 34 APÊNDICE A - Problemas mais comuns da rede elétrica, suas prováveis causas e possíveis soluções. Categoria do Distúrbio Transientes tipo Impulso Parâmetros para Análise Causas Típicas Amplitude do Pico Forma de Onda Transientes tipo Oscilató- Amplitude do Pico rios Freqüência Valor RMS x Tempo Sag1 / Sweell2 Estatística Raios Varístores ESD Chaveamento de cargas Chaveamento de banco de capacitores Chaveamento de cargas Filtros passivos Rede elétrica de má qualidade ou mal dimensionada Concessionária não confiável Interrupção Sub e Sobre-tensão Duração Valor RMS x tempo Estatística Análise de espectro Distorções Harmônicas Distorção total Estatística Variação da Amplitude Flutuação Freqüências das Ocorrências Possíveis Soluções Varístores Filtros passivos Trafos isoladores Estabilizador de tensão No-break Reprojeto da instalação elétrica Reprojeto da instalação elétrica Sistema de Gerador proteção sem No-break seletividade Partida de motores No-break Variações de carga Cargas não lineaSistemas ressonantes Banco de capacitores Excesso de carga indutiva Cargas intermitentRede mal dimensi- Estabilizador de tensão onada Partida de motores Re-projeto da instalação elétrica Instalação mal dimensionada Fonte: Saber Eletrônica nº 359/Dezembro 2002 – p. 06 1 2 É a redução rápida em amplitude da tensão, esta sub-tensão pode variar o valor nominal de 10% a 90%. É o contrário do Sag, temos uma sobre-tensão que pode variar o valor nominal (RMS) da rede de 10% a 80%. 35 APÊNDICE B – Telas do display Tela Inicial TCC Sistema de Avaliação da Qualidade da Rede Elétrica José Roberto e Michel Koneski Menu 2 Informações Gerais Fase 1 Fase2 Fase 3 [V] [A] [W] Menu 1 Opções para Análise 1 – Inf. Gerais 4 - Harmônicos 2 – Tensão 5 – Potência 3 – Corrente Menu 3 Análise da Tensão Fase1 Fase2 Sub [V] Sobre [V] Fase3 Desbalanc. De fase Menu 4 Menu 5 Análise de Potência Fase1 Fase2 Fase3 Análise da Corrente Fase1 Fase2 Fase3 [A] Defasagem Desbalanc. [A] % Menu 6 Análise de Harmônicos Fase1 Fase2 Fase3 THD % Min. % Máx. Ordem Fonte: Própria [W] +[V.Ar] -[V.Ar] 36 APÊNDICE C – Esquema elétrico R3 10k U1D 12 13 2 R1 R2 33r2 1 TC 1 R4 10kO 14 LM 324 C2 470pF R5 100k0 U2B VCC 3.3V VCC 3.3V bx B by 5V 2 5V GND 1 CD4053 C29 100nF R6 10k0 GND LM1117 3 IN OUT GND b GND R8 33r2 R10 10k0 U2A 14 INH VEE VSS 8 A C4 470pF PT8 12 ax R63 10k R65 10k VCC 3.3V TP1 3.3K U10 MMC/SD CARD R66 10k 1 2 3 4 5 6 7 8 9 GND CD4053 GND VCC 3.3V GND 13 ay 6 11 C60 100nF R64 10k PT7 R11 100k0 a GND 5V PT6 LM 324 7 R7 3 TC 2 U1B 7 5 6 C31 100nF C30 10uF GND R12 10k0 GND GND BZ1 PK12N40 CS Din GND +3.3V SCK GND Dout NC NC INSERT CARD R9 10k 4 2 U9 1 10 PROTECT CARD 15 C1 100nF 10 R75 1k 3.3V 11 GND Q2 BC817 D23 D22 D21 D20 D19 D18 D17 D16 R26 220r C38 100nF GND GND R79 R78 R76 R77 R82 R81 R83 R80 GND GND 10k 10k 10k 10k 10k 10k 10k 10k GND GND GND 3 cy GND CD4053 R19 2.2k 3.3V C8 100nF R20 10k0 C10 470pF GND PT12 3.3V PT13 C9 4.7uF R49 10k PT14 5V GND GND GND PT11 R18 10k0 GND DZ5 LM385BXZ-1.2 C33 100nF R68 10k GND 4 U1C MCU MCLR 5V GND R46 10k0 GND 10 9 8 11 MCLR C11 100nF C28 100nF S13 RESET R47 10k0 LM 324 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 VD R25 100k0 R27 100k0 GND S20K510 R30 100k0 R31 100k0 R32 100k0 R33 100k0 R34 100k0 R35 100k0 R36 20k0 R37 20k0 R38 100k0 R39 100k0 R40 100k0 R41 100k0 R42 100k0 R45 20k0 VAR 3 5V VCC 4013 VCC 4093 5V1 - RTC DZ3 5V1/1W C19 100nF 5V1 5V1 IN OUT GND U3A 1 GND 3 R57 10k C23 22uF R54 100r GND 12 5V 9 CON4 GND 8 11 LIGA DESLIGA 11 8 R55 1k C59 1uF D9 LL4148 R103 100k0 Q CP Q U6 GND C36 100nF 3.3V 4093 SCK WP* SI RST* SO 4 2 5V1 GND 5 6 GND GND 14 Vcc 5 3 4 GND 7 U3B 4093 GND R69 R70 R71 R72 R84 10k 1 4 2 8 7 6 10k 10k 10k 10k 1 2 3 SOBE S1 S2 S3 S15 4 5 6 DESCE S4 S5 S6 S16 7 8 9 S7 S8 S9 8 VCC NC CS SK NC GND SI DO 93LC66B D 1 2 GND GND 1 2 U12 INT OSCO SDA OSCI SCL VSS CLK VDD X2 32.768KHZ 2 1 4 8 D25 R87 220r U13 1 2 3 4 5 6 7 8 C35 1uF GND 3 GND R88 220r C1+ Vs+ C1C2+ C2VsT2out R2in Vcc GND T1out R1in R1out T1in T2in R2out 5 9 4 8 3 7 2 6 1 16 15 14 13 12 11 10 9 MAX 232 R89 10k R90 10k 0 ESC ENTER S10 S11 S12 SUPER CAP R100 1k 5V DB9F GND 10 Q3 BC817 5V 11 R91 10k Q4 BC817 R92 10k R93 10k 5V Q5 BC817 C57 100nF FR1 USB - B R94 27r 1 2 3 4 GND R95 27r GND C51 33nF U14 R96 1.5k 6 8 7 5 4 27 28 32 1 2 31 X4 6MHZ GND C53 100nF C52 100nF C55 33pF C54 10uF ESQUERDA S18 4.4V BAT PT3 C48 0.1F CON9 GND GND D10 LL4148 CON 8 DIREITA S17 TM1 5,2-30pF 4.4V BAT PCF8563 GND C56 33pF 3V3OUT USBDM USBDP RSTOUT# RESET# XTIN XTOUT EECS EESK EEDATA TEST GND C50 100nF R97 470r GND TXD RXD RST# CTS# DTR# DSR# DCD# R# TXDEN TXLED# RXLED PWRCTL PWREN# SLEEP# GND 5V 25 24 23 22 21 20 19 18 16 12 11 14 15 10 R98 220r D11 R99 220r TP2 10k CON 11 D12 GND FT232BL GND GND GND 3 4 R62 10k U15 GLCD 128 X 64 GND U4A Q CP Q GND 7 4013 GND 3 5 6 7 R85 10k 5V C25 1uF CON6 1 GND C47 100nF 10 7 5 GND GND 5V1 Vcc 14 U4B 4013 C44 22pF C45 100nF C3 1uF C37 100nF GND U8 8 6 C27 100nF GND Q1 BC817 12 CS* GND AT45DB041 VCC 3.3V R58 330R C24 47uF R56 10k 13 U3C 9 GND D 4093 5V1 10 5V1 9 U3D 13 S14 Fonte: Própria 3.3V GND 3.3V GND 6 1 2 R60 10k D15 S BATERIA PT5 R 9V 10 GND C22 100nF R53 100k0 5 VCC 2 IN OUT PT4 GND MCU MCLR 5V UA7805 4093 Q6 BC817 Q7 BC817 C34 100nF GND S MC OFF 2 6 3 VCC 3.3V R C18 1uF GND GND U16 IRF BG30 3 C21 100nF C20 10uF COM R52 100k0 U7 C26 100nF R59 10k U5 R86 100r GND C49 10nF 7 1 D8 LL4148 R102 1k R51 10k GND R74 220r GND 2 GND C43 22pF GND LM1117 3 PT2 GND GND C17 1uF GND 3.3V 3.3V 5V 3.3V X3 29 9 17 GND TERRA MC ON R73 220r CON5 RJ11 - FEMEA R61 10k R50 220r/1W PT1 10MHZ C42 100nF dsPIC33FJ128GP710 3.3V 4 GND C58 1nF/3.5kV C16 3300uF/25V D7 1N4007 D6 1N4007 MC ON MC OFF 3.3V 5V1 GND VCC 3.3V 120VAC R101 10k 1 2 3 4 5 6 3.3V D14 GND 3.3V 5 GND COM NEUTRO GND 32.768KHZ GND D24 VCC 3.3V D5 1N4007 C41 22pF X1 C15 100nF DZ2 3V9 D4 1N4007 VAR 4 S20K510 VSS PGC2/SOSCO/RC14 PGD2/SOSCI/RC13 OC1/RD0 IC4/RD11 IC3/RD10 IC2/RD9 IC1/RD8 INT4/RA15 INT3/RA14 VSS OSC2/CLK0/RC15 OSC1/CLKIN/RC12 VDD TDO/RA5 TDI/RA4 SDA2/RA3 SCL2/RA2 SCL1/RG2 SDA1/RG3 SCK1/INT0/RF6 SDI1/RF7 SDO1/RF8 U1RX/RF2 U1TX/RF3 3.3V Trans 1 CON3 1 2 D13 GND R48 1k C40 22pF 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 3.3V GND VD GND GND MCU MCLR MCU RB7 MCU RB6 MCU VCC PT17 C14 470pF GND 1 TERRA 9 7 5 3 1 CON 10 D3 BAV99 GND GND FASE 10 8 6 4 2 3.3V S20K510 C46 1nF/3.5kV GND MCLR RB7 RB6 VCC PT16 VD GND GND GND Header 5X2A D2 BAV99 C13 470pF R44 20k0 R43 100k0 GND PT15 VD GND GND GND VAR 2 S20K510 GND C12 470pF R29 20k0 VAR 1 CON2 D1 BAV99 COFS/RG15 VDD AN29/RE5 AN30/RE6 AN31/RE7 AN16/T2CK/RC1 AN17/T3CK/RC2 AN18/T4CK/RC3 AN19/T5CKRC4 SCK2/CN8/RG6 SDI2/CN9/RG7 SDO2/CN10/RG8 MCRL SS2/CN11/RG9 VSS VDD TMS/RA0 AN20/INT1/RE8 AN21/INT2/RB9 AN5/CN7/RB5 AN4/CN6/RB4 AN3/CN5/RB3 AN2/SS1/CN4/RB2 PGC3/AN1CN3/RB1 PGD3/AN0/RB0 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 R24 100k0 GND MCU MCLR R23 100k0 R22 100k0 GND MCLR R21 100k0 VA VB VC VN R28 20k0 J1 J2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 5 GND cx C U11 CS1 CS2 GND VCC Vo RS R/W E D0 D1 D2 D3 D4 D5 D6 D7 RST Vee LED+ LED- c 9 PT10 3.3V C39 10uF C32 100nF 3.3V 30 3 26 13 4 C5 100nF 3.3V 3.3V R67 10k C6 470pF R17 100k0 AVCC VCC VCC VCCIO CON1 VDD U2C AGND GND GNG 3.3V 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 R14 33r2 PT9 C7 100nF 16 R13 5 TC 3 R16 10k0 1 LM 324 AN28/RE4 AN27/RE3 AN26/RE2 CSDO/RG13 CSDI/RG12 CSCK/RG14 AN25/RE1 AN24/RE0 AN23/CN23/RA7 AN22/CN22/RA6 C2RX/RG0 C2TX/RG1 C1TX/RF1 C1RX/RF0 VDD VDDCORE OC8/CN16/RD7 OC7/CN15/RD6 OC6/CN14/RD5 CO5/CN13/RD4 IC6/CN19/RD13 IC5/RD12 OC4/RD3 OC3/RD2 OC2/RD1 U1A 3 2 PGC1/AN6/RB6 PGD1/AN7/RB7 VREF-/RA9 VREF+/RA10 AVDD AVSS AN8/RB8 AN9/RB9 AN10/RB10 AN11/RB11 VSS VDD TCK/RA1 U2RST/RF13 U2CTS/RF12 AN12/RB12 AN13/RB13 AN14/RB14 AN15/CN12/RB15 VSS VDD U1CTS/CN20/RD14 U1RTS/CN21/RD15 U2RX/CN17/RF4 USTX/CN18/RF5 R15 10k 6 GND 37 REFERÊNCIAS BOYLESTAD, R.L.; NASHELSKY, L. Dispositivos eletrônicos e teoria de circuitos. 8 ed. São Paulo: Prentice Hall, 2004. VEGTE, J.V. Fundamentals of digital signal processing. Ohio: Prentice Hall, 2002. SADIKU, M.N.O. Fundamentos de circuitos elétricos. São Paulo: Bookman, 2003. CUNHA, R.L.R. Qualidade da energia elétrica. Saber Eletrônica, Abril de 2007. p. 40 TECHNOLOGY, M.I. dsPIC30F4013 Data Sheet, U.S.A., 2007 INPE. Descargas Atmosféricas. Disponível em: www.inpe.br Acesso em: 23 mar. 2008. ANEEL. Fator de Potência. Disponível em: www.aneel.gov.br Acesso em: 30 mar. 2008.

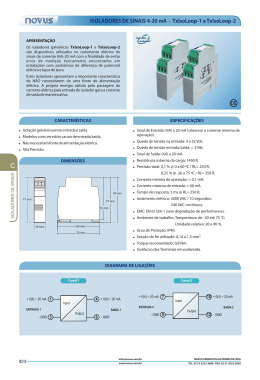

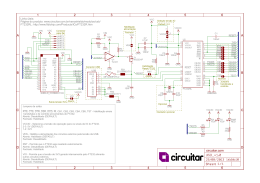

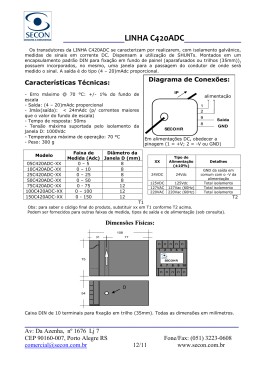

Baixar