Entrada e Saída Interface entre periféricos, processador e memória Fonte: Minho - Portugal 1 Ligação Processador/Memória - Periférico Processador Memória Controlo Controlador Dados Fonte: Minho - Portugal 2 Input / Output 1. Qual o papel do Sistema Operacional (SO)? 2. Como é que os pedidos de I/O são transformados em comandos e comunicados ao periférico? 3. Como é que os dados são transferidos entre o periférico e a memória? Fonte: Minho - Portugal 3 I/O – O papel do Sistema Operativo Age como um interface entre os controladores dos periféricos e o programa que pretende realizar operações de I/O Características dos periféricos: 1. São partilhados por vários programas que correm simultaneamente na máquina; 2. Enviam sinais ao processador para comunicar o seu estado; 3. O controlo de um dispositivo de I/O é, geralmente, bastante complexo. Fonte: Minho - Portugal 4 I/O – O papel do Sistema Operativo Funções do Sistema Operacional: 1. Garante que os utilizadores só têm acesso a periféricos para os quais têm direitos; 2. Gere a multiplicidade de acessos, garantindo uso exclusivo quando necessário e justiça no acesso aos recursos; 3. Atende os sinais gerados pelos periféricos; 4. Esconde a complexidade dos periféricos, fornecendo rotinas que tratam dos aspectos de baixo nível (device drivers). Fonte: Minho - Portugal 5 Comunicação de Comandos Para enviar comandos e receber respostas dos periféricos, o processador tem que ser capaz de endereçar os controladores dos periféricos. Existem 2 formas alternativas de comunicação com os controladores: 1. I/O mapeado em memória - porções do espaço de endereçamento são dedicadas aos periféricos; escritas nestes endereços são ignoradas pela memória e comunicadas directamente ao controlador, podendo ser usadas para enviar comandos ou dados; leituras nestes endereços podem ser usadas para receber dados ou verificar o estado do dispositivo; 2. Instruções especiais para I/O (in, out) – a comunicação com os periféricos é feita usando as instruções in e out, para leituras e escritas, respectivamente. Cada periférico tem um ou mais números que o identificam. A maior parte dos sistemas operativos não permite que os programas do utilizador comuniquem directamente com os periféricos. Todos os comandos têm que ser enviados via Sistema Operativo (system calls). Fonte: Minho - Portugal 6 Comunicação Processador - Periférico Conseguida acedendo a registos do controlador. Genericamente, existem 2 tipos de registos: estado/controle e dados. Registos de estado/controle: Usados pelo controlador para comunicar o seu estado (Ready, erros,...) Usados pelo processador para dar ordens ao controlador Registos de dados: Usados para comunicar/receber dados para/do controlador Fonte: Minho - Portugal 7 Transferência de Dados entre a Memória e os Periféricos Existem essencialmente 3 métodos para transferir dados entre a memória e os periféricos: 1. Polling 2. Orientado às interrupções Diminuição do grau de envolvimento do processador 3. Direct Memory Access (DMA) Fonte: Minho - Portugal 8 Polling – espera activa O processador lê repetidamente os registos de estado dos periféricos, para determinar quando é que estes se encontram prontos para iniciar uma transferência de dados. Repetir Ler Registo de Estado do Controlador Até Controlador=Ready Enviar/Escrever Dados de/para Controlador • Fácil de implementar, mas... • Processador responsável por verificar alterações no estado do controlador e por fazer as transferências de dados. • O processador não pode realizar outras tarefas enquanto a operação de I/O não terminar, mesmo que seja muito mais rápido que o controlador do periférico. Fonte: Minho - Portugal 9 Interrupções O controlador envia ao processador um sinal indicando alterações no seu estado. Interrupções – sinais enviados pelos controladores dos periféricos ao CPU, indicando uma alteração no seu estado. Rotina de atendimento de interrupções – ao receber um sinal de interrupt o CPU interrompe o programa que estava a executar e salta para uma rotina de atendimento de interrupções, que se encarrega da transferência de dados. Esta rotina, regra geral, pertence ao S.O. Excepções – semelhantes às interrupções, mas com origem interna ao CPU. As causas podem ser overflow, instrução desconhecida, mau funcionamento do hardware, divisão por zero, etc. Fonte: Minho - Portugal 10 Interrupções Quando ocorre uma excepção ou uma interrupção a execução salta para uma rotina de atendimento. Mas o hardware tem que indicar qual a causa da interrupção. Existem 2 mecanismos alternativos: 1. Interrupções vectorizadas – existem diversas rotinas de atendimento de interrupções, localizadas em diferentes endereços. Quando surge o sinal de interrupt, a execução prossegue no endereço apropriado. 2. Registo de causa – existem apenas 1 rotina de atendimento de interrupções. Quando surge o sinal de interrupt, o hardware coloca num registo de CAUSA um valor identificativo da interrupção. Mecanismos de atribuição de prioridades: indicam qual a excepção ou interrupção que é atendida primeiro, se se verificarem várias em simultâneo: 1. As excepções têm maior prioridade que as interrupções. 2. Periféricos mais rápidos têm maior prioridade que os mais lentos. Fonte: Minho - Portugal 11 Direct Memory Access Polling O CPU verifica activamente alterações no estado do controlador O CPU é responsável pela transferência de dados Interrupt O CPU é notificado de alterações no estado do controlador O CPU é responsável pela transferência de dados Se a quantidade de dados a transferir for elevada, como, por exemplo, no caso dos discos, o overhead no processador é elevado. Direct Memory Access (DMA) – controlador dedicado a transferir dados entre a memória e outros controladores e vice-versa. O mecanismo de interrupções é utilizado apenas para notificar o CPU de que a transferência terminou ou da ocorrência de erros. Fonte: Minho - Portugal 12 Direct Memory Access – Mecanismo O controlador de DMA assume o papel de bus master e dirige todo o tráfego entre a memória e o controlador do periférico. Uma transferência DMA envolve 3 passos: 1. O CPU indica ao DMA a identidade do controlador, o tipo de operação, o endereço de memória a aceder e o número de bytes a transferir; 2. O DMA inicia a operação, arbitra o barramento e transfere os dados na direcção apropriada; o próprio DMA fornece os vários endereços de memória para todo o bloco de dados a ler ou escrever; é possível completar uma transferência de várias centenas ou milhares de dados sem incomodar o CPU; 3. Uma vez a transferência terminada, o DMA interrompe o CPU, que pode então ler os registos de estado do DMA para determinar se a operação completou com sucesso; Fonte: Minho - Portugal 13 Direct Memory Access – Mecanismo Processador Memória Controlador DMA 1. Início da operação Controlador 2. Transferência de dados Disco 3. Interrupção: Fim ou erro Fonte: Minho - Portugal 14 Direct Memory Access – Dificuldades • O CPU e o DMA acedem simultaneamente à memória, criando problemas de contenção; com a utilização da cache o CPU evita aceder à memória principal a maior parte do tempo, diminuindo a contenção; • Num sistema sem DMA apenas o processador acede à memória; num sistema com DMA temos 2 ou mais componentes a aceder à memória; se o DMA está a fazer uma escrita na memória e esse item também se encontra na cache do CPU, então os dois valores ficam diferentes; se o DMA está a fazer uma leitura da memória e a cache é write-back, então o DMA pode estar a ler um valor desactualizado – problema da incoerência. Soluções 1. Fazer o tráfego do DMA passar pela cache – ineficiente 2. Fazer o S.O. ou o hardware invalidar as linhas da cache que são afectadas pelas escritas do DMA (cache flushing), e forçar o write-back das linhas que são lidas pelo DMA. Fonte: Minho - Portugal 15 Mecanismos de I/O - Comparação Polling O CPU verifica activamente alterações no estado do controlador O CPU é responsável pela transferência de dados Interrupt O CPU é notificado de alterações no estado do controlador O CPU é responsável pela transferência de dados DMA O CPU é notificado de alterações no estado do controlador de DMA O DMA é responsável pela transferência de dados O preço das máquinas é muitas vezes determinado pelas facilidades de I/O de que dispõe: número e velocidade dos barramentos, número e tipo de controladores de DMA, resolução dos problemas de contenção e coerência na memória. Fonte: Minho - Portugal 16

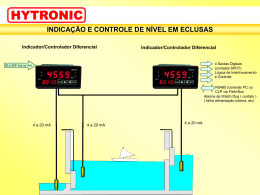

Baixar