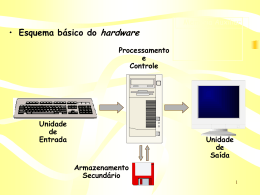

Fundamentos de Sistemas Computacionais Professor: Ricardo Quintão e-mail: [email protected] Site: www.rgquintao.com.br Versão 4.0 Sistema de Numeração • • A base de representação numérica de um número está relacionada com a quantidade de símbolos disponíveis para representar este número. Se tivermos 10 símbolos para as representações numéricas, este número estará sendo representado na base 10, se tivermos 8 símbolos, ele estará na base 8 e assim sucessivamente. 0 Vazio 1 2 3 4 5 6 7 8 9 0 Vazio 1 2 3 Base 4 Base 10 0 Vazio 1 Base 2 2 Sistema de Numeração • • A maneira utilizada para representar qualquer valor com um número limitado de símbolos foi o da agrupagem. Se montarmos grupos contendo como quantidade de elementos a mesma quantidade de símbolos que temos para a representação numérica, isto é, a base do número, a quantidade de objetos que ficar sobrando será inferior a base, sendo então possível a sua representação. 3 Sistema de Numeração • Vamos entender graficamente como é feita esta representação. • Vamos fazer um exemplo na base 10, que é a nossa base diária. (4 3 ) 10 4 Sistema de Numeração • Agora vamos fazer um exemplo na base 3 com as mesmas 43 bolinhas. (1 1 2 1 ) 3 4’ 3 3 1 3 14 1 2 3 2 1 3 4 1 3 1 0 (1 1 2 1 ) 3 = 1 x 3 x 3 x 3 +1 x 3 x 3 +2 x 3 +1 = 3 2 1 0 1 x3 + 1 x3 + 2 x3 + 1 x 3 = 27 + 9 + 6 = ( 43 ) 10 + 1 5 Sistema de Numeração • • Como será a representação no caso de bases superiores a base 10? Neste caso, precisaremos de mais símbolos para representar estes novos valores. Para facilitar, utilizou-se o alfabeto. 0 Vazio 1 2 3 4 5 6 7 8 9 A B C D E F Base 16 6 Sistema de Numeração • Exemplo de conversão de bases superiores a base 10. (7126)10 ( )16 7126 16 72 445 16 86 125 27 6 13 11 (1BD6)16 ( 3 2 1 16 1 (1BD6) 16 )10 0 (1 B D 6 ) 16 3 2 1 0 = 1 x 16 + 11 x 16 + 13 x 16 + 6 x 16 = 4096 + 2816 + 208 + 6 = ( 7126) 10 7 Sistema de Numeração Conversão de bases que são potências entre si. • • • • • • • • • • O que significa dizer que duas bases são potências entre si? Primeiramente devemos representar a base maior numa potência da base menor. (B be) onde B > b & e número inteiro maior que 1. Se for possível escrever as potências acima, então as bases são potências entre si. O próximo passo é montar uma tabela de conversão entre estas bases. Esta tabela terá uma quantidade de linhas de conversão igual ao valor da maior base (B). Normalmente coloca-se uma linha adicional para o cabeçalho das colunas. A quantidade de dígitos referente aos valores da menor base deve ser igual ao expoente usado nesta base (e). Monta-se uma tabela de duas colunas onde cada coluna representará uma base. Na coluna da base maior (B) coloca-se, em seqüência e começando do zero, todos os seus símbolos. Na coluna da base menor, coloca-se o valor equivalente escrito com uma quantidade de dígitos igual ao expoente da base menor (e). Pronto! Já temos a tabela pronta, agora é só usar. 8 Sistema de Numeração Conversão de bases que são potências entre si. • Exemplo: Montar a tabela que converta da base 2 para a base 4. Resolução: Base 4 base 2 (4 = 22 são potências entre si) Total de linhas da tabela: 4 Total de dígitos da base 2: 2 Base 4 0 1 2 3 Base 2 00 01 10 11 Exemplo: a) (323121302)4 ( )2 (3 2 3 1 2 1 3 0 2)4 = (111011011001110010)2 11 1011011001110010 b) (111101011110101010110)2 ( )4 (0111101011110101010110)2 = (13223311112)4 1 3 2 2 3 3 1 1 1 1 2 9 Sistema de Numeração Conversão de bases que são potências entre si. • Exemplo: Montar a tabela que converta da base 2 para a base 8. Resolução: Base 8 base 2 (8 = 23 são potências entre si) Total de linhas da tabela: 8 Total de dígitos da base 2: 3 Exemplo: Base 8 Base 2 0 1 2 3 4 5 6 7 000 001 010 011 100 101 110 111 a) (637254)8 ( )2 (6 3 7 2 5 4)8 = (110011111010101100)2 110 011 111 010 101 100 b) (111101011110101010110)2 ( )8 (111101011110101010110)2 = (7536526)8 7 5 3 6 5 2 6 10 Sistema de Numeração Conversão de bases que são potências entre si. • Exemplo: Montar a tabela que converta da base 2 para a base 16. Resolução: Base 16 base 2 (16 = 24 são potências entre si) Total de linhas da tabela: 16 Total de dígitos da base 2: 4 Exemplo: a) (AD3B9)16 ( )2 (A D 3 B 9)16 = (10101101001110111001)2 10101101001110111001 b) (111101011110101010110)2 ( )16 (000111101011110101010110)2 = (1EBD56)16 1 E 5 6 B D Base 16 Base 2 0 1 2 3 4 5 6 7 8 9 A B C D E F 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 11 Sistema de Numeração Representação de Números Negativos. • Os computadores digitais utilizam principalmente três métodos para representar números negativos: – Sinal e Magnitude – Complemento de um – Complemento de dois Para os três casos é importante definir a quantidade de bits usada na representação do número, porque o bit mais significativo (bit da esquerda) representará o sinal. 0 Positivo 1 Negativo 12 Sistema de Numeração Representação de Números Negativos. Sinal e Magnitude Esta representação agrupa o bit de sinal com um valor (magnitude) que representa o valor absoluto de número como ilustrado abaixo: Sinal Magnitude ... Número Faixa de Valores Para um número formado por n bits (incluindo o bit de sinal), é possível representar valores que vão deste -2n-1 + 1 até 2n-1 - 1. Exemplo: Para um número representado por 8 bits, isto é n = 8, teremos como faixa de valores: -28-1 + 1 até 28-1 - 1 -128 + 1 até 128 - 1 Faixa -127 até 127 13 Sistema de Numeração Representação de Números Negativos. Sinal e Magnitude Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. a) (-45)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 45, para binário. (45)10 = (101101)2. Segundo passo: Completar (à esquerda) com o valor zero os bits que faltam para chegar a n com exceção do bit mais à esquerda que deve representar o sinal. Neste caso o bit de sinal vale 1 pois o valor é negativo. (-45)10 = (10101101)2 = (AD)16. Bit de Sinal 14 Sistema de Numeração Representação de Números Negativos. Sinal e Magnitude Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. b) (-7)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 7, para binário. (7)10 = (111)2. Segundo passo: Completar (à esquerda) com o valor zero os bits que faltam para chegar a n com exceção do bit mais à esquerda que deve representar o sinal. Neste caso o bit de sinal vale 1 pois o valor é negativo. (-7)10 = (10000111)2 = (87)16. Bit de Sinal 15 Sistema de Numeração Representação de Números Negativos. Sinal e Magnitude Um ponto negativo em relação a esta representação é a existência de duas formas de representar o valor zero. Veja abaixo: Para um número com 8 bits, temos: (0)10 = (00000000)2. (-0)10 = (10000000)2. Como (0)10 = (-0)10 Então, (00000000)2 = (10000000)2. Isto é, duas representações do zero. 16 Sistema de Numeração Representação de Números Negativos. Complemento de 1 Nesta representação, o valor negativo de um número é dado pela inversão de todos os seus bits. O bit mais à esquerda continua representando o sinal, porém os demais bits não representam a magnitude. Sinal Demais bits ... Número Faixa de Valores Para um número formado por n bits (incluindo o bit de sinal), é possível representar valores que vão deste -2n-1 + 1 até 2n-1 - 1. Exemplo: Para um número representado por 8 bits, isto é n = 8, teremos como faixa de valores: -28-1 + 1 até 28-1 - 1 -128 + 1 até 128 - 1 Faixa -127 até 127 17 Sistema de Numeração Representação de Números Negativos. Complemento de 1 Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. a) (-45)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 45, para binário e representá-lo com 8 bits. (45)10 = (00101101)2. Segundo passo: Inverter todos os bits do número. Repare que o bit mais à esquerda continua representando o sinal. (-45)10 = (11010010)2 = (D2)16. Bit de Sinal 18 Sistema de Numeração Representação de Números Negativos. Complemento de 1 Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. b) (-7)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 7, para binário e representá-lo com 8 bits. (7)10 = (00000111)2. Segundo passo: Inverter todos os bits do número. Repare que o bit mais à esquerda continua representando o sinal. (-7)10 = (11111000)2 = (F8)16. Bit de Sinal 19 Sistema de Numeração Representação de Números Negativos. Complemento de 1 Um ponto negativo em relação a esta representação é a existência de duas formas de representar o valor zero. Veja abaixo: Para um número com 8 bits, temos: (0)10 = (00000000)2. (-0)10 = (11111111)2. Como (0)10 = (-0)10 Então, (00000000)2 = (11111111)2. Isto é, duas representações do zero. 20 Sistema de Numeração Representação de Números Negativos. Complemento de 2 Nesta representação, o valor negativo de um número é dado pela inversão de todos os seus bits mais 1. O bit mais à esquerda continua representando o sinal, porém os demais bits não representam a magnitude. Sinal Demais bits ... Número Faixa de Valores Para um número formado por n bits (incluindo o bit de sinal), é possível representar valores que vão deste -2n-1 até 2n-1 - 1. Exemplo: Para um número representado por 8 bits, isto é n = 8, teremos como faixa de valores: -28-1 até 28-1 - 1 -128 até 128 - 1 Faixa -128 até 127 21 Sistema de Numeração Representação de Números Negativos. Complemento de 2 Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. a) (-45)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 45, para binário e representá-lo com 8 bits. (45)10 = (00101101)2. Segundo passo: Inverter todos os bits do número (11010010)2. Terceiro passo: Somar 1 ao valor anterior. Repare que o bit mais à esquerda continua representando o sinal. (-45)10 = (11010011)2 = (D3)16. Bit de Sinal 22 Sistema de Numeração Representação de Números Negativos. Complemento de 2 Converta os valores abaixo para a sua representação em binário e em seguida apresente-os em hexadecimal (base 16). O valor de n representa a quantidade de bits utilizada na representação binária. a) (-7)10, n = 8 bits. Primeiro passo: Converter o valor sem sinal, 7, para binário e representá-lo com 8 bits. (7)10 = (00000111)2. Segundo passo: Inverter todos os bits do número. (11111000)2. Terceiro passo: Somar 1 ao valor anterior. Repare que o bit mais à esquerda continua representando o sinal. (-7)10 = (11111001)2 = (F9)16. Bit de Sinal 23 Sistema de Numeração Representação de Números Negativos. Complemento de 2 Diferente dos casos anteriores, esta representação possui apenas uma forma de representar o valor zero. Veja abaixo: Para um número com 8 bits, temos: (0)10 = (00000000)2. (-0)10 = (11111111)2 + 1 = (100000000)2. Como o número possui apenas 8 bits, o nono bit representado em azul deve ser descartado. (-0)10 = (00000000)2. Já que (0)10 = (-0)10 Então, (00000000)2 = (00000000)2. Isto é, apenas uma representações do zero. 24 Sistema de Numeração Aritmética com Complemento de 2. Como que a CPU faz para saber se o número utilizado é com ou sem sinal? Afinal de contas, isto é importante na hora de usar o número? Vamos supor os valores em binário abaixo representados por 8 bits. (10000100)2 e (00001110)2 Como seria feita a soma destes números? Usando o método tradicional fica: 11 10000100 + 00001110 10010010 Considerando sem sinal 10000100 (+132)10 + 00001110 (+14)10 10010010 (+146)10 Considerando com sinal 10000100 (-124)10 + 00001110 (+14)10 10010010 (-110)10 Olha só que interessante! A mesma conta serve tanto para números sem sinal, como para números com sinal. O que vai mudar é a interpretação do resultado feito pelo seu programa. 25 Memória • Tipos de Memória – Volátil São aquelas que necessitam de energia elétrica para manter os seus dados armazenados. – Não Volátil São aquelas que não necessitam de energia elétrica para manter os seus dados armazenados. 26 Memórias Voláteis • Estática (SRAM – “Static Random Access Memory”) – A característica mais relevante deste tipo de memória é no fato dela ter um tempo de resposta muito pequeno, sendo assim usada para caches e registradores, e também por ocupar um espaço muito grande nas pastilhas de silício proporcionando um alto custo por bit. • Dinâmica (DRAM – “Dynamic Random Access Memory”) – Esta memória ocupa um espaço muito pequeno da pastilha, levando a possibilidade de se produzir memórias com uma grande capacidade de armazenamento sendo utilizada para a memória principal, entretanto, ela possui um tempo de resposta muito alto, comparado com as SRAM. 27 Memórias Voláteis Volátil Vantagem 1- Alto desempenho Estática Desvantagens Dinâmica Vantagens Desvantagem 1- Alto consumo de energia elétrica 1- Baixo consumo de energia elétrica 1- Baixo desempenho 2- Alta geração de calor 2- Baixa geração de calor 2- Refresh 3- Baixo grau de integração 3- Alto grau de integração 4- Baixa capacidade de armazenamento 4- Alta capacidade de armazenamento 5- Alto custo por bit Exemplo de local onde é Utilizada Memória Cache, Registradores 5- Baixo custo por bit Exemplo de local onde é Utilizada Memória Principal 28 Memórias Não Voláteis • ROM (Read Only Memory) – Esta memória vem de fábrica com o seu conteúdo gravado, só sendo permitido ao usuário a operação de leitura (consulta dos dados). Devido ao alto custo da matriz de fabricação desta memória, a sua confecção só se torna financeiramente viável se for produzida em alta quantidade. • PROM (Programmable Read Only Memory) – Esta memória vem de fábrica com todos os seu bits valendo “1”, sendo permitido ao usuário a gravação dos “0”. Uma vez que o valor “0” é gravado em um determinado bit, não é possível restaurar este bit para o valor “1”, sendo assim, dizemos que esta memória permite apenas uma gravação por bit. 29 Memórias Não Voláteis • EPROM (Erasable Programmable Read Only Memory) – Esta memória vem de fábrica com todos os seu bits valendo “1”, sendo permitido ao usuário a gravação dos “0” através da energia elétrica. Nesta memória é possível restaurar o valor “1” do bit, mas para isso deve-se expor a memória a luz ultra-violeta. Como a luz ultravioleta será incidida em toda a memória, todos os bits de valor “0” serão retornados ao valor “1” original de fábrica. • EEPROM ou E2PROM (Electrically Erasable Programmable Read Only Memory) – Esta memória vem de fábrica com todos os seu bits valendo “1”, sendo permitido ao usuário a gravação dos “0” através da energia elétrica. Nesta memória é possível restaurar o valor “1” do bit também com o uso da energia elétrica, neste caso, não existe a necessidade de apagar toda a memória antes de ser regravada. 30 Memórias Não Voláteis • FLASH – É um tipo de E2PROM, onde a sua tecnologia permite uma maior densidade de bits uma maior taxa de transferência dos dados e menor tempo de gravação. BIOS (Basic Input Output System – Sistema Básico de Entrada e Saída) – Este é um programa que é executado assim que o computador é ligado. Ele tem por objetivo configurar o hardware existente e fazer as devidas verificações. Após toda a sua execução, ele solicita o carregamento do Sistema Operacional de alguma mídia. Devida a necessidade deste programa estar presente no momento em que a máquina é ligada, ele é armazenado em uma memória do tipo não volátil. Durante muitos anos foi utilizada a EPROM como meio de armazenamento da BIOS, mas hoje em dia usa-se a memória do tipo FLASH. 31 Estrutura Interna da Memória Principal M.P. 0 1 Identificação ou Endereço 2 3 N-1 Bit Célula Célula Unidade Mínima de Trabalho da M.P. N Total de Células da M.P. M Capacidade da Célula. CAP_MP Capacidade da M.P. CAP_MP = N x M E Total de bits do Endereço. 2E Total de Endereços. N – 1 Endereço da Última Célula. Se o Total de Células = Total de Endereços então { N = 2E Maior Endereço = N – 1 } 32 Conexão da CPU com a MP CPU MP. 0 Unidades Funcionais 1 2 3 REM RDM UC N-1 Barramento de Controle (BC) Barramento de Dados (BD) Barramento de Endereço (BE) REM Registrador de Endereço de Memória. RDM Registrador de Dados de Memória. UC Unidade de Controle. REM >= BE >= E RDM = BD >= M 33 Memórias Dinâmicas • • • • • • WE Write Enable (Ativado em “0”). RAS Row Address Strobe (Ativado em “0”, 11 bits mais significativos). CAS Column Address Strobe (Ativado em “0”, 11 bits menos significativos). A0 ... A21 Bits de Endereço (22 bits neste exemplo). D Entrada do bit de dados. Q Saída do bit de dados. Obs: em algumas memórias, os pinos D e Q são curtocicuitados gerando um único pino bidirecional. 34 Memórias Dinâmicas • Diagrama em blocos simplificado de uma memória DRAM de 4 Mbits. 35 Memórias Dinâmicas • • • • • • As memórias dinâmicas são formadas por minúsculos capacitores que, quando carregados, armazenam o valor “1” e, quando descarregados, armazenam o valor “0”. Estes capacitores formam matrizes que são endereçadas pelos bits de linha e coluna que juntos formam o endereço da célula. Devida a corrente de fuga existente em todo circuito eletrônico, estes capacitores precisam ser periodicamente recarregados para que o dado por ele armazenado não seja perdido. A este procedimento dá-se o nome de “Refresh”. O Refresh é feito por linha, isto é, uma linha é selecionada e todas as suas colunas são recarregadas simultaneamente É comum estruturar uma matriz retangular onde existem mais colunas do que linhas, para que o tempo gasto no Refresh seja reduzido. Quando é feita a leitura de um bit, o capacitor responsável por seu armazenamento perde parte da carga armazenada, sendo necessário um recarregamento logo após a leitura ser feita. Este procedimento é feito pelo circuito de Pré-Carga, que, infelizmente, contribui com a queda no desempenho, pois este tempo é incluído no tempo das operações de leitura. 36 Memórias Dinâmicas (sinalização de RAS) • • • • Nesta figura vemos como funciona a sinalização dos bits de linha. Inicialmente o sinal de RAS deve estar desabilitado (“1”) para que sejam colocados os bits referentes a linha (ROW). Como para a memória só existem 11 bits, estes são colocados nos pinos (A0 – A10). Após a estabilidade dos bits de linha, o sinal de RAS é habilitado (“0”). Neste momento, o decodificador de linha é acionado e memoriza o endereço da linha. 37 Memórias Dinâmicas (sinalização de CAS) • • • • • Nesta figura vemos como funciona a sinalização dos bits de coluna. Após a sinalização do sinal de RAS, este deve permanecer habilitado (“0”) durante todo o procedimento. O sinal de CAS deve estar inicialmente desabilitado (“1”). Após a captura dos bits de linha, são disponibilizados os bits de coluna (Column). Como para a memória só existem 11 bits, estes são colocados nos pinos (A0 – A10). Após a estabilidade dos bits de coluna, o sinal de CAS é habilitado (“0”). Neste momento, o decodificador de coluna é acionado e memoriza o endereço da linha. 38 Memórias Dinâmicas (leitura de um dado) • • • • Nesta figura vemos como funciona a leitura de um dado. Após a sinalização do sinal de CAS, automaticamente é habilitado o buffer de saída (Q). Apesar do buffer de saída estar habilitado, o dado só estará presente na saída após um certo tempo, no exemplo acima, 60ns após a sinalização de RAS. Só apos este tempo, o dado estará disponível no barramento. 39 Memórias Dinâmicas (leitura de um dado) • • • • Nesta figura vemos o procedimento de leitura completo de um dado. Na finalização do procedimento de leitura, o sinal de CAS e RAS devem ser desabilitados em seqüência. Após desabilitar o sinal de RAS, é necessário permanecer um período de tempo neste estado até começar um novo procedimento de leitura, ou escrita. É neste período de tempo que é realizada a pré-carga do dado lido. 40 Memórias Dinâmicas (escrita de um dado) • • Nesta figura vemos o procedimento de escrita completo de um dado. O detalha a adicionar é que neste procedimento, o pino WE deve ser habilitado (“0”) para que seja feita uma escrita. 41 Memórias Dinâmicas (escrita de um dado) • • • • • • O pino WE é habilitado após a sinalização de RAS e antes da sinalização de CAS. Desta forma, a memória sabe antecipadamente que será realizada uma operação de escrita, mantendo o pino de saída desabilitado. Isto possibilita que os dois pinos (Q e D) sejam curtocircuitados. Este método é conhecido como “early-write” (escrita antecipada), já que a escrita é sinalizada antes da finalização do endereço. Também existe o método “delayed-write” (escrita atrasada), onde a sinalização de escrita é feita após o sinal de CAS. Neste caso, não é possível curtocircuitar os pinos (D e Q), pois o pino Q será habilitado juntamente com o pino D, gerando problemas elétricos. A figura a seguir mostra esta situação. 42 Memórias Dinâmicas (escrita de um dado) Nesta figura vemos o procedimento de escrita atrasada. 43 Memórias Dinâmicas (FPM RAM – Fast Page Mode RAM) • • • Como a maioria dos acessos aos dados é feita em seqüência é bem provável que o próximo acesso ocorra na mesma linha, com exceção das bordas. Neste tipo de memória, otimiza-se o acesso, indicando a linha apenas uma vez e depois indicam-se as colunas a serem acessadas. O controle do buffer de saída continua sendo acionado pela linha CAS. 44 Memórias Dinâmicas (EDO RAM – Extended Data Output RAM) • • • Funciona de forma semelhante a FPM RAM, mas nesta memória foi acrescentado um “latch” para ser usado na saída do dado. Desta forma, o sinal de CAS não precisa ser utilizado para habilitar a saída, deixando esta tarefa para o controlador da DRAM. A vantagem é que com a liberação do CAS, pode-se enviar uma nova coluna em um período de tempo menor. 45 Memórias Dinâmicas (BEDO RAM – Burst Extended Data Output RAM) • • Funciona de forma semelhante a EDO RAM, mas nesta memória foi acrescentado um contador para os n bits menos significativos da coluna. Desta forma, para acessos seqüenciais, não era preciso enviar os bits de todas as colunas acessadas. Este contador se auto incrementava a cada acesso, permitindo um acesso em rajada de até 2n colunas. 46 Memórias Dinâmicas (BEDO RAM – Burst Extended Data Output RAM) • • • Após o envio do endereço da primeira coluna, o sinal de CAS é utilizado para acionar a leitura da próxima coluna. Como não havia necessidade de enviar o endereço da coluna, o tempo de CAS era bem menor, aumentando a taxa de transferência durante a rajada. No exemplo abaixo, foi utilizado um contador de 2 bits, permitindo uma rajada de apenas 4 colunas. Após a quarta coluna, deve-se enviar na integra uma nova coluna e então recomeçar a rajada. 47 Memórias Dinâmicas (SDRAM – Synchronous Dynamic RAM) • • • Esta memória passou a ser sincronizada por um clock (Relógio) externo. Este clock externo é conhecido como clock de barramento. A vantagem é que a maioria dos sinais de controle são enviados no primeiro acesso e todos os demais acessos da mesma linha são gerados internamente, aumentando o desempenho. 48 Memórias Dinâmicas (SDRAM – Synchronous Dynamic RAM) • • • Estas memórias passaram a ter o seu sinalizador de desempenho como sendo a freqüência deste clock. Para as memórias de clock igual a 100 MHz, eram denominadas PC100, as de clock igual a 133 MHz, PC133. Em um barramento de 32 bits (4 bytes), a taxa de transferência da memória PC100 é de 400 MB/s e a PC133 é de 532 MB/s. 49 Memórias Dinâmicas (Empacotamento de Memória) • • • • • • • As memórias costumam vir empacotadas em dois tipos de módulos (SIMM e DIMM). Módulo SIMM (Single In Line Memory Module – Módulo de Memória em Linha Única). Módulo DIMM (Dual In Line memory Module – Módulo de Memória em Linha Dupla). Estes termos dizem respeito apenas ao empacotamento das memórias dinâmicas. É possível usar qualquer um dos dois tipos. Houve uma tendência no uso do módulo DIMM no empacotamento das memórias dinâmicas. Os módulos SIMM possuíam 30 ou 72 pinos Os módulos DIMM possuíam 168 pinos 50 Memórias Dinâmicas (Módulo SIMM) • Os módulos de 30 pinos possuem barramento de dados de 8 bits (9 bits contando a paridade). • São necessários 4 SIMM de 30 pinos para formar um barramento de 32 bits (caso das CPUs 486). • Os módulos de 72 pinos, possuem barramento de dados de 32 bits (36 bits contando a paridade). • Basta apenas 1 módulo para atender um barramento de 32 bits (caso das CPUs 486). • Para o caso dos Pentium que possuem barramento de 64 bits, eram necessários 2 módulos SIMM de 72 pinos. 51 Memórias Dinâmicas (Módulo SIMM) • Abaixo temos um exemplo de encapsulamento SIMM. 52 Memórias Dinâmicas (Módulo DIMM) • • • Motivados pelas máquinas Pentium com barramento de 64 bits, surgiram os módulos DIMM com 168 pinos. Estes módulos ofereciam barramento de dados de 64 bits sem contar com os bits de paridade). Abaixo temos um exemplo de encapsulamento DIMM. 53 Memórias Dinâmicas (Módulo DDR) • • • Até este momento, a taxa externa de comunicação da CPU (Pentium III) era de 1.064 MB/s. Esta taxa de comunicação estavam sendo satisfeitas pelas memórias de DIMM de 133 MHz (PC133). Como elas possuíam 8 bytes de barramento de dados, a sua taxa máxima era de 133 x 8 = 1.064 MB/s. Com o lançamento do Pentium 4 e o Athlon, este equilíbrio na taxa de transferência foi quebrado. Estes processadores tinham a capacidade de se comunicar a uma taxa maior, mas as memórias estavam ainda no clock de 133 MHz. Devido a isso, foi lançada a memória DDR (Double Data Rating). 54 Memórias Dinâmicas (Módulo DDR) • • • • • Os módulos DDR possuíam 184 pinos. A grande diferença esta na taxa de transferência dos dados. Nesta memória, é feita a transferência de dois dados a cada ciclo de clock. Um dado é transferido na transição de subida do clock e outro é transferido na transição de descida. Com isso, consegue-se o dobro da taxa de transferência com a mesma freqüência de clock. Estas memórias já vinham com a indicação do clock dobrada, porém o clock real era a metade do valor. Exemplo: – A memória DDR-200 trabalha a 100 MHz de clock e possui uma taxa de 1.600 MB/s; – A memória DDR-400 trabalha a 200 MHz de clock e possui uma taxa de 3.200 MB/s. 55 Memórias Dinâmicas (Tecnologia Dual DDR) • • • • • • A taxa de transferência ainda era considerada baixa para as CPUs, então foi criada a tecnologia Dual Channel DDR, ou DDR de Canal Duplo. Estas são memórias DDR que trabalham em dupla para aumentar a largura de banda na transmissão. Cada módulo DDR possui um barramento de dados de 64 bits. Ao juntar dois módulos DDR, o barramento aumenta para 128 bits. Para isso, são necessários dois controladores de memória para que sejam feitos acessos simultâneos a dois módulos DDR. É importante lembrar que a mudança foi na placa mãe e não na memória em si. Com esta tecnologia, uma memória DDR 800 trabalharia com o dobro da taxa, isto é 12.800 MB/s contra os 6.400 MB/s sem o Dual Channel. 56 Memórias Dinâmicas (Tecnologia Dual DDR) • Abaixo temos a ilustração de um sistema DDR de canal simples. 57 Memórias Dinâmicas (Tecnologia Dual DDR) • Abaixo temos a ilustração de um sistema DDR de canal duplo. 58 Memórias Dinâmicas (Tecnologia Dual DDR) • • Placas mãe com a tecnologia dual channel possuem indicações especiais nos slots de memória para que os pentes sejam encaixados corretamente e então habilitar a transmissão de canal duplo. A figura a seguir mostra um exemplo de placa mãe dual channel. Vale ressaltar que cada fabricante tem um modo diferente de especificar os canais, sendo importante a leitura do manual da respectiva placa mãe. 59 Memórias Dinâmicas (Tecnologia Dual DDR) 60 Memórias Dinâmicas (Tecnologia DDR) DDR Nome padrão DDR-200 DDR-266 DDR-300 DDR-333 DDR-400 Clock dos chips 100 MHz 133 MHz 150 MHz 166 MHz 200 MHz Ciclo de tempo 10 ns 7.5 ns 6.67 ns 6 ns 5 ns Clock real 100 MHz 133 MHz 150 MHz 166 MHz 200 MHz Dados por Nome do Taxa de segundo módulo transferência 200 Milhões PC-1600 1600 MB/s 266 Milhões PC-2100 2100 MB/s 300 Milhões PC-2400 2400 MB/s 333 Milhões PC-2700 2700 MB/s 400 Milhões PC-3200 3200 MB/s 61 Memórias Dinâmicas (Tecnologia DDR2) DDR2 DDR2-400 Clock dos chips 100 MHz Ciclo de tempo 10 ns 200 MHz Dados por segundos 400 Milhões DDR2-533 133 MHz 7.5 ns 266 MHz 533 Milhões DDR2-667 166 MHz 6 ns 333 MHz 667 Milhões DDR2-800 200 MHz 5 ns 400 MHz 800 Milhões DDR2-1066 266 MHz 3.75 ns 533 MHz 1066 Milhões DDR2-1300 325 MHz 3.1 ns 650 MHz 1300 Milhões Nome padrão Clock real Nome do módulo PC2-3200 PC2-4200 PC2-4300 PC2-5300 PC2-5400 PC2-6400 PC2-8500 PC2-8600 PC2-10400 Taxa de transferência 3200 MB/s 4266 MB/s 5333 MB/s 6400 MB/s 8533 MB/s 10400 MB/s 62 Memórias Dinâmicas (Tecnologia DDR3) DDR3 Nome padrão Clock real Dados por segundos DDR3-1600 800 MHz 1600 Milhões DDR3-2666 1333 MHz 2666 Milhões DDR3-3200 1600 MHz 3200 Milhões Taxa de transferência 12800 MB/s 21328 MB/s 25600 MB/s 63 Memórias Cache • • • • A Memória Cache foi criada devida a grande diferença de velocidade entre a CPU e a Memória Principal. Para conseguir um melhor desempenho, foi utilizada a tecnologia Estática na fabricação da Memória Cache. Ela foi introduzida entre a CPU e a Memória Principal com o objetivo de, caso possuísse o dado, respondesse mais rapidamente a solicitação da CPU. Abaixo temos um esquema de comunicação de memória com a Memória Cache. 64 Memórias Cache • • O funcionamento da Memória Cache baseia-se totalmente nos conceitos de Localidade Temporal e Localidade Espacial. Estes conceitos estão relacionados ao comportamento dos softwares. – Localidade Temporal: uma vez acessada uma determinada região de memória, existe uma grande probabilidade desta região ser novamente acessada em um curto espaço de tempo. – Localidade Espacial: uma vez acessada uma determinada região de memória, existe uma grande probabilidade de serem acessadas as regiões que estão na sua vizinhança. Com base nestes dois conceitos, a Memória Cache passou a ter uma alta taxa de acertos (Hits) contra as taxas de faltas (Misses), já que na maioria das Memórias Caches o seu carregamento é feito sob demanda. 65 Memórias Cache • A Memória Cache se divide em três características principais que se subdividem em outras, como mostra o esquema abaixo: – Políticas de Carregamento: • Mapeamento Direto • Puramente Associativo • Associativo por Conjunto – Políticas de Substituição: • Aleatório • FIFO (First In First Out) • LFU (Least Frequently Used - Menos Freqüentemente Usado) • LRU (Least Recently Used - Menos Recentemente Usado) – Políticas de Atualização: • Write Through (Escrita em Ambas) • Write Back (Escrita Atrasada) • Write Once (Utilizada na existência de mais de uma CPU) 66 Memórias Cache • • • • A Política de Carregamento estabelece o local interno da Memória Cache que os dados serão carregados. A Política de Substituição define qual região da Memória Cache terá seus dados substituídos por outros vindos da Memória Principal. A Política de Atualização define o momento que os dados escritos pela CPU serão repassados a Memória Principal. A figura a seguir mostra o formato da Memória Cache. – O bit V (Válido) indica se o conteúdo da linha é válido ou não. – O bit M (Modificado) indica se a linha sofreu alguma alteração por parte da CPU. – A TAG indica de que lugar da memória principal pertence o dado carregado na linha. – Blocos são um conjunto de células consecutivas com capacidade para preencher uma linha da Memória Cache. 67 Memórias Cache • Abaixo temos o formato da Memória Cache 68 Memórias Cache Mapeamento Direto 69 Memórias Cache Mapeamento Direto • • • • • • Nesta Memória temos os blocos sendo mapeados seqüencialmente nas linhas da Memória Cache. Quando um bloco é mapeado na última linha da Cache, o bloco seguinte volta a ser mapeado na sua primeira linha. Neste ponto é finalizado um ciclo e inicializado outro. A característica mais importante de um ciclo é que não existe conflito de linhas da Cache entre os blocos do mesmo ciclo. Para que haja conflito de linhas, os blocos acessados deverão estar em ciclos diferentes e separados por uma distância mínima equivalente a uma Cache inteira. Devido ao conceito de Localidade Espacial, esta situação é pouco provável. 70 Memórias Cache Mapeamento Direto • • • • A TAG desta memória guarda o número do ciclo de onde o dado se originou. Para trabalhar internamente, a Memória Cache precisa do valor da TAG, do Número da Linha e do Número da Coluna para localizar o dado solicitado. O pedido do dado se origina na CPU. Esta solicitação é feita pelo endereço da célula da Memória Principal. Este endereço é visto pela Cache como sendo composto pelas informações (TAG, Número da Linha, Número da Coluna), como mostra a figura abaixo: 71 Memórias Cache Puramente Associativa 72 Memórias Cache Puramente Associativa • • • • Nesta Memória os blocos podem ser carregados em qualquer linha da Cache, ao contrário do Mapeamento Direto, onde as linhas já eram pré-definidas e não podiam ser mudadas. A TAG neste caso guarda o número do bloco, já que não existe a definição de ciclo nesta memória. Devida a possibilidade do bloco ser carregado em qualquer linha, existe a necessidade de verificar todas as linhas da Cache para saber se o dado se encontra ou não. Esta necessidade torna a implementação desta Cache mais difícil e pouco escalável, já que o aumento no número de linhas implica em mais circuitos de verificação de dados. 73 Memórias Cache Puramente Associativa • • Nesta memória, o número da linha não se originará do endereço da Memória Principal, e sim de um circuito interno de verificação. O endereço da Memória Principal é visto pela Cache como sendo composto pelas informações (TAG, Número da Coluna), como mostra a figura abaixo: 74 Memórias Cache Associativa por Conjunto 75 Memórias Cache Associativa por Conjunto • • • • • Nesta Memória as linhas são agrupadas formando conjuntos. Os blocos são mapeados para os conjuntos de forma semelhante ao Mapeamento Direto, só que ao invés de ser mapeado para linha ele é mapeado para o conjunto. Dentro do conjunto o bloco pode ser carregado em qualquer uma de suas linhas, semelhante a Puramente Associativa, sendo que esta liberdade está restrita ao conjunto. A TAG neste caso guarda o número do ciclo, já que, devido ao mapeamento dos conjuntos, volta a existir a definição de ciclo. Devida a possibilidade do bloco ser carregado em qualquer linha do conjunto, existe a necessidade de verificar todas as suas linhas para saber se o dado se encontra ou não. Como esta necessidade está limitada ao conjunto, a implementação desta Memória Cache ficou mais fácil e escalável, já que o aumento no número de linhas da Cache não implica em mais circuitos de verificação de dados, pois não aumenta o número de linhas do conjunto. 76 Memórias Cache Associativa por Conjunto • • • Nesta memória, o número da linha não se originará do endereço da Memória Principal, e sim o número do conjunto. A linha dentro do conjunto se originará de um circuito interno de verificação. O endereço da Memória Principal é visto pela Cache como sendo composto pelas informações (TAG, Número do Conjunto, Número da Coluna), como mostra a figura abaixo: 77 Memórias Cache Políticas de Substituição • • A Política de Substituição tem como finalidade definir uma linha para ter seus dados substituídos por um novo conteúdo vindo da Memória Principal. Esta linha é denominada “Linha Vítima”. – Aleatório: Este método faz uma escolha casual de uma linha para ser a linha vítima. Como este método não leva em consideração os acessos anteriores à Memória Cache, existirá uma grande chance de se fazer uma má escolha. – FIFO: Este método faz a escolha da linha vítima de acordo com a ordem de carregamento (First-in, First-out). O método de escolha é simples e é levado em consideração a ordem de carregamento, que só é atualizado quando a linha for carregada, isto é, na ocorrência de um miss. – LFU (Menos Freqüentemente Usada): Este método usa como base para a escolha da linha vítima a quantidade de vezes que as linhas foram referenciadas. A linha que foi referenciada menos vezes, é a linha vítima. Este método usa como critério a freqüência de acessos a uma determinada linha. – LRU (Menos Recentemente Usada): O critério de escolha deste método é a ordem dos acessos feitos às linhas de cache. A linha que não é acessada a mais tempo é a candidata a linha vítima. 78 Memórias Cache Políticas de Atualização • A Política de Atualização faz referência ao momento em que o dado escrito pela CPU será transferido para a Memória Principal. – Write Through: Este método faz a atualização da Memória Principal no momento em que foi feita a escrita na Memória Cache. A vantagem deste método é de manter a Memória Principal sempre atualizada, só que para cada escrita feita pela CPU, será consumido o tempo referente ao da Memória Principal. A vantagem da cache será apenas nas operações de leitura que, por serem muito mais freqüentes, ainda terá algum ganho com este método. – Write Back: Para conseguir aumentar o desempenho nas operações de escrita, esta memória atrasa as atualizações na Memória Principal, mantendo os dados mais recentes apenas na Cache. A atualização será realizada somente no momento em que a respectiva linha tiver que ser substituída por outra, a não ser que ela não tenha sido alterada pela CPU. 79 Memórias Cache Políticas de Atualização – Write Once: Esta política de atualização é uma mistura dos dois métodos anteriores e tem como objetivo trazer vantagens tanto nas operações de leitura como nas operações de escrita em sistemas com mais de uma CPU. Este é um caso em que mais de um dispositivo está acessando a Memória Principal. Para que não aconteça o envio de uma informação errada para uma das CPUs, a Memória Cache utiliza do recurso da primeira escrita para avisar as demais caches do sistema que aquele bloco da Memória Principal passará a ser de uso exclusivo dela. A partir deste momento, todas as operações de escrita e leitura naquele bloco da Memória Principal ficarão restritos a esta cache. Quando alguma outra CPU necessitar das informações deste bloco, será feita uma solicitação de atualização à cache portadora do bloco. Esta cache irá então atualizar a Memória Principal possibilitando que as demais CPUs recebam o dado mais recente. 80 Memórias Cache Processador Athlon 64 Athlon 64 FX Cache L1 de Instruções 64 KB Associativo por conjunto de 2 vias 64 KB Associativo por conjunto de 2 vias 512 KB ou 1 MB Associativo por conjunto de 16 vias Linhas de 64 bytes Linhas de 64 bytes Linhas de 64 bytes Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com a unidade de busca Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L1 de dados Caminho de dados de 128 bits com o cache L1 de instruções 64 KB por núcleo 64 KB 1 MB por núcleo Associativo por conjunto de 2 vias Associativo por conjunto de 2 vias Associativo por conjunto de 16 vias Linhas de 64 bytes Linhas de 64 bytes Linhas de 64 bytes Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L1 de dados Caminho de dados de 128 bits com a unidade de busca Cache L1 de Dados Cache L2 Caminho de dados de 128 bits com o cache L1 de instruções 81 Memórias Cache Processador Athlon 64 X2 Cache L1 de Instruções 64 KB por núcleo Cache L1 de Dados 64 KB 512 KB ou 1 MB por núcleo Associativo por conjunto de 2 vias Associativo por conjunto de 2 vias Associativo por conjunto de 16 vias Linhas de 64 bytes Linhas de 64 bytes Linhas de 64 bytes Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L1 de dados Caminho de dados de 128 bits com a unidade de busca Sempron (soquetes 754 e AM2) Cache L2 Caminho de dados de 128 bits com o cache L1 de instruções 64 KB por núcleo 64 KB 128 KB ou 256 KB Associativo por conjunto de 2 vias Associativo por conjunto de 2 vias Associativo por conjunto de 16 vias Linhas de 64 bytes Linhas de 64 bytes Linhas de 64 bytes Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L1 de dados Caminho de dados de 128 bits com a unidade de busca Caminho de dados de 128 bits com o cache L1 de instruções 82 Memórias Cache Processador Opteron Cache L1 de Instruções 64 KB por núcleo Cache L1 de Dados 64 KB por núcleo 1 MB por núcleo Associativo por conjunto de 2 vias Associativo por conjunto de 2 vias Associativo por conjunto de 16 vias Linhas de 64 bytes Linhas de 64 bytes Linhas de 64 bytes Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L2 Caminho de dados de 128 bits com o cache L1 de dados Caminho de dados de 128 bits com a unidade de busca Pentium 4 N/D * Cache L2 Caminho de dados de 128 bits com o cache L1 de instruções 8 KB 256 KB, 512 MB ou 1 MB Associativo por conjunto de 4 vias Associativo por conjunto de 8 vias Linhas de 64 bytes Caminho de dados de 256 bits com o cache L2 Linhas de 128 bytes Caminho de dados de 64 bits com a unidade de busca Caminho de dados de 256 bits com o cache L1 de dados 83 Memórias Cache Processador Cache L1 de Instruções Pentium D N/D * Cache L1 de Dados Cache L2 16 KB 1 MB ou 2 MB por núcleo Associativo por conjunto de 4 vias Associativo por conjunto de 8 vias Linhas de 64 bytes Caminho de dados de 256 bits com o cache L2 Linhas de 128 bytes Caminho de dados de 64 bits com a unidade de busca Caminho de dados de 256 bits com o cache L1 de dados Core 2 Duo 32 KB 32 KB 2 MB ou 4 MB Linha de dados de 64 bytes Linha de dados de 64 bytes Associativo por conjunto de 8 vias Caminho de dados de 256 bits com a unidade de busca Caminho de dados de 256 bits com o cache L2 Linhas de 64 bytes Caminho de dados de 256 bits com o cache L1 de dados Pentium Dual Core 32 KB Linha de dados de 64 bytes Caminho de dados de 256 bits com a unidade de busca 32 KB Linha de dados de 64 bytes Caminho de dados de 256 bits com o cache L2 1 MB Associativo por conjunto de 8 vias Linhas de 64 bytes Caminho de dados de 256 bits com o cache L1 de dados 84 CPU Características Gerais • A CPU é um dispositivo eletrônico que tem a finalidade de executar operações previamente estabelecidas pelo seu fabricante (desenvolvedor). • Dentro da CPU existem diversos circuitos específico para cada operação diferente definida pelo fabricante. • Estas operações são chamadas de instruções de máquina. • As instruções de máquina são muito simples e, para que seja possível realizar uma tarefa mais complexa, deve-se executar uma determinada seqüência destas instruções. • Esta seqüência de instruções são os programas. 85 CPU Características Gerais • O que é necessário para a execução do programa? 1. As instruções a serem executadas devem estar armazenadas em células sucessivas da Memória Principal; 2. O endereço da primeira instrução deve estar armazenado no processador para que ele possa começar a execução. • Após estabelecidos os passos anteriores, o processador realizará ciclicamente os passos a seguir: a) Buscar uma instrução na Memória Principal, uma de cada vez, cujo endereço deve estar armazenado em um registrador existente na CPU específico para este fim; b) Interpretar que operação representa aquela instrução; c) Buscar os dados, onde estiverem, para trazê-los até o processador; d) Executar efetivamente a operação com os dados; e) Guardar o resultado, se houver algum, no local definido pela instrução; f) Reiniciar o procedimento buscando uma nova instrução. Este procedimento cíclico é chamado de “Ciclo de Instrução”. 86 CPU Características Gerais • • • • Este ciclo é realizado indefinidamente desde o momento em que a máquina foi ligada até o momento em que ela é desligada, reiniciada (resete), que ocorra algum tipo de erro ou que seja encontrada uma instrução de parada. A execução do ciclo de instrução foi sofrendo diversos melhoramentos com o passar dos anos com o objetivo de agilizar a execução dos programas. Um dos melhoramentos foi a utilização de pipelines (linha de montagem). Com esta técnica foi possível diminuir a ociosidade das unidades funcionais permitindo que todas elas trabalhassem simultaneamente. Desta forma, enquanto se interpreta uma instrução, já esta sendo feita a busca da próxima. No pipeline temos vária instruções sendo executadas ao mesmo tempo, porém cada uma delas em estágios diferentes. Outra melhoria foi permitir a execução simultânea de várias instruções no mesmo estágio. Estas CPUs são chamadas de superescalares. 87 CPU Características Gerais • • • • • • • • Os registradores são memórias especiais que possuem acesso direto às unidades de processamento. Eles são produzidos com a mesma tecnologia de fabricação da CPU e com isso, possuem o mesmo desempenho. Como é uma memória, a sua única funcionalidade é de guardar valores para uma futura consulta. Os registradores podem ser classificados como de uso geral (de dados) ou de uso específico (informações de uso interno da CPU). Os registradores de uso geral são usados para armazenar dados da execução do programa, como os valores que serão operados e o resultado das operações. Os registradores de uso específico guardam informações especiais. Já vimos dois deles: RDM e REM. Existe também o registrador PC (Program Counter) ou CI (Contador de Instruções) ou IP (Instruction Pointer – nomenclatura da Intel e da AMD). Este registrador guarda o endereço da próxima instrução a ser executada pela CPU. Um outro importante registrador é o RI (Registrador de Instrução). Este registrador guarda a instrução que está sendo executada pela CPU. 88 CPU Formatos de uma Instrução de Máquina • • • • • • Como será que é formada a instrução de máquina? Devemos ter em mente que a CPU possui um circuito para cada tarefa definida pelo fabricante. Para acessar estes circuitos e então ter tal operação realizada, eles foram identificados com um código numérico. Sempre que se deseja executar uma determinada operação, deve-se indicar o código do circuito em questão. Este código é conhecido como opcode. Além de indicar a operação, a maioria delas necessita de parâmetros (operandos). Então, além do opcode, a instrução possui campos com os operandos da operação em questão. Nas arquiteturas mais comuns, as instruções podem ir desde apenas o opcode, zero operando, até três operandos. Operandos OPCODE OP. 1 OP. 2 OP. 3 89 CPU Modos de Endereçamentos • Indicar o endereço do dado diretamente na instrução muitas das vezes é insuficiente para algumas estruturas de dados. Sendo assim, existem outras formas de formar o endereço onde os dados ou instruções estão guardados. • Dentre os diversos modos de endereçamentos desenvolvidos para processadores, os principais são: – Imediato; – Direto; – Indireto; – Por registrador; – Indexado; – Base mais deslocamento. • Nem todos estes modos estão incluídos nos conjuntos de instruções dos processadores contemporâneos, mas devem ser descritos não só por razões históricas mas para percepção do processo evolutivo da tecnologia. 90 CPU Modos de Endereçamentos • • • • Modo Imediato O método mais simples e rápido de obter um dado é indicar seu próprio valor no campo operando da instrução, em vez de buscá-lo na memória. A vantagem desse método reside no curto tempo de execução da instrução, pois não gasta ciclo de memória para a sua execução, exceto o único requerido para a sua busca. Assim, o dado é transferido da memória juntamente com a instrução (para o RI), visto estar contido no campo operando da instrução. Este modo é útil: – Para inicialização de contadores (um valor sempre fixo em toda execução do mesmo programa); – Na operação com constantes matemáticas; – Para armazenamento de ponteiros em registradores do processador; – Para indicação da quantidade de posições em que um determinado número será deslocado para a direita ou para a esquerda (em operações de divisão e multiplicação por 2). Uma de suas desvantagens consiste na limitação do tamanho do campo operando das instruções o que reduz o valor máximo do dado a ser manipulado. 91 CPU Modos de Endereçamentos • • • • • Modo Direto Nesse método, o valor binário contido no campo operando da instrução indica o endereço de memória onde se localiza o dado. O endereço pode ser o de uma célula onde o dado está inteiramente contido. É também um modo simples de acesso, pois requer apenas uma referência à MP para buscar o dado, sendo, porém mais lento que o modo imediato devido naturalmente à referência à memória. Quando um dado varia de valor a cada execução do programa, a melhor maneira de utilizá-lo é, inicialmente, armazená-lo na MP (do dispositivo de entrada para a memória). O programa, então, usa o dado através do modo direto, onde a instrução indica apenas o endereço onde ele se localiza. Esta é a característica de uma variável de programa: representar o endereço de uma variável. Uma possível desvantagem desse processo está na limitação da memória a ser usada, conforme o tamanho do campo operando. Isto é, se o campo tiver um tamanho, por exemplo, de 12 bits, com o emprego do modo direto somente se pode acessar as células de endereço na faixa de 0 a (4.095)10. 92 CPU Modos de Endereçamentos • • • • Modo Indireto Nesse método, o valor binário contido no campo operando da instrução representa o endereço de uma célula; mas o conteúdo da referida célula não é o valor de um dado (como no modo direto), é um outro endereço de memória, cujo o conteúdo é o valor do dado. Assim, há um duplo endereçamento para o acesso a um dado e, conseqüentemente, mais ciclos de memória para buscar o dado, comparativamente com os métodos já apresentados. O endereço intermediário (conteúdo da célula endereçado pelo valor do campo operando) é conhecido como ponteiro, pois indica a localização do dado. Com esse processo, elimina-se o problema do modo direto, delimitação do valor do endereço do dado, pois estando o endereço armazenado na memória (pode ocupar uma ou mais células) se estenderá ao tamanho necessário à representação do maior endereço da MP, do sistema de computação em uso. 93 CPU Modos de Endereçamentos • • • • Endereçamento por Registrador Esse método tem característica semelhante aos modos direto e indireto, exceto que a célula (ou palavra) de memória referenciada na instrução é substituída por um dos registradores do processador. Com isso, o endereço mencionado na instrução passa a ser o de um dos registradores, e não mais de uma célula da MP. A primeira vantagem, logo observada, consiste no menor número de bits necessários para endereçar os registradores, visto que estes existem em muito menor quantidade que as células de memória. Isso reduz o tamanho geral da instrução. Um computador que tenha, por exemplo, um processador com 16 registradores, requer apenas 4 bits para endereçá-los; no caso de endereçamentos de células da MP, como o espaço de endereçamento da memória é grande, há necessidade de 20 ou mais bits para indicar o endereço de cada uma das células. Outra vantagem está no próprio emprego do dado, que passa a ser armazenado em um meio (registrador) cujo acesso é muito mais rápido que o acesso à memória. 94 CPU Modos de Endereçamentos Modo Indexado • • • • • Freqüentemente, durante a execução dos programas há necessidade de se manipular endereços de acesso a elementos de certos tipos especiais de dados. Esses endereços servem, na realidade, de ponteiros para os referidos elementos. Por exemplo, o acesso aos elementos de um vetor deve considerar que tais elementos são armazenados seqüencialmente na memória e que sua localização pode ser referenciada por um ponteiro (endereço) que é alterado para indicar o elemento desejado (índice do elemento identifica univocamente cada um). A descrição dessas instruções caracterizam o modo de endereçamento denominado indexado. Esta denominação advém do fato de que a obtenção do endereço de um dado (elemento de um array) relaciona-se com o seu índice. Nesse tipo de instrução, o endereço do dado é a soma do valor do campo operando (fixo para todos os elementos de um dado array) e de um valor armazenado em um dos registradores (normalmente denominado registrador índice). O valor armazenado nesse registrador varia para o acesso a cada elemento. Na verdade, esse modo de endereçamento é uma evolução das técnicas desenvolvidos desde os primórdios da computação para manipulação dessas estruturas de dados especiais. 95 CPU Modos de Endereçamentos • • • • Modo Base mais Deslocamento Este modo de endereçamento tem característica semelhante ao modo indexado, visto que o endereço de acesso a uma célula de memória se obtém através da soma de dois valores, um inserido no campo apropriado da instrução (normalmente denominado campo deslocamento) e o outro valor inserido é em um determinado registrador, denominado registrador – base ou registrador de segmento. A diferença entre eles está na aplicação do propósito do método e, por conseguinte, na forma de implementá-lo. Nesse caso, o valor a se manter fixo é o do registrador – base/segmento, variando o conteúdo do campo deslocamento em cada instrução, diferentemente do modo indexado, onde o conteúdo do registrador é que se altera. Os processadores da família Intel x86 possuem alguns registradores projetados especificamente com a finalidade de servir como registrador de segmento, como os registradores de 16 bits dos primeiros processadores Pentium seguidos posteriormente pelos registradores de segmentos de 32 bits. Este método de endereçamento acarreta uma redução do tamanho das instruções (e, com isso, economiza memória), bem como facilita o processo de relocação dinâmica de programas. 96 CPU Modos de Endereçamentos • Modo Base mais Deslocamento A sua escolha decorre de dois fatores: a) Durante a execução de uma grande quantidade de programas as referências as células de memória, onde se localizam os operandos, normalmente são seqüenciais, ocorrendo poucos acessos a outras instruções fora de ordem (exceto os desvios); b) A maioria dos programas ocupam um pequeno espaço da MP disponível. • • Dessa forma, em vez de ser necessário, em cada instrução, que o campo operando tenha um tamanho correspondente à capacidade total de endereçamento da MP, basta que o endereço desejado seja obtido pela soma de um valor existente em um dos registradores da CPU com o valor contido na instrução. Por isso o método é chamado de base + deslocamento, consistindo, então, na utilização de dois campos na instrução (que substituem o campo operando): um, com o endereço de um registrador (chamado de base ou segmento), e outro, com valor denominado deslocamento (porque contem um valor relativo – que se desloca em relação – à primeira instrução). 97 CPU Arquitetura x86 – CISC x RISC • A arquitetura x86 teve início no processador 8086 da Intel e vem prosseguindo até os processadores atuais. • Esta arquitetura é de tecnologia CISC (Conjunto Complexo de Instrução), que foi muito útil para a época dos primeiros processadores desta linha, mas para os dias atuais tem sido um dificultador no aumento de desempenho dos processadores. • A grande vantagem da tecnologia CISC na época vinha do fato da capacidade da memória principal ser muito pequena, lenta e também muito cara. • Para diminuir esses efeitos, definiu-se um conjunto CISC de instrução para que os programas ficassem menores, consumindo menos memória. • Além disso, uma instrução complexa tinha que ser destrinchada em micro-códigos internos da CPU que ao serem executados ofereciam um desempenho melhor, pois o acesso a memória era muito lento. 98 CPU Arquitetura x86 – CISC x RISC • Uma outra tecnologia existente é a RISC (Conjunto Reduzido de Instruções). • Quando as memórias começaram a ficar mais rápidas e baratas, possibilitando um aumento na sua capacidade, não havia mais empecilhos no uso da arquitetura RISC. • A grande vantagem desta arquitetura era de possuir instruções bem simples e de tamanho fixo, possibilitando a construção de circuitos decodificadores bem mais simples e rápidos. • Infelizmente, a arquitetura x86 se proliferou de forma tão rápida em âmbito mundial que quando o uso da tecnologia RISC se tornou viável, o mercado não iria aceitar, já que todos os softwares até então foram criados para a arquitetura x86. • A solução adotada a princípio foi de manter o projeto da CPU com a arquitetura CISC x86. 99 CPU Arquitetura x86 – CISC x RISC • Esta arquitetura foi mantida até o Pentium (8086, 80286, 80386, 80486, Pentium). • Neste ponto, o uso da tecnologia CISC x86 não estava mais permitindo avanços no desempenho, tornando as CPUs tão complexas que se tornavam lentas e inviáveis. • A solução adotada pela Intel a partir do Pentium Pro foi criar um pré-decodificador que converteria instruções CISC x86 em instruções RISC proprietárias de uso interno. • A partir deste momento, a CPU passava a ser RISC, pois as instruções que eram executadas eram instruções RISC. • Desta forma, novos avanços tecnológicos e de arquitetura foram criados permitindo uma taxa de aumento de clock elevada. 100 CPU Arquitetura x86 - Registradores • Esta arquitetura possuía inicialmente 4 registradores de dados de 16 bits que podiam ser acessados como 2 registradores cada um de 8 bits. 8 bits 8 bits AH AL AX (16 bits) – Acumulador Primário BH BL BX (16 bits) – Acumulador e Registrador Base CH CL CX (16 bits) – Acumulador e Contador DH DL DX (16 bits) – Acumulador e Endereçador de I/O 101 CPU Arquitetura x86 - Registradores • Abaixo seguem os demais registradores de uso específico desta arquitetura. 16 bits 16 bits SP Stack Pointer CS Code Segment BP Base Pointer DS Data Segment SI Source Index SS Stack Segment DI Destination Index ES Extra Segment IP Ponteiro de Instrução FLAGS Estados 102 CPU Arquitetura x86 - Registradores • AX Acumulador Primário – Todas as operações de I/O são realizadas com o uso auxiliar deste registrador; – Operações que utilizam dados imediatos necessitam de menos memória quando feitos através de AX; – Algumas operações com string e instruções aritméticas pedem o uso deste registrador; – Geralmente é usado pelos compiladores para guardar os valores retornados de subrotinas. • BX Registrador Base – É o único registrador de finalidade geral que pode ser utilizado no cálculo de endereços de memória; – Todas as referências à memória que usam esse registrador no cálculo do endereço tomam o registrador de segmento DS como segmento default. 103 CPU Arquitetura x86 - Registradores • CX Contador – É decrementado durante operações com loops e strings; – Tipicamente, é usado para controlar o número de repetições de uma instrução antecedida pelo prefixo “rep”; – Também é usado para controlar rotações e deslocamentos de vários bits. • DX Endereçador de I/O e Registrador de Dados – Foi-lhe dado o nome de registrador de dados, principalmente por força dos mnemônicos; – Em algumas operações de I/O, fornece o endereço, coisa que nenhum outro registrador pode fazer; – Também é usado em operações aritméticas, incluindo multiplicação e divisão, com o resultado a 32 bits; – Pode ser usado por compiladores, juntamente com AX, para guardar os valores retornados de subrotinas. 104 CPU Arquitetura x86 - Registradores • SP Ponteiro de Pilha (Stack Pointer) – Armazena o offset do endereço do topo da pilha, controlando a alocação dinâmica de variáveis e empilhamento de endereços de retorno de subrotinas; – Todas as referências ao SP, por definição usam o registrador SS. • BP Ponteiro de Base (Base Pointer) – Permite acessar dados alocados na pilha; – Tipicamente é usado para acessar parâmetros que foram passados via pilha para uma determinada subrotina. • SI e DI Registradores de Indexação – São usados para acessar dados na memória de dados; – São extensivamente usados nas operações com strings; – Podem ser usados como operandos em todas as operações lógicas e aritméticas de 16 bits. 105 CPU Arquitetura x86 - Registradores • DS Segmento de Dados (Data Segment) – Todo o acesso a dados usa este registrador como referência, mas existem 3 exceções: • Endereços para acessos à pilha são calculados usando o registrador de segmento de pilha (SS); • Endereços para acessos a dados que usam o BP são calculados a partir de SS; • Operações com strings, que usam o DI no cálculo do endereço, são feitas usando ES. • SS Segmento de Pilha (Stack Segment) – Todos os acessos a dados que usam os registradores SP ou BP tomam como referência o registrador de segmento de pilha (SS). • ES Segmento Extra (Extra Segment) – Operações com strings que usam DI para calcular o endereço são feitas usando o registrador ES para definir o segmento. 106 CPU Arquitetura x86 - Registradores • FLAGS Registrador de Estados do Programa 15 14 13 12 * • • • • • * * * 11 10 9 OF DF IF C Carry P Paridade A Carry Auxiliar Z Zero S Sinal • • • • • 8 7 6 TF SF ZF 5 4 3 2 1 0 * AF * PF * CF T Trap (Armadilha) I Interrupção (habilitada/desabilitada) D Direção O Overflow * Reservado, normalmente zero 107 CPU Arquitetura x86 - Registradores • C (Carry) Reflete o “vai um” do bit mais significativo, nas operações aritméticas (de 8 ou 16 bits). Ele também é modificado por algumas instruções de rotação e deslocamento. • P (Paridade) Indica a paridade (par), dos 8 bits menos significativos, do resultado da operação realizada. – P = 1 número par de “1” nos 8 bits menos significativas. – P = 0 número ímpar de “1” nos 8 bits menos significativos. • A (Carry auxiliar) Reflete o “vai um” do bit 3, em uma operação de 8 bits. • Z (Zero) Indica se uma operação teve “0” como resultado. – Z = 1 se o resultado da operação for igual a zero. – Z = 0 se o resultado da operação for diferente de zero. 108 CPU Arquitetura x86 - Registradores • S (Sinal) É igual ao bit de mais alta ordem do resultado de uma operação aritmética. – S = 0 resultado positivo. – S = 1 resultado negativo. • T (Armadilha) Para a depuração de programas, coloca o 8086 no modo passo a passo, de forma a invocar uma exceção após a execução de cada instrução. • I (Interrupção) Habilita ou desabilita a interrupção. – I = 1 interrupção habilitada. – I = 0 interrupção desabilitada. 109 CPU Arquitetura x86 - Registradores • D (Direção) Determina se as operações com string vão incrementar ou decrementar os registradores de indexação (SI e DI) – D = 1 Os registradores SI e DI serão decrementados, ou seja, a string será acessada a partir do endereço mais alto em direção ao mais baixo. – D = 0 Os registradores SI e DI serão incrementados, ou seja, a string será acessada a partir do endereço mais baixo em direção ao mais alto. • O (Overflow) Seu conteúdo é obtido através de uma operação XOR do “carry in” com o “carry out” do bit de mais alta ordem do resultado de uma operação aritmética. Ele indica um overflow de magnitude, em aritmética binária com sinal. OBS: As operações de subtração usam aritmética em complemento a dois e, por isso, o carry é invertido e passa a funcionar como borrow. Se, após uma operação de subtração, obtém-se C = 1, isso indica que não houve borrow, mas C = 0, indica que houve borrow. 110 CPU Arquitetura x86 - Registradores • Registrador IP Ponteiro de Instrução – Este registrador, junto com o registrador CS, são responsáveis por marcar o endereço da próxima instrução a ser executada. 111 CPU Arquitetura x86 – Formato de uma Instrução • Uma instrução no x86 pode ser formada de apenas um byte como pode ter vários bytes. • O formato geral de instruções em uma CPU é formado por uma parte contendo o código da operação (opcode) e uma outra parte contendo os operandos. Veja a figura abaixo: Operando OPCODE OP. 1 Operandos OPCODE OP. 1 OP. 2 112 CPU Arquitetura x86 – Formato de uma Instrução • O Opcode é responsável por identificar a operação a ser realizada pela CPU. • Esta operação pode não possuir operandos, como pode possuir diversos operandos. Vai depender do projeto da CPU. • O opcode pode possuir tamanho fixo ou tamanho variável, isto é, o tamanho do opcode não é o mesmo para todas as instruções. • A arquitetura RISC tem como uma de suas características o tamanho único para a instrução e o tamanho único para o opcode. • Esta característica simplifica bastante o projeto da unidade de busca já que sempre se sabe o tamanho da instrução que irá buscar e do decodificador que já sabe de antemão qual porção das instruções representa o opcode e os operandos. 113 CPU Arquitetura x86 – Formato de uma Instrução • Já a arquitetura CISC, devido ao grande número de instruções e a sua grande complexidade, possui tamanho variável de instruções, de opcode e de operandos. • Esta complexidade é em virtude do fato de que se fossem de tamanho único, seria utilizado o tamanho da maior instrução, fazendo com que o desperdício de memória fosse muito grande. • O fato de ter tamanhos diferenciados, torna bem mais complexa a tarefa de busca, já que não se sabe o tamanho da instrução antes que ela seja buscada, correndo o risco de não se buscar toda a instrução e também de buscar pedaços da instrução seguinte. • O decodificador passa por dificuldades semelhantes, já que o opcode também possui tamanho variado. 114 CPU Modos de Endereçamento do 8086 • Com relação ao endereçamento do 8086, existem 2 tópicos importantes a serem discutidos: – Como é formado o endereçamento da memória (endereço físico), já que os registradores internos da CPU são de 16 bits e que existem 20 linhas de endereços? – Quais os modos de endereçamento disponíveis? O endereço, para acesso à memória, é gerado a partir da adição de um endereço-base (vindo do seletor – registrador de segmento) a um offset (deslocamento). O seletor é deslocado 4 bits à esquerda (o que equivale a uma multiplicação por 16) e então adicionado ao offset. A figura seguinte mostra este procedimento. A partir deste momento, utilizaremos o termo “Endereço Físico” para referenciar o endereço colocado efetivamente no Barramento de Endereços. 115 CPU Modos de Endereçamento do 8086 • Formação de um endereço no 8086: XXXX Seletor: 0000 Offset: Endereço Físico: XXXX XXXX YYYY ZZZZ XXXX YYYY ZZZZ XXXX YYYY ZZZZ 0000 YYYY YYYY (Início) (Deslocamento) (20 bits) • Assim, com duas palavras de 16 bits, gera-se um endereço de 20 bits, o que permite o acesso a até 1M endereços. Exemplo: para acessar o endereço físico de memória (97AC4)16 na área de dados, primeiro deve-se carregar o registrador de segmento DS com um valor apropriado, por exemplo, (97AC)16. Ao executar a instrução MOV AL, [0004], é feita a soma de (97AC0)16 com (0004)16 chegando ao valor (97AC4)16 que é o endereço físico desejado. 116 CPU Modos de Endereçamento da Memória de Dados • Os modos de endereçamento do 8086 podem ser agrupados em seis classes básicas: Imediato, Direto, Indexado, Implicado, Relativo à Base e Pilha. a) Endereçamento Imediato Nesta forma de endereçamento, os operandos estão definidos nos bytes seguintes ao código de operação. Observe que o dado a ser operado é obtido do segmento de código. ADD AX, 2233 IP + CS = m m 05 M+1 33 M+2 22 Deve-se notar que o byte menos significativo precede ao mais significativo. Esta forma de armazenamento é chamada de “little endian” 117 CPU Modos de Endereçamento da Memória de Dados b) Endereçamento Direto Nesta forma de endereçamento, os dois bytes que se seguem ao código constituem o offset do endereço físico (o seletor DS) do dado a ser acessado. Observe que o dado a ser operado é obtido do segmento de dados. ADD AX, [yyzz] IP + CS = m m 03 M+1 06 M+2 M+3 zz yy DS0 + yyzz abcde (Registrador de Segmento de Dados x 16) (Offset) (Endereço Físico) 118 CPU Modos de Endereçamento da Memória de Dados c) Endereçamento Direto, Indexado É obtido com o uso de SI ou DI como indexador. O dado a ser operado é obtido do segmento de dados (no caso do SI) e do segmento extra (no caso do DI). ADD AX, [SI] + yyzz IP + CS = m m 03 M+1 84 M+2 M+3 zz yy DS0 + 0SI yyzz abcde (ou ES) (ou DI) (Endereço Físico) 119 CPU Modos de Endereçamento da Memória de Dados d) Endereçamento Implicado Este modo é uma degeneração do anterior. É obtido quando não se especifica qualquer deslocamento. Neste caso, também é utilizado o segmento de dados. ADD AX, [SI] IP + CS = m m 03 M+1 04 DS0 + 0SI abcde (ou ES) (ou DI) (Endereço Físico) 120 CPU Modos de Endereçamento da Memória de Dados e) Endereçamento Relativo à Base Neste modo de endereçamento, é usado um registrador (BX ou BP) para fornecer a base. Todos os modos de endereçamento até então descritos, com exceção do endereçamento indireto, estão disponíveis neste modo. De forma simplificada, basta somar BX ou BP aos modos anteriores. Existem duas maneiras de implementá-lo: – – Relativo à memória de dados, nesse caso, usam-se BX e DS, Relativo à pilha, neste caso, usam-se BP e SS. e.1) Endereçamento Direto, Relativo à Base ADD AX, [BX + yyzz] IP + CS = m m 03 M+1 87 M+2 M+3 zz yy DS0 + 0BX yyzz abcde (Endereço Físico) 121 CPU Modos de Endereçamento da Memória de Dados e.2) Endereçamento Direto, Indexado, Relativo à Base ADD AX, [BX + rrss][SI+ttuu] IP + CS = m m 03 M+1 80 M+2 M+3 zz yy DS0 0BX + 0SI yyzz abcde (yyzz = rrss + ttuu) (Endereço Físico) 122 CPU Modos de Endereçamento da Memória de Dados e.3) Endereçamento Implicado, Relativo à Base ADD AX, [BX][SI] IP + CS = m m 03 M+1 00 DS0 + 0BX 0SI abcde (Endereço Físico) 123 CPU Modos de Endereçamento da Memória de Dados f) Endereçamento da Pilha O título deste item poderia ser: “endereçamento relativo à base para pilha”. Todos os endereçamentos relativos à base, já vistos, também servem para a pilha, basta substituir BX por BP e, com isso, a CPU usa SS como segmento. ADD AX, [BP + yyzz] IP + CS = m m 03 M+1 86 M+2 M+3 zz yy SS0 + 0BP yyzz abcde (Endereço Físico) 124 CPU Modos de Endereçamento da Memória de Código • • • Sempre que é feita a busca (fetch) de uma instrução, o endereço físico desta instrução é calculado através da soma do endereço de início do segmento (CS) com um deslocamento (offset), dado pelo ponteiro de instrução (IP). Normalmente o conteúdo do IP é incrementado enquanto a instrução é executada. Entretanto, as instruções de desvio jump e call podem modificar o conteúdo do IP de três maneiras: 125 CPU Modos de Endereçamento da Memória de Código a) Endereçamento Relativo Um deslocamento (jump) de 8 ou 16 bits, especificado de forma imediata, é adicionado ao IP (adição binária com sinal). Como não se altera o conteúdo do CS, este salto é classificado como “intrasegmento” (no mesmo segmento), estando limitado dentro do segmento de 64K. Se o valor adicionado ao IP for negativo, o desvio vai para endereços menores ao atual, se for positivo, o desvio vai para endereços maiores. b) Endereçamento Direto Os novos valores de IP ou de IP e CS são especificados na instrução de forma imediata. Esta operação é classificada como “intrasegmento” (salto near – próximo) ou como “intersegmento” (salto far – distante). – – Near altera somente IP (intrasegmento). Far altera IP e CS (intersegmento). 126 CPU Modos de Endereçamento da Memória de Código c) Endereçamento Indireto Qualquer uma das operações da memória de dados podem ser usadas para acessar um dado da memória, porém, esse dado será interpretado como um endereço para um jump ou call. Existem duas opções: – – O jump ou o call especificam, de forma direta (como se fosse um dado), um endereço onde está uma palavra de 16 bits que será carregada no IP. Esta é uma operação intrasegmento, pois não altera o conteúdo de CS (dentro dos 64K). EX: CALL offset_do_endereço_da_subrotina. O jump ou o call especificam, de forma direta (como se fosse um dado), um endereço onde existem duas palavras de 16 bits que serão carregadas em IP e CS. Como o valor de CS é alterado, esta operação é classificada como intersegmento. EX: CALL ES:BX (ponteiro far) 127 CPU Evolução dos Processadores: 80286 • • • • • • O projeto do 286 apresentou o desafio de construir uma CPU poderosa, com uma unidade de gerenciamento de memória integrada e que, ainda por cima, oferecesse compatibilidade com o 8086. A solução adotada pela Intel foi colocar duas CPUs em uma única. O 286 tem a possibilidade de operar no modo 8086, chamado de modo real, mas também pode trabalhar no modo 286, denominado protegido. Logo após o reset, a CPU inicia no modo real e a decisão de operar ou não no modo protegido cabe ao sistema operacional. Resumindo, no modo real o 286 trabalha como um 8086 mais veloz e com ciclos de barramento mais curtos e rápidos. No modo protegido, o 286 torna-se uma CPU com recursos para multitarefa e uma unidade de gerenciamento de memória integrada. 128 CPU Evolução dos Processadores: 80286 • A seguir são listados alguns avanços do 80286 em relação ao 8086. – – – – – – 24 linha de endereços, resultando em 16 MB de memória. Clock mais rápido (chega a 25 MHz). Novas instruções, de forma a apoiar ambientes em multitarefa. Menor número de períodos de clock por instrução. Barramento de dados de 16 bits com 2 períodos de clock.por ciclo. Modo protegido com um gerenciador de memória integrado, oferecendo: • • • – • • 1 GByte de endereço virtual por tarefa, Chaveamento de tarefas eficiente e verificação dos direitos de acesso em uma única instrução, Programação orientada a níveis de privilégio e a descritores. Registradores idênticos aos do 8086 (a menos de alguns registradores de controle) No 286 a transição entre os modos real e protegido não foi implementada de forma tão simples. A entrada no modo protegido era feita por software, porém, o regresso para o modo real só era possível com o reset da CPU. 129 CPU Evolução dos Processadores: 80386 • • • O lançamento do microprocessador 80386 possibilitou um grande salto no desempenho do PC, ao mesmo tempo em que era mantida a compatibilidade com os antecessores 8086 e 80286. Foram feitas melhorias no modo protegido e no gerenciamento de memória, que passaram a oferecer um eficiente apoio aos sistemas operacionais. A seguir apresenta-se um sumário das características do 80386: – – – – – Barramento de endereços e dados de 32 bits, permitindo endereçar 4 GBytes de memória física. Novas instruções para manusear dados de 32 bits. Offsets de endereços de 16 ou 32 bits e gerenciador de memória com novos recursos. Suporte, em hardware, para segmentação e paginação (memória virtual). Aumento de desempenho provocado por: • • • • • • – Barramento de 32 bits, Fila de instruções de 16 bytes, Novos tipos de dados, Menor quantidade períodos de clock por instrução, Gerenciador de memória mais rápido, e Clock mais veloz (de 16 a 33 MHz). Compatibilidade com o software do 8086 (modo real e modo virtual) e 286 (modo protegido). 130 CPU Evolução dos Processadores: 80386 (Registradores) • Alguns registradores foram ampliados para 32 bits, mas foi mantida a compatibilidade com a arquitetura anterior. AX 8 bits 8 bits AH AL EAX (32 bits) BL EBX (32 bits) CL ECX (32 bits) DL EDX (32 bits) BX BH CX CH DX DH 131 CPU Evolução dos Processadores: 80386 (Registradores) • Foram acrescentados mais 2 registradores de dados (FS e GS). 16 bits 16 bits SP ESP CS Code Segment BP EBP SS Stack Segment SI ESI DS DI EDI ES IP EIP FS EFLAGS GS FLAGS Dados 132 CPU Evolução dos Processadores: 80486 • • • O 80486 usa 1,2 milhões de transistores para integrar uma CPU 386, uma unidade de gerenciamento de memória, um cache de 8 Kbytes com controlador e uma unidade de ponto-flutuante. Antes do seu lançamento eram necessários diversos chips para realizar essas operações. A seguir apresenta-se um sumário das características do 80486: – – – – – Adição do coprocessador matemático (80387 com desempenho maior, pois está integrado na mesma pastilha semicondutora da CPU). Adição de um cache de 8 Kbytes para instrução e dados (Cache L1). Modificação do sistema de interface com o barramento de forma a transferir dados em um único período de clock – modo rajada (transfere até 16 bytes em 5 períodos de clock). Recursos para um cache de nível 2 (Cache L2). Dramático aumento de desempenho em relação ao 386 devido a: • • • • • • fila de instruções de 32 bytes, operação do barramento em modo rajada, com uma transferência por período de clock, cache integrado, redução significativa do número de períodos de clock necessários para a execução de cada instrução (muitas instruções são executadas em um único ciclo), coprocessador matemético integrado, clocks mais velozes: 25, 33, 50, 66, 100 MHz. 133 CPU Evolução dos Processadores: Pentium • • • • O Pentium possuía cerca de 3,1 milhões de transistores. O seu ganho de desempenho era o dobro em relação aos 486, que eram os mais rápidos da época. O maior ganho estava nas operações que envolviam ponto-flutuante. Além dos 64 bits de barramento interno e do clock mais rápido, muitas inovações auxiliaram a velocidade do Pentium: – – – – – – • Projeto superescalar, com uma via dupla de acesso, que permite a execução de mais de uma instrução por ciclo de máquina; Unidade de ponto flutuante (processador matemático) com melhor desempenho; Par de memórias caches internas, mais versáteis e eficientes, uma para dados e outra para códigos, que mantêm o processador operando a toda velocidade; Predição de decisão, que determina antecipadamente os desvios; Cheque interno de paridade, que permite detectar erros internos de processamento; Recurso para administração de energia (permite baixo consumo de potência). Superescalar é a capacidade que uma CPU tem de executar simultaneamente duas ou mais instruções. 134 CPU Evolução dos Processadores: Pentium • • • O Pentium possui internamente duas vias de dados, via V e via U. Com estas vias, é possível executar 2 instruções simultaneamente. A via V é usada apenas para cálculos com números inteiros, enquanto que a via U possui conexões tanto com unidades de inteiro como com unidade de ponto flutuante. 135 CPU Evolução dos Processadores: Pentium • • • • • Caso haja problemas de dependência de dados, o Pentium os resolve serializando a execução. Se duas instruções compartilham o mesmo registrador, ou uma precisa de um dado que será resultado de outra instrução, estas deverão ser serializadas. As instruções de desvio são as mais problemáticas, pois, devido a antecipação das buscas e do pipeline, estas instruções podem levar ao descarte de toda esta antecipação, levando a perda de tempo. A unidade de predição de desvio tem por finalidade analisar e decidir se um determinado desvio será aceito ou não. Esta decisão pode ser errada, mas proporciona uma taxa de aumento no acerto, minimizando as perdas em função dos desvios previstos incorretamente. A Intel afirma que um bom preditor pode acertar em 80% das vezes. A Unidade de Ponto-Flutuante foi totalmente redesenhada a partir dos 386 e 486, sendo que agora apresenta características de arquitetura RISC. 136 CPU Evolução dos Processadores: Pentium - MMX • • A arquitetura MMX baseia-se na técnica SIMD (Single Instruction, Multiple Data) de processamento paralelo. A Intel cita a possibilidade de 24 bits para cores em jogos, múltiplos canais de áudio e ótimo ganho da qualidade em animações de vídeo e processamento em tempo real. Assim cresceu a indústria da realidade virtual e aplicativos em 3D. Tipo “packed byte” Byte 7 Byte 6 Byte 5 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0 MM0 MM1 Tipo “packed word” Word 3 MM2 Word 2 Word 1 Word 0 MM3 Tipo “packed doubleword” MM4 Doubleword 1 Doubleword 0 MM5 Tipo “quadword” MM6 Quadword MM7 137 CPU Evolução dos Processadores: Pentium - MMX • • • • • • Basicamente, as novas instruções são capazes de operar em paralelo com vários fragmentos de dados, permitindo que até 8 pares de inteiros sejam operados simultaneamente em registradores de 64 bits. Estes registradores podem ser compostos por: 8 bytes, 4 words (16 bits cada), 2 doublewords (32 bits cada) ou 1 quadword (64 bits). Quaisquer aplicações que exijam um grande volume de cálculos poderão ser beneficiadas com esta estrutura em paralelo, como por exemplo, reconhecimento automático de voz ou compactação de dados em tempo real. As instruções MMX foram implementadas de forma independente da arquitetura e das demais instruções herdadas desde o 80386, não afetando o modo de operação da CPU. Elas podem rodar tanto no modo real como no modo protegido. Só existe ganho nestas novas instruções, onde simulações mostraram ganhos entre 50% e 400%. 138 CPU Evolução dos Processadores: Pentium – MMX2 ou 3DNow • • • • • • • • • As instruções MMX estudadas até agora apenas operam com números inteiros. Elas têm uma grande utilidade para tratamento de sinais de som e imagem. Quando se trata da simulação de ambientes em três dimensões (3D), a representação com números inteiros é insuficiente e torna-se necessária a representação com ponto-flutuante. Nessa situação, o conjunto de instruções MMX perde sua utilidade. Para trabalhar em 3D, é necessário lançar mão das Unidades de Ponto Flutuante. A tecnologia MMX2 consiste em identificar as operações em ponto-flutuante, necessárias para o 3D, e adicionar um hardware capaz de executá-las de forma rápida numa arquitetura SIMD. A AMD foi a primeira a lançar recursos 3D com sua CPU K6-2 3DNow. Em seguida veio a Intel com o Pentium III. Sucederam-se diversas outras tecnologias. Hoje, somente com um driver que deve ser sempre atualizado, como o Direct X e o OpenGL, consegue-se uma portabilidade satisfatória, que abranja todos os processadores de todos os fabricantes. 139 CPU Evolução dos Processadores: Pentium 4 • • • • • • • • • • Em 20 de novembro de 2000, a intel lançou o Pentium 4 (1,4 e 1,5 GHz). Em comparação com a AMD, esta CPU não teve o aumento de desempenho esperado, em alguns casos ficando com desempenho inferior ao da AMD. Porém, com um pipeline de 20 estágios, o ganho em freqüência de clock foi indiscutível. Esta quantidade de estágios é bem maior que a dos demais processadores (12 estágios no Pentium III e 11 no Athlon da AMD). O grande aumento no pipeline deixou clara a intenção da Intel de atingir elevadas freqüências de clock. O problema de um pipeline extenso vem da necessidade de manter todos os seus estágios ocupados. Novas unidades de predição de desvio foram implementadas para diminuir o efeito dos desvios condicionais. Para manter esse pipeline trabalhando a pleno vapor, são necessárias unidades de execução rápidas, que usam ALUs com o dobro da velocidade. Segundo a Intel, este pipeline permite ter até 126 instruções em execução, além de 48 cargas (load) e de 24 armazenamentos (store). A seguir vemos um diagrama de blocos simplificado do Pentium 4. 140 CPU Evolução dos Processadores: Pentium 4 141 CPU Evolução dos Processadores: Pentium 4 • • • • • • • A Unidade de Interface com o Barramento (BIU) é responsável por conectar o processador com o mundo exterior. Este barramento é o FSB e tem largura de banda de 64 bits. O cache L2 foi designado como sendo de transferência avançada, pois trabalha com um barramento de 256 bits e responde à mesma velocidade do clock do núcleo da CPU. O bloco TLB (Translate Lookaside buffer), trabalha de forma a auxiliar o cache L2 nas conversões de endereços que são exigidos pela paginação de memória. Ele guarda as últimas conversões, pois existe grande chance de que a próxima conversão seja semelhante a uma das anteriores. O Preditor de Desvios (DBP – Dynamic Branch Predictor) é o responsável por evitar que o pipeline de 20 estágios seja surpreendido por um desvio. Como foi comentado anteriormente, as instruções x86 são do tipo CISC o que inviabiliza a construção de unidades de processamento eficientes. As instruções x86 são traduzidas em instruções de uso interno, que são chamadas de microoperações que será abreviado por “m-ops”. Estas “m-ops” são do tipo RISC. O Decodificador de Instruções, a ROM de Microcódigos e o Seqüenciador (de microinstruções) são responsáveis por essa tradução. 142 CPU Evolução dos Processadores: Pentium 4 • • • • • • • • • O Trace Cache faz o papel do Cache de Instrução L1. Até o surgimento do Pentium, os caches L1 guardavam as instruções x86, o que significa que um laço de repetições, como um for ou um while, as instruções eram traduzidas repetidas vezes. Esse novo cache trabalha diretamente com as “m-ops”, disponibilizando espaço para até 12.000 “m-ops”. Para ajudar esse cache, foi colocado um buffer para os desvios, representado por BTB (Branch Target Buffer), cujo papel é ajudar na predição dos desvios das “m-ops”. O passo seguinte é a alocação de recursos e a renomeação de registradores. O Pentium disponibiliza 128 registradores internos para a renomeação dos registradores x86. Depois desta etapa, as “m-ops” vão para as respectivas filas (inteiro, ponto flutuante ou acesso à memória). O escalador direciona a instrução para a unidade funcional que fará a sua execução. Existem duas ALU de inteiro rápidas (2 x ALU) que executam duas instruções por ciclo de clock, duas AGU rápidas (2 x AGU) que realizam cálculos para endereços de carga e armazenamento e uma ALU lenta para a realização de cálculos mais complexos. Existe também as Unidades de Ponto-Flutuante que incluem as instruções SSE2 e MMX. Para finalizar temos o cache L1 de dados que foi reduzido para apenas 8Kbytes. 143 CPU Evolução dos Processadores: Pentium 4 HT • • • • • • • O Pentium 4 veio com uma quantidade enorme de recursos, mas, devido aos softwares não estarem preparados para tirar proveito de toda esta gama de recursos, o seu desempenho final ficou muito a desejar. Uma solução adotada pela Intel foi de disponibilizar a execução de duas linhas de código (threads) independentes ao mesmo tempo. Esta CPU foi chamada de Pentium 4 HT (Hyper-Thread). Desta forma, as unidades funcionais que ficavam ociosas na execução de um thread podiam ser utilizadas na execução de outro thread. Sendo assim, os recursos eram melhor utilizados e conseguia-se uma execução em paralelo de dois threads. Vale ressaltar que esta tecnologia visa diminuir o desperdício das unidades ociosas, o que significa que quando não houver disponibilidade de algum recurso que um thread solicita, este ficará parado esperando a liberação do recurso. A seguir mostramos a comparação da execução seqüencial, multitarefa e com HyperThread. 144 CPU Evolução dos Processadores: Pentium 4 HT Recursos da CPU Thread 1 100% Thread 2 Processamento Seqüencial 75% 50% 25% 0% Tempo 145 CPU Evolução dos Processadores: Pentium 4 HT Recursos da CPU 100% Processamento Multitarefa 75% 50% 25% 0% Tempo 146 CPU Evolução dos Processadores: Pentium 4 HT Recursos da CPU 100% Processamento Hyper-thread 75% 50% 25% 0% Tempo 147 CPU Evolução dos Processadores: Pentium 4 HT • Comparando o três casos: Recursos da CPU Thread 1 Thread 2 Processamento Seqüencial 100% 75% 50% 25% 0% Tempo Recursos da CPU Processamento Multitarefa 100% 75% 50% 25% 0% Recursos da CPU 100% 75% 50% 25% 0% Tempo Ganho Processamento Hyper-thread Tempo 148 CPU Evolução dos Processadores: Pentium X ou D • • • • • • • • • Em 18 de abril de 2005, a Intel finalmente concretizou o lançamento da tão esperada arquitetura com dois núcleos de processamento (dual-core). O topo de linha é marcado pelo Pentium Extreme Edition (P5-X) que roda a 3,2 GHz. Para cada core, há disponibilidade de cache L1 com 12K “m-ops” mais 16 Kbytes para dados além do cache L2 de 1 MB. Possui 250 milhões de transistores, sendo 125 milhões para cada núcleo. O barramento frontal é de 200 MHz, o que permite com a tecnologia dual-channel taxas de 6,4 GB/s (200 MHz x 2 x 16 bytes). Como cada um dos dois núcleos deste processador possui recurso HT, o resultado final é que o sistema operacional enxerga quatro processadores. O cache L2 dos processadores dual core são totalmente independentes. Essa independência simplifica o projeto, mas não é desejável. É fácil imaginar que muitas informações poderão estar repetidas nessas duas memórias, o que é um desperdício. 149 CPU Evolução dos Processadores: Pentium X ou D • • • • Além disso, a transferência de dados entre os caches é feita pelo barramento frontal, o que a torna lenta. Em modelos mais recentes deste tipo de CPU, o cache L2 foi unificado, guardando informações para todos os núcleos. Desta forma, aumenta a eficiência da cache, tanto devido a ausência de dados em duplicidade como pelo fato de que um núcleo pode estar usando apenas 20% da capacidade do cache e o outro núcleo os 80% restantes. Na cache individual, um núcleo estaria usando apenas 20% enquanto que o outro ficaria restrito a no máximo 50%, diminuindo o aproveitamento. 150 Barramento ISA • • • • • O barramento utilizado na arquitetura do PC-AT 80286 foi chamada de ISA (Industry Standard Architecture). Placas projetadas com esse barramento, como placas de fax-modem e placas de som, geralmente são mais simples e baratas. Até para os PCs Pentium, apenas aplicações que exigiam grandes velocidades de comunicação, como interfaces de disco, rede e vídeo, rejeitam a configuração ISA, exigindo outro padrão com capacidade de comunicação maior. Contudo, os micros modernos não estão mais equipados com slots ISA. Os principais atributos do barramento ISA são: – – – – – – – Adição de um segundo conector de 36 pinos (2 x 18), adjacente ao de 62 pinos (2 x 31) que existia no PC XT; Recursos para barramento de dados de 8 ou 16 bits; Recursos para endereçamento de memória de 20 e 24 bits; Adição de 3 canais de DMA de 16 bits; Adição de mais 6 níveis de interrupção; Ciclos de barramento com maior velocidade; Apoio para ciclos de I/O sem estados de espera. 151 Barramento EISA • • • A arquitetura EISA (Extended Industry Standard Architecture) surgiu para atender às CPUs com barramento de 32 bits. O EISA trabalha a 8,33 MHz, com 32 bits. Em teoria, o barramento EISA chegaria a 33 MB/s (8,33 MHz x 4). 152 Barramento Local VESA • • • • • • • • O contínuo aumento da velocidade das CPUs mantinha crítico o gargalo na comunicação da CPU com os periféricos conectados ao barramento de expansão. As placas de vídeo estavam sendo prejudicadas com a baixa taxa de transmissão do barramento. O consórcio VESA (Video Equipment Standard Association), formado por mais de 120 companhias, produziu a especificação VL-BUS, também chamada de “VESA Local Bus”. Essa especificação propôs uma maneira de se levarem os sinais do barramento local a um ou mais slots de expansão. Isso permitiu que periféricos transferissem dados à mesma velocidade da CPU. Por estar conectado diretamente ao barramento local da CPU, havia um limite de 2 ou 3 slots. Com um barramento de dados de 32 bits e um clock de 33 MHz, o limite do barramento VESA é de 133 MB/s. (33 MHz x 4 bytes). Também existe a especificação VESA de 64 bits, que possui uma taxa limite de 266 MB/s. 153 Barramento Local VESA • A seguir temos o esquema do barramento VESA Local Bus. 154 Barramento PCI • • • • A arquitetura PCI (Peripheral Component Interconnect), proposta pela Intel, aceita a idéia de que o PC padrão está chegando ao limite. A especificação PCI requer mais trabalho para o seu projeto e torna as placas mais caras, impedindo que pequenas companhias, logo no início, conseguissem projetá-las. Um barramento PCI de 32 bits operando a 33 MHz, possui a mesma velocidade teórica que o VL-BUS. As vantagens sobre o VL-BUS são: – – – – – – Permite até 10 carregamentos elétricos (um pode ser o controlador para barramento ISA); Trabalha com 32 ou 64 bits a uma velocidade de 33 MHz ou 66 MHz; Não carrega demais o barramento da CPU; É plug and play; Permite a conexão de múltiplos barramentos PCI hierarquizados, eletricamente independentes, através de pontes PCI-PCI; Não possui dependência com o processador, por não se tratar de um barramento local. 155 Barramento PCI • A seguir temos o esquema do barramento PCI. 156 Barramento AGP (Accelerated Graphics Port) • • • • • • A Intel desenvolveu o AGP de forma a aproveitar todo o potencial do seu mais recente processador da época, que era o Pentium II. Para trabalhar com gráficos em 3D, era necessário atender a rigorosos requisitos que iam desde uma plataforma robusta até a rapidez de realização de cálculos geométricos, renderizações sofisticadas e texturas detalhadas. Uma das principais restrições aos requisitos acima era o tamanho da memória local de vídeo usada pelo controlador gráfico. Normalmente, o tamanho dessas memórias variava entre 4 e 8 MB. Entretanto, aplicações em 3D podiam utilizar até mesmo 20 MB para disponibilizar um único mapeamento de textura. A memória de vídeo poderia ser estendida para atender a estes requisitos, mas esta seria uma solução extremamente cara e fisicamente inviável. Na época em que foi especificado o AGP, havia uma segunda restrição, relativa à banda passante do barramento PCI que, para estas aplicações, não era suficiente para se obter um desempenho adequado. 157 Barramento AGP (Accelerated Graphics Port) • • • • • Isto porque os controladores gráficos realizavam uma busca antecipada dos mapeamentos de textura nas suas memórias RAM locais. Uma vez que os mapeamentos de textura cresceram muito em tamanho, o barramento PCI começou a tornar-se um gargalo para este tipo de execução. Contudo, a especificação PCI foi estendida a 66 MHz e 64 bits, isto se contar os barramentos operando em "overclock" (ex: 83 MHz). Desta forma, este problema foi atenuado. A tecnologia utilizada no AGP melhorava o desempenho do sistema oferecendo uma via de dados de alta velocidade entre o controlador gráfico do PC e a memória do sistema. Esta via habilitava o controlador gráfico para executar os mapeamentos de textura diretamente da memória, ao invés de carregá-los para a limitada memória local e só então executar os mesmos mapeamentos. 158 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs antes do AGP • • • • Os gráficos tridimensionais de alta resolução, para serem animados, precisam da realização de uma série de cálculos geométricos altamente custosos ao processador, através dos quais é determinada a posição dos objetos no espaço tridimensional. Tipicamente, tais cálculos são realizados pelo processador do PC, uma vez que ele é projetado para as operações em ponto flutuante necessárias, geralmente associadas à imagem principal. Enquanto isso, o controlador gráfico deve processar dados de textura (imagem de fundo) para poder criar as superfícies e as sombras das imagens em 3D. Um aspecto crítico do processamento de gráficos 3D estava associado aos mapas de textura, ou seja, os bitmaps (ou mapa de bits) que descreviam em detalhes as superfícies tridimensionais dos objetos. Basicamente, tal processamento era composto por quatro etapas: 159 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs antes do AGP – os mapas de textura geralmente eram lidos de um arquivo e carregados para a memória do sistema; os dados trafegavam da interface de disco para a memória; – quando uma textura deveria ser usada em uma cena, ela era lida pelo processador, que realizava transformações espaciais (mudança de observador) e de luminescência na estrutura para então guardar o resultado de volta na memória; – em seguida, o controlador gráfico lia as texturas transformadas da memória do sistema e as escrevia na memória local de vídeo; – o controlador gráfico lia as próximas texturas (acrescidas da informação de cores bidimensionais) da memória local de vídeo; esses dados eram então usados para renderizar um quadro, que podia ser mostrado no monitor. 160 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs antes do AGP • • • • Assim sendo, pode-se constatar alguns problemas relacionados à maneira pela qual as texturas eram tratadas pelos PCs antes do AGP. Primeiro, as texturas deviam ser armazenadas tanto na memória do sistema quanto na memória local de vídeo, criando cópias redundantes do mesmo dado. Segundo, o fato de armazenar as texturas na memória local de vídeo, mesmo que temporariamente, estabelecia um limite máximo no tamanho das texturas. Finalmente, a banda de 132 MB/s do barramento PCI 33MHz / 32 bits original limitava a taxa à qual os mapas de textura podiam ser transferidos para o subsistema gráfico, principalmente quando se levava em consideração que vários outros dispositivos de I/O dividiam essa mesma banda. 161 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs antes do AGP • • • Sem o AGP, os aplicativos utilizavam várias estratégias para compensar as limitações inerentes aos PCs atuais; dentre elas, estava a de um algoritmo de "cache" para decidir quais texturas deviam ser armazenadas na memória local de vídeo e na memória do sistema. Se o hardware somente fosse capaz de manipular texturas na memória local de vídeo, o algoritmo normalmente tentaria realizar uma pré-busca das texturas necessárias para cada quadro ou cena na memória local de vídeo. Sem a pré-busca, os usuários perceberiam uma pausa considerável na cena enquanto o software parasse de desenhar para realizar o cache, ou seja, o ato de carregamento da nova textura necessária na memória local de vídeo. 162 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs com AGP • • • • • Os gráficos 3D certamente se beneficiaram das várias evoluções da plataforma PC, como o fato dos processadores P5-II, P5-III e P5-4 terem a característica de uma arquitetura de Barramento Dual Independente (DIB), na qual dois barramentos independentes conectam o núcleo do processador ao cache e ao barramento do sistema PC, o que aumenta significativamente o desempenho do processador. A adição do AGP foi, com certeza, uma alternativa boa na época (até cerca de 2004) para o processador tratar gráficos 3D. O AGP aliviava o gargalo provocado pelos gráficos, colocando um novo barramento dedicado e de alta velocidade que ligava diretamente o barramento local do processador ao controlador gráfico. Isto removia o intenso tráfego 3D e de vídeo do barramento PCI compartilhado. Além disso, o AGP permitia que as texturas fossem acessadas diretamente da memória do sistema durante a renderização, ao invés de serem previamente buscadas para a memória gráfica local. 163 Barramento AGP (Accelerated Graphics Port) Gráficos 3D em PCs com AGP • • • • • • Com isso, segmentos da memória do sistema podiam ser dinamicamente reservados pelo sistema operacional para uso pelo controlador gráfico. Tal memória era denominada memória AGP ou memória "não local" de vídeo. Isto resultava na manutenção de menos texturas na memória local (pelo controlador gráfico), diminuindo o custo total do sistema. Essa inovação também eliminava a limitação do tamanho que a memória gráfica local impõe para as texturas, conseqüentemente possibilitando aos aplicativos usar texturas maiores e então melhorar o realismo e a qualidade da imagem. A figura a seguir resume o ambiente de hardware resultante da implementação do AGP. Deve ser notado que o barramento é capaz de realizar transferências a 528 MB/s (banda passante). 164 Barramento AGP (Accelerated Graphics Port) 165 Barramento Arquitetura Plug and Play • • • • Ao conectar um dispositivo de entrada e saída, precisa-se configurar três parâmetros: Endereço Base de comunicação, Número de Interrupção e Canal de DMA. Nos projetos iniciais, estas configurações eram feitas através de jumpers ou chaves (dipswitch) existentes nas placas dos dispositivos. Este tipo de configuração exigia um conhecimento técnico do assunto, pois além de mexer diretamente no hardware, precisavase ler e entender o manual para saber como configurá-lo. Para agravar o procedimento, precisava-se saber quais eram os valores disponíveis e quais já estavam ocupados. Caso todos os valores disponíveis para a configuração já estivessem ocupados por outros dispositivos, haveria a necessidade de modificar a configuração de algum outro dispositivo para que chegasse a uma configuração única que satisfizesse a todos os dispositivos. No início do uso do computador, a maior parte dos usuários eram pessoas com conhecimento técnico suficiente para lidar com esta tarefa. 166 Barramento Arquitetura Plug and Play • • • • • Com o passar dos anos, novos grupos de pessoas começaram a aderir ao uso do computador, e este grupo não possuía este tipo de conhecimento. Para se evitar as referidas dificuldades de configuração, de reconfiguração e de atualização, que tanto frustravam os usuários, foram idealizados sistemas confortáveis, denominados plug and play, ou seja, conecte e opere. Tecnicamente falando, o objetivo de um sistema plug and play é permitir que a BIOS ou o Sistema Operacional instalem e configurem quaisquer combinações de placas de expansão e dispositivos. Desta forma, aquele método de configuração por jumpers ou chaves passa a ser substituído por um gerenciamento por software. A flexibilidade conseguida com este sistema é tal que permite reconfigurações mesmo com a máquina já em operação. 167 Barramento Arquitetura Plug and Play • • • • A solução plug and play consiste em fazer com que o hardware, o firmware, o Sistema Operacional e os aplicativos sejam capazes de compartilhar dispositivos, o que é conseguido através da definição de identificadores de dispositivos (tipo, de placa, fabricante, versão, etc.) e de recursos exigidos (interrupção, canal de DMA e endereços de I/O ou memória), que são estruturas de dados padronizadas pela arquitetura plug and pIay. O primeiro passo para que seja constituído o ambiente plug and play é identificar a configuração da máquina, o que é feito inicialmente pela BIOS e posteriormente gerenciado pelo Sistema Operacional, através da construção de uma árvore de hardware, que é uma estrutura em árvore que mapeia o hardware. Tal árvore deve conter os registros necessários para estabelecerem-se a assinatura ou identificação dos dispositivos e a informação necessária para automaticamente localizar e carregar os device-drivers. Após carregar o device-driver, adiciona-se à árvore de hardware um nó de dispositivo associado ao driver, mesmo com toda a máquina já inicializada e com os programas aplicativos sendo executados. 168 Barramento Arquitetura Plug and Play • • • • Vale observar que toda placa-mãe que admite a arquitetura plug and play possui uma BIOS que durante a inicialização do computador, busca e armazena os registros de nós de dispositivos, contendo as informações dos recursos exigidos. Isto orienta todas as partições de Sistemas Operacionais e os device-drivers que possam futuramente ser instalados. Após a instalação, os nós de dispositivos são acrescentados ou modificados segundo as necessidades do Sistema Operacional. É importante ressaltar que quaisquer tipos de conexões elétricas fazem parte da árvore hardware, inclusive todas as ligações hierárquicas entre os barramentos, como, por exemplo a ponte barramento local - barramento ISA ou PCI. A figura a seguir ilustra um caso de configuração envolvida numa árvore de hardware. 169 Barramento Arquitetura Plug and Play 170 Barramento Arquitetura Plug and Play • • Um problema, de solução não trivial, surge ao se distribuírem os recursos pelos nós da árvore de hardware, que é o de identificar os dispositivos estáticos, como placas ISA que não têm flexibilidade de alterar dinamicamente os recursos de interrupção, de DMA e de endereços de I/O ou memória. Por falta desta flexibilidade, duas são as opções para tais dispositivos: mapeá-los de forma prioritária (ex: se o dispositivo exigir a IRQ 5, ele a terá disponível) ou desligá-los (desconectá-los logicamente da configuração da máquina e fisicamente do barramento), o que não é uma alternativa adequada. 171 Barramento Arquitetura Plug and Play • • Um problema, de solução não trivial, surge ao se distribuírem os recursos pelos nós da árvore de hardware, que é o de identificar os dispositivos estáticos, como placas ISA que não têm flexibilidade de alterar dinamicamente os recursos de interrupção, de DMA e de endereços de I/O ou memória. Por falta desta flexibilidade, duas são as opções para tais dispositivos: mapeá-los de forma prioritária (ex: se o dispositivo exigir a IRQ 5, ele a terá disponível) ou desligá-los (desconectá-los logicamente da configuração da máquina e fisicamente do barramento), o que não é uma alternativa adequada. 172 Barramento USB (Universal Serial Bus) • • • • O Barramento Serial Universal (USB), especificado pelas empresas líderes no mercado de computadores pessoais permite uma expansão externa de até 127 dispositivos. Com o USB, os usuários aproveitam os benefícios da arquitetura plug and play, ou seja, não necessitam mais de efetuar configurações de recursos de hardware, como nos quebracabeças dos dip-switches e jumpers, para a definição de IRQs, canais de DMA ou endereços de I/O. O USB utiliza um conector universal que permite ao usuário instalar e remover periféricos sem sequer abrir o computador. E ainda, com a característica de inserção e remoção automáticas, os periféricos podem ser instalados e removidos a qualquer momento, mesmo com o computador ligado e inicializado. 173 Barramento USB (Universal Serial Bus) • • • Dois importantes atributos do USB são também destacados: a compatibilidade universal, pois nada impede que o USB seja aproveitado por outra arquitetura, e a simplicidade no projeto de periféricos, pois são eliminados diversos custos, como o de interfaces auxiliares de que, por exemplo, alguns scanners e CDROM precisam (no caso, uma SCSI). O USB pode ser usado com a maioria dos periféricos de PCs, tais como: controladoras de vídeo, drives de CDROM, flash drive, joysticks, unidades de fita, drives externos de disco flexível, máquina fotográfica digital, scanners ou impressoras. A taxa de comunicação especificada é de 1,5 ou 12 Mbits/s para a versão 1.0/1.1 e de até 480 Mbits/s para a versão 2.0. 174 Barramento USB (Universal Serial Bus) • • Uma arquitetura USB é bem simples, pois é constituída por um hospedeiro (Host) e por diversos dispositivos USB a ele conectados. Quanto à organização das camadas de software necessárias para operar um dispositivo, o sistema USB é composto por vários níveis de hardware e software conforme mostrado na figura a seguir. 175 Barramento USB (Universal Serial Bus) 176 Barramento USB (Universal Serial Bus) • • • • • • • • Como visto na figura, um aplicativo requer o acesso a um periférico USB de forma idêntica à utilizada pelos periféricos comuns: chama funções da API. Num segundo estágio, a API chama rotinas do Driver Cliente do periférico USB instalado. Este driver traduz os comandos da API para comandos USB. O driver Cliente é geralmente parte do Sistema Operacional ou vem para ser instalado junto com o dispositivo USB. A terceira camada de software indicada é o Driver USB (USBD), que é aquela que dá ao Sistema Operacional o suporte ao USB. A quarta camada de interesse é o Driver do Controlador HOST (HCD), que faz parte do Kernel (ou núcleo) do Sistema Operacional. O HCD provê o nível de software entre o hardware do controlador HOST e o USBD. É esta camada que realiza os acessos de I/O necessários para a operação do dispositivo USB. O HCD interpreta as chamadas do USBD e constrói uma lista de estruturas, um descritor de transferências, uma fila principal e um buffer de dados para o controlador HOST. 177 Barramento USB (Universal Serial Bus) • • • • • • • A figura apresenta também duas camadas de hardware. A primeira delas é o Controlador HOST (HC), presente geralmente na Ponte Sul do chipset, que é o circuito onde serão feitas as conexões de todos os dispositivos USB. Tal circuito executa eletronicamente os comandos programadas pelo HCD, além de registrar o estado das transações do USB. Sua operação é gerenciada pelo HCD. A segunda camada de hardware é constituída pelo conjunto de Dispositivos USB conectados, que são os periféricos que usam esse típo de barramento. Uma característica extremamente inovadora do USB é a possibilidade de conectar-se um novo dispositivo durante a execução do aplicativo. Neste caso, o Controlador HOST detecta a conexão e envia uma mensagem ao HCD para avisá-lo do fato. Em seguida, o HCD faz a mesma notificação ao driver USB (USBD). Este, então, inicializa o driver cliente do periférico conectado e, em seguida, torna-o operacional, de forma que o aplicativo já possa dispor de seus recursos. Tal seqüência está ilustrada na figura a seguir: 178 Barramento USB (Universal Serial Bus) 179 Barramento USB (Universal Serial Bus) • • • • • Um exemplo básico da topologia de uma rede de dispositivos conectados via USB está ilustrado na figura a seguir. Nela, um PC com recurso para USB contém um circuito especial, chamado de Controlador Host. Cabe ao Controlador Host receber a conexão de um ou mais periféricos USB, num hub embutido ou hub raiz, e implementar uma ponte entre estes periféricos e um dos barramentos implementados pelo chipset do computador, que pode ser o barramento frontal (FSB do processador, o PCI ou o PCMCIA). Normalmente, uma placa mãe que admite o USB faz a ponte do Controlador Host com o FSB na Ponte Sul do chipset. Contudo, existem placas de expansão para barramento PCI e PCMCIA que implementam o Host do padrão USB. O fluxo de dados que chega ao Controlador Host é chamado de upstream enquanto que o fluxo de dados que sai é chamado de downstream. 180 Barramento USB (Universal Serial Bus) • • É possível ter a presença de um hub, que é um circuito responsável por aceitar a conexão de diversos periféricos USB, também chamados de funções, de forma que todos eles possam trocar informações com o Controlador Host. É possível também expandir a rede USB conectando-se sucessivamente diversos hubs, desde que se totalize um máximo de 127 dispositivos, onde cada dispositivo pode conter até 16 dispositivos de hierarquia menor, chamados de endpoints. 181 Barramento USB (Universal Serial Bus) 182 Barramento USB (Universal Serial Bus) 183 Barramento Chipsets • • • • Uma CPU sozinha não é suficiente para construir um computador. Para que possa trabalhar e rodar programas, a CPU precisa, além da memória, de uma série de circuitos auxiliares: gerador de clock, controlador de Interrupção, controlador de DMA, temporizadores, decodificadores, pontes PCI e ISA, controlador USB e muitos outros. Chipset é um grupo de circuitos integrados destinados a uma tarefa específica, como por exemplo, construir um computador. No caso dos PCs, o chipset traz integrado uma série de dispositivos auxiliares, tais como: controladores de interrupções, de DMA e de memória dinâmica, temporizadores, pontes PCI e ISA, etc. Cada chipset define um computador diferente. Alguns processadores, em especial os da Intel, apresentam dois barramentos principais: o barramento frontal – FSB (Front Side Bus) e o barramento traseiro – BSB (Back Side Bus). 184 Barramento Chipsets • • Como pode ser visto na figura abaixo, o BSB é usado para conexão exclusiva com a memória cache L2, enquanto que o FSB faz as conexões com todo o resto do computador. O FSB é o principal barramento de conexão do processador com o chipset. 185 Barramento Chipsets • • • • • • • • • A partir dos processadores de 64 bits, a AMD passou a empregar uma arquitetura um pouco diferente. Nesta arquitetura, o controlador de memória já vem integrado à CPU. Desta forma consegue-se grandes velocidades nas transferências de dados. Mas o processador já vem de fábrica preparado para um determinado tipo de memória. Para conexão com o chipset, a AMD emprega um canal bidirecional, denominado de HTT (Hyper Transport Technology). No caso de um Athlon 64 FX de 2,6 GHz, emprega-se um clock de 200 MHz que, multiplicado por 13 gera os 2,6 GHz para a CPU. A conexão com a memória é feita à velocidade duplicada com dois barramentos de 64 bits, o que resulta numa banda de 6,4 GB/s (200 MHz x 2 x 16 bytes). Já o canal HTT é de 16 bits e trabalha com clock de 2 GHz, o que resultaria em 4.0 GB/s. Como o canal é bidirecional, esse número é dobrado, resultando em 8,0 GB/s. 186 Barramento Chipsets • Abaixo tem-se um diagrama do Athlon 64 FX. 187 Barramento Chipsets • A seguir temos uma amostra de conexão da CPU com os Chipsets. 188 CPU Modos de Endereçamentos • • Modo Base mais Deslocamento Consideremos, por exemplo, o caso de processadores, nos quais as instruções possuem campo de endereço de registrador – base com 4 bits (estipulamos no exemplo que o processador possui 16 registradores e, portanto, será necessário se definir 16 endereços, um para cada registrador) e campo deslocamento com 12 bits. E que o processador pode endereçar até 16M células (cada endereço linear de memória deverá ter 24 bits). Nesse caso, podem-se endereçar áreas de 4.096 bytes (4K bytes) com valor armazenado no registrador – base, gastando-se apenas 16 bits (4 + 12) ao contrário dos 24 bits necessários para endereçar diretamente todas as células da MP daquele computador (capacidade máxima da MP = 16M bytes). Economizam-se, assim, 8 bits em cada instrução. 189