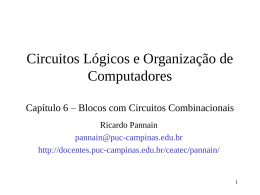

Circuitos Lógicos e Organização de Computadores Capítulo 7 – Flip-Flops e Circuitos Seqüenciais Ricardo Pannain [email protected] http://docentes.puc-campinas.edu.br/ceatec/pannain/ 1 Circuito Seqüenciais Circuito combinacional saídas dependem apenas das entradas Cicuito seqüencial saídas dependem das entradas e do comportamento anterior do circuito Exemplo - Controle de Sistema de Alarme Sensor Set Memory element On Off Alarm Reset 2 Elemento de memória simples A B Elemento de memória com portas NOR Reset Elemento de memória controlado Set Q Load A Data B Output TG1 TG2 3 Latch construído com portas NOR R Qa Qb S (a) Circuito t1 t2 S R Qa Qb 0 0 0/11/0 0 1 0 1 1 0 1 0 1 1 0 0 (sem alteração) (b) Tabela Verdade t3 t4 t5 t6 t7 t8 t9 t 10 1 R 0 1 S 0 1 Qa ? 0 1 Qb ? 0 Time (c) Diagrama de Tempo 4 Latch SR com clock (gated) R R Q Clk Q S S Clk S R Q(t + 1) 0 x x Q(t) (sem alteração) 1 0 0 Q(t) (sem alteração) 1 0 1 0 1 1 0 1 1 1 1 x (a) Circuito (b) Tabela Verdade 1 Clk 0 1 R S 0 Q Clk 1 S R 0 1 ? Q Q (d) Símbolo Gráfico 0 Q 1 ? 0 Time (c) Timing diagram 5 Latch SR Gated SR com portas NAND S Q Clk Q R 6 Latch D Gated S D (Data) Clk D Q 0 1 1 Clk Q(t ) 0 1 (b) Tabela Verdade Q R x 0 1 Q(t + 1) D Q (a) Circuito Clk Q t1 t2 t3 t4 (c) Símbolo Gráfico Clk D Q Time (d) Diagrama de Tempo 7 Setup and hold times t su th Clk D Q Setup time tempo mínimo que D deve estar estável antes da descida do clock Hold time temp mínimo que D deve ser mantido estável após a descida do clock Valores típos (CMOS): tsu = 3ns e th = 2ns 8 Flip-Flop D Master-slave Master D Clock D Q Slave Qm Clk Q D Q Clk Q Qs Q Q D (a) Circuito Q Q (c) Símbolo Gráfico Clock D CLK = 1 master armazena e slave não muda CLK = 0 master não muda e slave armazena Qm Q = Qs (b) Diagrama de tempo 9 Sensível à borda de descida Flip-Flop D sensível à borda de subida 1 P3 D 2 Clock P1 5 Q Q (b) Símbolo Gráfico Clock 3 D Q 4 P2 P4 (a) Circuito 6 Q Clk = 0 P1 = P2 = 1 P3 = D P4 = D Clk =1 P3 e P4 são transmitidos através de 2 e 3 P1 = D e P2 = D Q = D e Q = D Obs - P4 e P3 DEVEM ESTAR ESTÁVEIS QUANDO CLK MUDA PARA 1 10 Comparação de Flip-Flops D sensíveis a nivel e sensíveis a borda D Clock Q Qa Clk Q Qa D Clock D D Q Qb D Q Qb Qa Q Qc Qb Q Qc Qc (a) Circuito (b) Diagrama de Tempo 11 Flip-Flop Master-slave tipo D com Clear e Preset Preset D Q Clock Q Clear (a) Circuito Preset D Q Q Clear (b) Símbolo Gráfico 12 Flip-Flop D sensível à borda de subida com Clear e Preset Preset Q Preset D Q Clock Q Q Clear (b) Símbolo Gráfico D Clear (a) Circuito 13 Flip-Flop D com reset síncrono Clear D D Clock Q Q Q Q 14 Flip-Flop tipo T (toogle) D T Q Q Q Q T Q(t + 1) 0 Q(t ) 1 Q(t ) (b) Tabela Verdade T Q Q Clock (c) Símbolo Gráfico (a) Circuito Clock T Q (d) Diagrama de tempo 15 Flip-Flop JK D=JQ+ KQ J D K Q Q Q Q J e K entradas De controle FFs SR e T juntos Clock (a) Circuito J K Q ( t + 1) 0 0 1 1 0 1 0 1 Q (t) 0 1 Q (t ) (b) Tabela Verdade J Q K Q (c) Símbolo Gráfico 16 Registrador de deslocamento com entrada e saída serial Registrador é um conjunto de n Flip-Flops In Q D Clock Q1 Q D Q Q2 Q D Q Q3 D Q Q Q4 Out Q (a) Circuito t0 In 1 Q1 0 Q2 0 Q3 0 Q4 = Out 0 t1 0 1 0 0 0 t2 1 0 1 0 0 t3 1 1 0 1 0 t4 1 1 1 0 1 t5 0 1 1 1 0 t6 0 0 1 1 1 t7 0 0 0 1 1 (b) Exemplo de uma seqüência FFs master-slave ou sensível à borda. Porque não sensível a nível ? 17 Registrador de deslocamento com entrada paralela e serial e saída paralela Parallel output Q3 D Q Q Serial input Shift/Load Q2 D Q Q Parallel input Q1 D Q Q Q0 D Q Q Clock 18 Contadores Contador de 3 bits up-counter 1 Q T Clock Q T Q Q T Q Q0 Q Q1 Q2 (a) Circuito Clock Q0 Q1 Q2 Count 0 1 2 3 4 5 6 7 0 19 (b) Diagrama de tempo Contador de 3 bits down-counter Clock 1 T Q T Q Q T Q Q0 Q Q Q1 Q2 (a) Circuit Clock Q0 Q1 Q2 Count 0 7 6 5 4 3 (b) Timing diagram 2 1 0 20 Derivação de contador síncrono up-counter Clock cycle 0 1 2 3 4 5 6 7 8 Q2 Q1 Q0 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 Q1 muda Q2 muda T0 = 1 T1 = Q0 T2 = Q0 Q1 T3 = Q0 Q1 Q2 Tn = Q0 Q1 ... Qn 21 Contador síncrocno de quatro-bits up-counter 1 Q T Q T T Q0 Clock Q Q1 Q T Q Q2 Q Q3 Q Q (a) Circuito Clock Q0 Q1 Q2 Q3 Count 0 1 2 3 4 5 6 7 8 9 10 11 (b) Diagrama de tempo 12 13 14 15 0 1 22 Inclusão de sinais de enable e clear Enable Clock T Q Q T Q Q T Q Q T Q Q Clear 23 Enable D Q Q0 Q Contador de 4 bits com FF D D Q Q1 Q D Q Q2 Q D Q Q3 Q Clock Output carry 24 Enable D0 D1 0 1 D Q Q0 Q 0 1 D Q Q1 Q Contador com entrada paralela D2 0 1 D Q Q2 Q D3 0 1 D Q Q3 Q Load Clock Output carry 25 Contador modulo-6 com reset síncrono 1 Enable 0 D0 Q0 0 D1 Q1 0 D2 Q2 Load Clock Clock (a) Circuito Clock Q0 Q1 Q2 Count 0 1 2 3 4 (b) Diagrama de tempo 5 0 1 26 Contador modulo-6 com reset síncrono 1 T Clock Q Q0 Q T Q Q T Q1 Q Q2 Q (a) Circuito Clock Q0 Q1 Q2 Count 0 1 2 3 4 5 (b) Diagrama de tempo 0 1 2 27 Contador BCD de 2 dígitos 1 0 0 0 0 Enable D0 D1 D2 D3 Q0 Q1 Q2 Q3 BCD 0 Q0 Q1 Q2 Q3 BCD 1 Load Clock Clock Clear 0 0 0 0 Enable D0 D1 D2 D3 Load Clock 28 Q0 Q1 Qn ” 1 Start D Q D Q Q D Q Q Q Clock (a) An n -bit ring counter Q0 Q1 Q2 Q3 Contador em Anel y0 y1 y2 y3 2-to-4 decoder w1 1000, 0100, 0010, 0001 w0 En 1 Clock Clock Q1 Q0 Two-bit up-counter Start Clear (b) A four-bit ring counter 29 Contador Johnson Q0 D Q Q Q1 D Q Q Qn – 1 D Q Q Reset Clock 30 Inatalação de um FF D de um package LIBRARY ieee ; USE ieee.std_logic_1164.all ; LIBRARY altera ; USE altera.maxplus2.all ; ENTITY flipflop IS PORT ( D, Clock Resetn, Presetn Q END flipflop ; : IN : IN : OUT STD_LOGIC ; STD_LOGIC ; STD_LOGIC ) ; ARCHITECTURE Structure OF flipflop IS BEGIN dff_instance: dff PORT MAP ( D, Clock, Resetn, Presetn, Q ) ; END Structure ; 31 Memória LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY implied IS PORT ( A, B AeqB END implied ; : IN : OUT STD_LOGIC ; STD_LOGIC ) ; ARCHITECTURE Behavior OF implied IS BEGIN PROCESS ( A, B ) BEGIN IF A = B THEN AeqB <= '1' ; END IF ; END PROCESS ; END Behavior ; 32 Codigo para um latch D gated LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY latch IS PORT ( D, Clk Q END latch ; : IN : OUT STD_LOGIC ; STD_LOGIC) ; ARCHITECTURE Behavior OF latch IS BEGIN PROCESS ( D, Clk ) BEGIN IF Clk = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; 33 Código para um FF D LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY flipflop IS PORT ( D, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC) ; END flipflop ; ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS ( Clock ) BEGIN IF Clock'EVENT AND Clock = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; 34 Código para um FF D usando WAIT UNTIL LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY flipflop IS PORT ( D, Clock : IN Q : OUT END flipflop ; STD_LOGIC ; STD_LOGIC ) ; ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS BEGIN WAIT UNTIL Clock'EVENT AND Clock = '1' ; Q <= D ; END PROCESS ; END Behavior ; 35 FF D com reset assíncrono LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY flipflop IS PORT ( D, Resetn, Clock Q END flipflop ; : IN : OUT STD_LOGIC ; STD_LOGIC) ; ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= '0' ; ELSIF Clock'EVENT AND Clock = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; 36 FF D com reset síncrono LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY flipflop IS PORT ( D, Resetn, Clock Q END flipflop ; : IN : OUT STD_LOGIC ; STD_LOGIC) ; ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS BEGIN WAIT UNTIL Clock'EVENT AND Clock = '1' ; IF Resetn = '0' THEN Q <= '0' ; ELSE Q <= D ; END IF ; END PROCESS ; END Behavior ; 37 Instanciação do módulo lpm_shiftreg LIBRARY ieee ; USE ieee.std_logic_1164.all ; LIBRARY lpm ; USE lpm.lpm_components.all ; ENTITY shift IS PORT ( Clock Reset Shiftin, Load R Q END shift ; : IN : IN : IN : IN : OUT STD_LOGIC ; STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(3 DOWNTO 0) ; STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; ARCHITECTURE Structure OF shift IS BEGIN instance: lpm_shiftreg GENERIC MAP (LPM_WIDTH => 4, LPM_DIRECTION => "RIGHT") PORT MAP (data => R, clock => Clock, aclr => Reset, load => Load, shiftin => Shiftin, q => Q ) ; END Structure ; 38 Código um registrador de 8 bits com clear assíncrono LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY reg8 IS PORT ( D Resetn, Clock Q END reg8 ; : IN STD_LOGIC_VECTOR(7 DOWNTO 0) ; : IN STD_LOGIC ; : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ) ; ARCHITECTURE Behavior OF reg8 IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= "00000000" ; ELSIF Clock'EVENT AND Clock = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; 39 Código um registrador de n-bit com clear assíncrono LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY regn IS GENERIC ( N : INTEGER := 16 ) ; PORT ( D : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; Resetn, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END regn ; ARCHITECTURE Behavior OF regn IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= (OTHERS => '0') ; ELSIF Clock'EVENT AND Clock = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; 40 Código para um FF D com um multiplexador 2-para-1 na entrada D LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY muxdff IS PORT ( D0, D1, Sel, Clock : IN Q : OUT END muxdff ; STD_LOGIC ; STD_LOGIC ) ; ARCHITECTURE Behavior OF muxdff IS BEGIN PROCESS BEGIN WAIT UNTIL Clock'EVENT AND Clock = '1' ; IF Sel = '0' THEN Q <= D0 ; ELSE Q <= D1 ; END IF ; END PROCESS ; END Behavior ; 41 Código hierárquico para um shift-register de 4 bits LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY shift4 IS PORT ( R L, w, Clock Q END shift4 ; : IN : IN : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; ARCHITECTURE Structure OF shift4 IS COMPONENT muxdff PORT ( D0, D1, Sel, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC ) ; END COMPONENT ; BEGIN Stage3: muxdff PORT MAP ( w, R(3), L, Clock, Q(3) ) ; Stage2: muxdff PORT MAP ( Q(3), R(2), L, Clock, Q(2) ) ; Stage1: muxdff PORT MAP ( Q(2), R(1), L, Clock, Q(1) ) ; Stage0: muxdff PORT MAP ( Q(1), R(0), L, Clock, Q(0) ) ; END Structure ; 42 Alternativa para o shift register LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY shift4 IS PORT ( R : IN Clock : IN L, w : IN Q : BUFFER END shift4 ; STD_LOGIC_VECTOR(3 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; ARCHITECTURE Behavior OF shift4 IS BEGIN PROCESS BEGIN WAIT UNTIL Clock'EVENT AND Clock = '1' ; IF L = '1' THEN Q <= R ; ELSE Q(0) <= Q(1) ; Q(1) <= Q(2); Q(2) <= Q(3) ; Q(3) <= w ; END IF ; END PROCESS ; END Behavior ; 43 Contador up-counter quatro-bits LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE ieee.std_logic_unsigned.all ; ENTITY upcount IS PORT ( Clock, Resetn, E Q END upcount ; : IN STD_LOGIC ; : OUT STD_LOGIC_VECTOR (3 DOWNTO 0)) ; ARCHITECTURE Behavior OF upcount IS SIGNAL Count : STD_LOGIC_VECTOR (3 DOWNTO 0) ; BEGIN PROCESS ( Clock, Resetn ) BEGIN IF Resetn = '0' THEN Count <= "0000" ; ELSIF (Clock'EVENT AND Clock = '1') THEN IF E = '1' THEN Count <= Count + 1 ; ELSE Count <= Count ; END IF ; END IF ; END PROCESS ; Q <= Count ; END Behavior ; 44 Contador de 4 bits com carga paralela usando sinais INTEGER LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY upcount IS PORT ( R Clock, Resetn, L Q END upcount ; : IN : IN : BUFFER INTEGER RANGE 0 TO 15 ; STD_LOGIC ; INTEGER RANGE 0 TO 15 ) ; ARCHITECTURE Behavior OF upcount IS BEGIN PROCESS ( Clock, Resetn ) BEGIN IF Resetn = '0' THEN Q <= 0 ; ELSIF (Clock'EVENT AND Clock = '1') THEN IF L = '1' THEN Q <= R ; ELSE Q <= Q + 1 ; END IF; END IF; END PROCESS; END Behavior; 45 Contador down-counter LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY downcnt IS GENERIC ( modulus : INTEGER := 8 ) ; PORT ( Clock, L, E : IN STD_LOGIC ; Q : OUT INTEGER RANGE 0 TO modulus-1 ) ; END downcnt ; ARCHITECTURE Behavior OF downcnt IS SIGNAL Count : INTEGER RANGE 0 TO modulus-1 ; BEGIN PROCESS BEGIN WAIT UNTIL (Clock'EVENT AND Clock = '1') ; IF E = '1' THEN IF L = '1' THEN Count <= modulus-1 ; ELSE Count <= Count-1 ; END IF ; END IF ; END PROCESS; Q <= Count ; END Behavior ; 46 Sistema digital com k registradores Data Extern Bus Clock R1 R1in R1out R2 R2in R2out Rk Rkin Rkout Control circuit Function 47 Conexão dos registradoes ao barramento Bus R 1out D R 2out Q D Q Q D Q R 1in Q D Q Q Q R 2in Clock R1 R2 48 Circuito de controle com um shift-register R2out ,R3in w Clock D Q Q R1out ,R2in D Q Q R3out ,R1in D Q Q Reset 49 Circuito de controle modificado R2out ,R3in R1out ,R2in R3out ,R1in Reset w D PQ Clock Q D Q Q D Q Q 50 Cicuito de controle com FF sem preset R2out ,R3in R1out ,R2in R3out ,R1in w D Clock Q Q D Q Q D Q Q Reset 51 Usando multiplexadores para implementação de um barramento Bus R1in R2in R1 R2 Rkin Rk Clock Data S0 Multiplexers Sj – 1 52 Código para registrador de n-bits com enable LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY regn IS GENERIC ( N : INTEGER := 8 ) ; PORT ( R : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; Rin, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END regn ; ARCHITECTURE Behavior OF regn IS BEGIN PROCESS BEGIN WAIT UNTIL Clock'EVENT AND Clock = '1' ; IF Rin = '1' THEN Q <= R ; END IF ; END PROCESS ; END Behavior ; 53 Código para buffer tri-sate n-bits LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY trin IS GENERIC ( N : INTEGER := 8 ) ; PORT ( X : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; E : IN STD_LOGIC ; F : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END trin ; ARCHITECTURE Behavior OF trin IS BEGIN F <= (OTHERS => 'Z') WHEN E = '0' ELSE X ; END Behavior ; 54 Código para controlador com for the shift-register LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY shiftr IS -- left-to-right shift register with async reset GENERIC ( K : INTEGER := 4 ) ; PORT ( Resetn, Clock, w : IN STD_LOGIC ; Q : BUFFER STD_LOGIC_VECTOR(1 TO K) ) ; END shiftr ; ARCHITECTURE Behavior OF shiftr IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= (OTHERS => '0') ; ELSIF Clock'EVENT AND Clock = '1' THEN Genbits: FOR i IN K DOWNTO 2 LOOP Q(i) <= Q(i-1) ; END LOOP ; Q(1) <= w ; END IF ; END PROCESS ; END Behavior ; 55 Declaração de package e component LIBRARY ieee ; USE ieee.std_logic_1164.all ; PACKAGE components IS COMPONENT regn -- register GENERIC ( N : INTEGER := 8 ) ; PORT ( R : IN Rin, Clock : IN Q : OUT END COMPONENT ; STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; COMPONENT shiftr -- left-to-right shift register with async reset GENERIC ( K : INTEGER := 4 ) ; PORT ( Resetn, Clock, w : IN STD_LOGIC ; Q : BUFFER STD_LOGIC_VECTOR(1 TO K) ) ; END component ; COMPONENT trin -- tri-state buffers GENERIC ( N : INTEGER := 8 ) ; PORT ( X : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; E : IN STD_LOGIC ; F : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END COMPONENT ; END components ; 56 Sistema digital com bus LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE work.components.all ; ENTITY swap IS PORT ( Data : IN DOWNTO 0) ; Resetn, w : IN Clock, Extern : IN RinExt : IN BusWires : INOUT DOWNTO 0) ) ; END swap ; STD_LOGIC_VECTOR(7 STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(1 TO 3) ; STD_LOGIC_VECTOR(7 57 Sistema digital com bus - continuação ARCHITECTURE Behavior OF swap IS SIGNAL Rin, Rout, Q : STD_LOGIC_VECTOR(1 TO 3) ; SIGNAL R1, R2, R3 : STD_LOGIC_VECTOR(7 DOWNTO 0) ; BEGIN control: shiftr GENERIC MAP ( K => 3 ) PORT MAP ( Resetn, Clock, w, Q ) ; Rin(1) <= RinExt(1) OR Q(3) ; Rin(2) <= RinExt(2) OR Q(2) ; Rin(3) <= RinExt(3) OR Q(1) ; Rout(1) <= Q(2) ; Rout(2) <= Q(1) ; Rout(3) <= Q(3) ; tri_ext: trin PORT MAP ( Data, Extern, BusWires ) ; reg1: regn PORT MAP ( BusWires, Rin(1), Clock, R1 ) ; reg2: regn PORT MAP ( BusWires, Rin(2), Clock, R2 ) ; reg3: regn PORT MAP ( BusWires, Rin(3), Clock, R3 ) ; tri1: trin PORT MAP ( R1, Rout(1), BusWires ) ; tri2: trin PORT MAP ( R2, Rout(2), BusWires ) ; tri3: trin PORT MAP ( R3, Rout(3), BusWires ) ; END Behavior ; 58 Usando multiplexadores para implementar um bus LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE work.components.all ; ENTITY swapmux IS PORT ( Data Resetn, w Clock RinExt BusWires END swapmux ; : IN : IN : IN : IN : BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(1 TO 3) ; STD_LOGIC_VECTOR(7 DOWNTO 0) ) ; ARCHITECTURE Behavior OF swapmux IS SIGNAL Rin, Q : STD_LOGIC_VECTOR(1 TO 3) ; SIGNAL S : STD_LOGIC_VECTOR(1 DOWNTO 0) ; SIGNAL R1, R2, R3 : STD_LOGIC_VECTOR(7 DOWNTO 0) ; BEGIN control: shiftr GENERIC MAP ( K => 3 ) PORT MAP ( Resetn, Clock, w, Q ) ; … con’t 59 Usando multiplexadores para implementar um bus - continuação Rin(1) <= RinExt(1) OR Q(3) ; Rin(2) <= RinExt(2) OR Q(2) ; Rin(3) <= RinExt(3) OR Q(1) ; reg1: regn PORT MAP ( BusWires, Rin(1), Clock, R1 ) ; reg2: regn PORT MAP ( BusWires, Rin(2), Clock, R2 ) ; reg3: regn PORT MAP ( BusWires, Rin(3), Clock, R3 ) ; encoder: WITH Q SELECT S <= "00" WHEN "000", "10" WHEN "100", "01" WHEN "010", "11" WHEN OTHERS ; muxes: --eight 4-to-1 multiplexers WITH S SELECT BusWires <= Data WHEN "00", R1 WHEN "01", R2 WHEN "10", R3 WHEN OTHERS ; END Behavior ; 60 Código simplificado para descrever um barramento (ENTITY declaration not shown) ARCHITECTURE Behavior OF swapmux IS SIGNAL Rin, Q : STD_LOGIC_VECTOR(1 TO 3) ; SIGNAL R1, R2, R3 : STD_LOGIC_VECTOR(7 DOWNTO 0) ; BEGIN control: shiftr GENERIC MAP ( K => 3 ) PORT MAP ( Resetn, Clock, w, Q ) ; Rin(1) <= RinExt(1) OR Q(3) ; Rin(2) <= RinExt(2) OR Q(2) ; Rin(3) <= RinExt(3) OR Q(1) ; reg1: regn PORT MAP ( BusWires, Rin(1), Clock, R1 ) ; reg2: regn PORT MAP ( BusWires, Rin(2), Clock, R2 ) ; reg3: regn PORT MAP ( BusWires, Rin(3), Clock, R3 ) ; muxes: WITH Q SELECT BusWires <= Data R2 R1 R3 END Behavior ; WHEN "000", WHEN "100", WHEN "010", WHEN OTHERS ; 61 Sistema digital implementa um processador simples Data Bus Clock R0 R3 B A G R 0in R 0out R 3in R 3out Ain Gin Gout AddSub w Function Extern Control circuit Done 62 Operacões executadas pelo processador 63 Circuito de controle do porcessador T0 T1 T2 T3 y0 y1 y2 y3 2-to-4 decoder w1 w0 En 1 Clock Clear Q1 Q0 Up-counter Reset 64 Registrador de função e os decodificadores I0 I1 X I2 I3 X1 X 2 X3 Y 0 Y1 Y2 Y3 y0 y1 y2 y3 y0 y1 y2 y3 y0 y1 y2 y3 2-to-4 decoder w1 w0 En 2-to-4 decoder w1 w0 En 0 1 1 Clock FRin 2-to-4 decoder w1 w0 En 1 Function Register f1 f 0 Rx1 Rx0 Ry1 Ry0 Function 65 Valores dos sinais de controle para cada operação/time step 66 Código para two-bit up-counter reset assíncrono LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE ieee.std_logic_unsigned.all ; ENTITY upcount IS PORT ( Clear, Clock : IN STD_LOGIC ; Q : BUFFER STD_LOGIC_VECTOR(1 DOWNTO 0) ) ; END upcount ; ARCHITECTURE Behavior OF upcount IS BEGIN upcount: PROCESS ( Clock ) BEGIN IF (Clock'EVENT AND Clock = '1') THEN IF Clear = '1' THEN Q <= "00" ; ELSE Q <= Q + '1' ; END IF ; END IF; END PROCESS; END Behavior ; 67 Código para o processador LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE ieee.std_logic_signed.all ; USE work.subccts.all ; ENTITY proc IS PORT ( Data Reset, w Clock F, Rx, Ry Done BusWires END proc ; : IN : IN : IN : IN : BUFFER : INOUT STD_LOGIC_VECTOR(7 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC ; STD_LOGIC_VECTOR(7 DOWNTO 0) ) ; ARCHITECTURE Behavior OF proc IS SIGNAL Rin, Rout : STD_LOGIC_VECTOR(0 TO 3) ; SIGNAL Clear, High, AddSub : STD_LOGIC ; SIGNAL Extern, Ain, Gin, Gout, FRin : STD_LOGIC ; SIGNAL Count, Zero : STD_LOGIC_VECTOR(1 DOWNTO 0) ; SIGNAL T, I, X, Y : STD_LOGIC_VECTOR(0 TO 3) ; SIGNAL R0, R1, R2, R3 : STD_LOGIC_VECTOR(7 DOWNTO 0) ; SIGNAL A, Sum, G : STD_LOGIC_VECTOR(7 DOWNTO 0) ; SIGNAL Func, FuncReg : STD_LOGIC_VECTOR(1 TO 6) ; … con’t 68 Código para o processador - continuação BEGIN Zero <= "00" ; High <= '1' ; Clear <= Reset OR Done OR (NOT w AND T(0)) ; counter: upcount PORT MAP ( Clear, Clock, Count ) ; decT: dec2to4 PORT MAP ( Count, High, T ); Func <= F & Rx & Ry ; FRin <= w AND T(0) ; functionreg: regn GENERIC MAP ( N => 6 ) PORT MAP ( Func, FRin, Clock, FuncReg ) ; decI: dec2to4 PORT MAP ( FuncReg(1 TO 2), High, I ) ; decX: dec2to4 PORT MAP ( FuncReg(3 TO 4), High, X ) ; decY: dec2to4 PORT MAP ( FuncReg(5 TO 6), High, Y ) ; Extern <= I(0) AND T(1) ; Done <= ((I(0) OR I(1)) AND T(1)) OR ((I(2) OR I(3)) AND T(3)) ; Ain <= (I(2) OR I(3)) AND T(1) ; Gin <= (I(2) OR I(3)) AND T(2) ; Gout <= (I(2) OR I(3)) AND T(3) ; AddSub <= I(3) ; … con’t 69 Código para o processador - continuação RegCntl: FOR k IN 0 TO 3 GENERATE Rin(k) <= ((I(0) OR I(1)) AND T(1) AND X(k)) OR ((I(2) OR I(3)) AND T(3) AND X(k)) ; Rout(k) <= (I(1) AND T(1) AND Y(k)) OR ((I(2) OR I(3)) AND ((T(1) AND X(k)) OR (T(2) AND Y(k)))) ; END GENERATE RegCntl ; tri_extern: trin PORT MAP ( Data, Extern, BusWires ) ; reg0: regn PORT MAP ( BusWires, Rin(0), Clock, R0 ) ; reg1: regn PORT MAP ( BusWires, Rin(1), Clock, R1 ) ; reg2: regn PORT MAP ( BusWires, Rin(2), Clock, R2 ) ; reg3: regn PORT MAP ( BusWires, Rin(3), Clock, R3 ) ; tri0: trin PORT MAP ( R0, Rout(0), BusWires ) ; tri1: trin PORT MAP ( R1, Rout(1), BusWires ) ; tri2: trin PORT MAP ( R2, Rout(2), BusWires ) ; tri3: trin PORT MAP ( R3, Rout(3), BusWires ) ; regA: regn PORT MAP ( BusWires, Ain, Clock, A ) ; alu: WITH AddSub SELECT Sum <= A + BusWires WHEN '0', A - BusWires WHEN OTHERS ; regG: regn PORT MAP ( Sum, Gin, Clock, G ) ; triG: trin PORT MAP ( G, Gout, BusWires ) ; END Behavior ; 70 Alternativa para o código do processador … (ENTITY declaration not shown) ARCHITECTURE Behavior OF proc IS SIGNAL X, Y, Rin, Rout : STD_LOGIC_VECTOR(0 TO 3) ; SIGNAL Clear, High, AddSub : STD_LOGIC ; SIGNAL Extern, Ain, Gin, Gout, FRin : STD_LOGIC ; SIGNAL Count, Zero, T, I : STD_LOGIC_VECTOR(1 DOWNTO 0) ; SIGNAL R0, R1, R2, R3 : STD_LOGIC_VECTOR(7 DOWNTO 0) ; SIGNAL A, Sum, G : STD_LOGIC_VECTOR(7 DOWNTO 0) ; SIGNAL Func, FuncReg, Sel : STD_LOGIC_VECTOR(1 TO 6) ; BEGIN Zero <= "00" ; High <= '1' ; Clear <= Reset OR Done OR (NOT w AND NOT T(1) AND NOT T(0)) ; counter: upcount PORT MAP ( Clear, Clock, Count ) ; T <= Count ; Func <= F & Rx & Ry ; FRin <= w AND NOT T(1) AND NOT T(0) ; functionreg: regn GENERIC MAP ( N => 6 ) PORT MAP ( Func, FRin, Clock, FuncReg ) ; I <= FuncReg(1 TO 2) ; decX: dec2to4 PORT MAP ( FuncReg(3 TO 4), High, X ) ; decY: dec2to4 PORT MAP ( FuncReg(5 TO 6), High, Y ) ; controlsignals: PROCESS ( T, I, X, Y ) BEGIN … con’t 71 Alternativa para o código do processador - continuação Extern <= '0' ; Done <= '0' ; Ain <= '0' ; Gin <= '0' ; Gout <= '0' ; AddSub <= '0' ; Rin <= "0000" ; Rout <= "0000" ; CASE T IS WHEN "00" => -- no signals asserted in time step T0 WHEN "01" => -- define signals asserted in time step T1 CASE I IS WHEN "00" => -- Load Extern <= '1' ; Rin <= X ; Done <= '1' ; WHEN "01" => -- Move Rout <= Y ; Rin <= X ; Done <= '1' ; WHEN OTHERS => -- Add, Sub Rout <= X ; Ain <= '1' ; END CASE ; WHEN "10" => -- define signals asserted in time step T2 CASE I IS WHEN "10" => -- Add Rout <= Y ; Gin <= '1' ; WHEN "11" => -- Sub Rout <= Y ; AddSub <= '1' ; Gin <= '1' ; WHEN OTHERS => -- Load, Move END CASE ; WHEN OTHERS => -- define signals asserted in time step T3 CASE I IS 72 Alternativa para o código do processador - continuação WHEN "00" => -- Load WHEN "01" => -- Move WHEN OTHERS => -- Add, Sub Gout <= '1' ; Rin <= X ; Done <= '1' ; END CASE ; END CASE ; END PROCESS ; reg0: regn PORT MAP ( BusWires, Rin(0), Clock, R0 ) ; reg1: regn PORT MAP ( BusWires, Rin(1), Clock, R1 ) ; reg2: regn PORT MAP ( BusWires, Rin(2), Clock, R2 ) ; reg3: regn PORT MAP ( BusWires, Rin(3), Clock, R3 ) ; regA: regn PORT MAP ( BusWires, Ain, Clock, A ) ; alu: WITH AddSub SELECT Sum <= A + BusWires WHEN '0', A - BusWires WHEN OTHERS ; regG: regn PORT MAP ( Sum, Gin, Clock, G ) ; Sel <= Rout & Gout & Extern ; WITH Sel SELECT BusWires <= R0 WHEN "100000", R1 WHEN "010000", R2 WHEN "001000", R3 WHEN "000100", G WHEN "000010", Data WHEN OTHERS ; END Behavior ; 73 Um circuito reaction-timer DD c9 DD c1 c0 RL Clock 10-bit counter (a) Clock divider V LED (b) LED circuit 74 Um circuito reaction-timer VDD VDD RL R a b w 0 1 c9 1 D g a b g Converter Converter w0 w1 w2 w3 w0 w1 w2 w3 BCD1 BCD0 Q Q E Two-digit BCD counter Reset Clear (c) Push-button switch, LED, and 7-segment displays 75 Código para contador BCD de dois dígitos LIBRARY ieee ; USE ieee.std_logic_1164.all ; USE ieee.std_logic_unsigned.all ; ENTITY BCDcount IS PORT ( Clock : IN STD_LOGIC ; Clear, E : IN STD_LOGIC ; BCD1, BCD0 : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END BCDcount ; ARCHITECTURE Behavior OF BCDcount IS BEGIN PROCESS ( Clock ) BEGIN IF Clock'EVENT AND Clock = '1' THEN IF Clear = '1' THEN BCD1 <= "0000" ; BCD0 <= "0000" ; … con’t 76 Código para contador BCD de dois dígitos ELSIF E = '1' THEN IF BCD0 = "1001" THEN BCD0 <= "0000" ; IF BCD1 = "1001" THEN BCD1 <= "0000"; ELSE BCD1 <= BCD1 + '1' ; END IF ; ELSE BCD0 <= BCD0 + '1' ; END IF ; END IF ; END IF; END PROCESS; END Behavior ; 77 Código para o reaction timer LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY reaction IS PORT ( c9, Reset w, Pushn LEDn Digit1, Digit0 END reaction ; : IN : IN : OUT : BUFFER STD_LOGIC ; STD_LOGIC ; STD_LOGIC ; STD_LOGIC_VECTOR(1 TO 7) ) ; ARCHITECTURE Behavior OF reaction IS COMPONENT BCDcount PORT ( Clock : IN STD_LOGIC ; Clear, E : IN STD_LOGIC ; BCD1, BCD0 : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END COMPONENT ; COMPONENT seg7 PORT ( bcd : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ; leds : OUT STD_LOGIC_VECTOR(1 TO 7) ) ; END COMPONENT ; SIGNAL LED : STD_LOGIC ; SIGNAL BCD1, BCD0 : STD_LOGIC_VECTOR(3 DOWNTO 0) ; … con’t 78 Código para o reaction timer (continuação) BEGIN flipflop: PROCESS BEGIN WAIT UNTIL c9'EVENT AND c9 = '1' ; IF Pushn = '0' THEN LED <= '0' ; ELSIF w = '1' THEN LED <= '1' ; END IF ; END PROCESS ; LEDn <= NOT LED ; counter: BCDcount PORT MAP ( c9, Reset, LED, BCD1, BCD0 ) ; seg1 : seg7 PORT MAP ( BCD1, Digit1 ) ; seg0 : seg7 PORT MAP ( BCD0, Digit0 ) ; END Behavior ; 79

Baixar