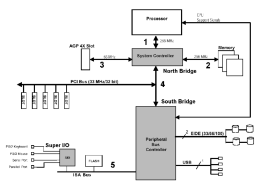

PSO800 e PXO400 Descrição do Hardware Apresentação • Serviço de voz no PC • Integração com rede PSTN • 4 ou 8 interfaces FXO • Interface PCI 32bits/33Mhz 3.3V/5V r2.2 Apresentação PXO400 PSO800 Blocos principais Circuito de Proteção • TVS para proteção entre TIP e RING na placa-base(Não Montado) • TVS para proteção de TIP e RING para GND na placa-base • Centelhador tripolar entre TIP, RING e GND na placa-base • Filtro de modo comum entre TIP e RING no módulo FXO (Não montado) Filtro “bead” no TIP e no RING Circuito de Proteção Módulo FXO • CODEC para conversão D/A • Circuito DAA para linha analógica • Detecção de gancho •Detecção de ring • Detecção de tons por hardware • Interface de controle via SPI Módulo FXO – PS0400 SI3050 SI3019 Módulo FXO – PS0400 Driver-PSO800/PXO400 LINUX ASTERISK libsupertone libsupertone ZAPTEL DRIVER HW-PSO800 Sistema Operacional Aplicação Responsável por gerar e detectar tons Driver do Asterisk que controla o HW(PSO800) Interface de configuração do HW (Canais FXO) Não faz parte do Asterisk. Permite o sistema operacional comunicar-se com hardware (“seta” valores elétricos para interface de linha) Zaptel – Arquivo zaptel.conf fxsks=1 # Aqui especificamos o número de portas fxo, no caso 1. Notem que ao invés de usarmos fxoks=1 para placa fxo, usamos o contrário fxsks=1. Se tivéssemos uma placa fxs esse parâmetro ficaria fxoks=1 loadzone=br defaultzone=br # Aqui definimos a zona onde a placa irá ser instalada. Carrega o HW PSO800 com os valores de característica de linha padrão Brasil. Implementações no Driver •Ganho de RX (importante para detecção de chamada em PABX) •Ajuste no nível de tensão de detecção de ring •Impedância de linha(600/900) •Identificação DTMF (passa os MF's na hora correta. Não faz o caller id, quem faz a identificação é o asterisk). FPGA – Configuração • Componente volátil • Precisa ser configurado a cada power-on • Memória flash armazena configuração • Flash gravada via JTAG • FPGA envia clock, flash envia dado • LED acende quando carga é concluída FPGA – Configuração FPGA • Lógica programável com várias funções • Framer: geração de frames para CODECs • Geração de chip selects para CODECs • Interface SPI para configuração dos CODECs • Bufferização dos time-slots • Geração e contagem de IRQs • Interface com o PLX FPGA – I/O Interface PCI • Conexão da placa PSO800 com o PC • Interface implementada pelo PLX9030 • Funciona como um bridge • Escravo para o barramento PCI • Mestre para o barramento local Interface PCI Interface PCI • BIOS (mother board)faz as primeiras configurações: Mapeamento no espaço de endereçamento; Definição de qual IRQ será usada. Driver executa as demais configurações Interrupção da FPGA mapeada para IRQ Interface PCI • PLX faz a interface com a E2PROM • E2PROM armazena número serial Reguladores de tensão • Tensões geradas a partir dos 5V da PCI • FPGA precisa de 3.3V, 2.5V e 1.2V • Demais componentes: 3.3V • U6 gera 3.3V a partir do 5V • U7 gera 2.5V a partir do 3.3V • U8 gera 1.2V a partir do 3.3V

Baixar