Licenciatura em Engenharia Informática e Computação Exercícios Arquitectura de Computadores 2005/06 Organização de microprocessadores (II) N. 6 FEUP 1. [Implementações uniciclo e multiciclo] Suponha que alguém sugeria eliminar o sinal MemtoReg. O multiplexador controlado por este sinal passaria a ser controlado por MemRead. Considere o efeito da mudança nas duas implementações. O CPU ainda funcionaria correctamente? Porquê? 2. [Desempenho de CPU] Considere as seguintes três versões de um CPU : C1: Implementação multiciclo normal com F = 4 GHz. C2: Implementação multiciclo semelhante à anterior, mas com a seguinte diferença: actualizações de registos são efectuadas no mesmo ciclo que as leituras de memória ou operações da ALU. Assim, os estados 6 e 7 são combinados num único; o mesmo acontece com os estados 3 e 4. Para esta implementação, F = 3,2 GHz. C3. CPU parecido com C2, mas com o cálculo do endereço efectivo a ser feito no mesmo ciclo que o acesso a memória. Assim, os estados 2, 3 e 4 são combinados num único. O mesmo acontece com os estados 2 e 5, bem como 6 e 7. Para esta implementação, F = 2,8 GHz. Usando a distribuição de instruções indicada na tabela, determine qual é o computador mais rápido (em MIPS). Existem outras possíveis distribuições de instruções que permitissem a outro dos computadores ser o mais rápido? Quais? Classe Tipo R Load Store Saltos Taxa de ocorrência 47% 25% 13% 15% 3. [Pipeline] A tabela mostra o tempo de execução de cada uma das unidades do percurso de dados estudado nas aulas. Unidade Tempo de atraso (ps) Mem instr. Banco de reg. ALU Mem. dados 200 100 200 200 a) Suponha que o tempo de execução da ALU é encurtado de 25%. Esta alteração afecta o desempenho da "pipeline"? Em caso afirmativo, determine a alteração de desempenho. b) Responda à questão anterior, supondo que o tempo de execução da ALU aumenta 25%. Arquitectura de Computadores 1/2 2005/06 4. [Desempenho de pipelines] Um engenheiro de computadores necessita de projectar um caminho de dados para um novo processador. Para avliação do desempenho usa um programa de aferição com 10 6 instruções. Cada instrução demora 100 ps. a) Quanto tempo demora a execução do programa num processador sem pipeline? b) Um CPU actual tem cerca de 20 andares de pipeline. Assumindo que a pipeline funciona em condições ideais, que melhoria de desempenho pode ser obtida (por comparação com a situação da alínea anterior)? c) Na realidade, a implementação de pipelines introduz sempre algum overhead por andar. Este overhead afecta a latência ou o débito das instruções (ou ambos)? Porquê? 5. [Desempenho de pipelines / forwarding] Uma rotina com 103 instruções tem o seguinte formato: "lw, add, lw, add, ..." A instrução de soma depende apenas da instrução lw imediatamente anterior. Cada instrução lw depende apenas da instrução de soma imediatamente anterior. O programa deve ser executado pelo caminho de dados com pipeline apresentado nas aulas. a) Determine o CPI do CPU para esta rotina? b) Qual seria o CPI obtido na ausência de forwarding? Fim. Arquitectura de Computadores 2/2 2005/06

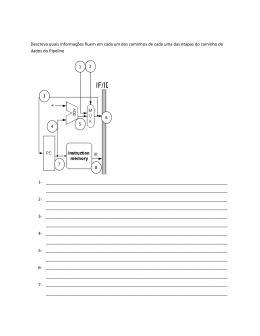

Baixar