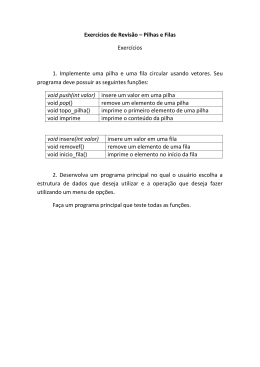

UNIVERSIDADE FEDERAL DE LAVRAS DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO RELATÓRIO FINAL DE PROJETO DE PESQUISA FAPEMIG PROJETO CEX 2832/97 DESENVOLVIMENTO DE UMA UNIDADE PROCESSADORA DISCRETA MICROPROGRAMÁVEL Coordenador: Prof. Wilian Soares Lacerda Lavras, outubro de 2001 RESUMO Este é o relatório final do projeto de pesquisa intitulado "Desenvolvimento de uma Unidade Processadora Discreta Microprogramável", financiado pela FAPEMIG (processo CEX2832/97), iniciado em 05/10/2000 e encerrado em 04/10/2001. Neste documento é apresentado os resultados do projeto, bem como as etapas para o seu desenvolvimento. Inicialmente, é apresentado o processador desenvolvido detalhadamente, tendo como base o estudo bibliográfico do assunto. Em seguida, é mostrado a metodologia e materiais utilizados para a implementação do processador. Finalmente é apresentado exemplos de utilização do processador, provando a eficiência do protótipo desenvolvido. 2 ÍNDICE 1 - Introdução....................................................................................................................4 2 - Objetivo........................................................................................................................7 3 - Proposição....................................................................................................................8 3.1 - Componentes da CPU..........................................................................................13 3.2 - Unidade de dados.................................................................................................14 3.3 - Unidade de controle.............................................................................................18 3.4 - Funcionamento da CPU ......................................................................................21 4 - Metodologia e materiais ............................................................................................23 4.1 - O Hardware .........................................................................................................24 4.2 - Os Softwares ........................................................................................................25 4.2.1 - O Software de Comunicação .........................................................................26 5 - Resultados ..................................................................................................................33 6 - Conclusão...................................................................................................................34 Agradecimentos ..............................................................................................................34 Referências Bibliográficas ..............................................................................................35 Propostas de continuidade..............................................................................................36 ANEXOS: ANEXO A - Esquemas de projeto da CPU ANEXO B - Resultados da simulação da CPU ANEXO C - Esquema da placa ISA ANEXO D - Arquivos de configuração das PAL's ANEXO E - Layout da placa ISA ANEXO F - Datasheet da CPLD ANEXO G - Listagem do software 3 1 - INTRODUÇÃO Atualmente, os computadores digitais fazem parte do nosso cotidiano. Nós os utilizamos desde para extrair um saldo bancário, até mesmo para aquecer alimentos em um forno microondas. A cada dia que passa, o computador se torna mais importante para nós, na medida em que a sua tecnologia avança, tornando-o mais acessível para todos. O "cérebro" do computador é o processador digital (CPU). Este elemento é responsável pela execução das tarefas pré-programadas no computador. Todos os outros componentes do computador (memória, periféricos de entrada, periféricos de saída) dependem do processador para funcionar. O processador coordena e gerencia todos os componentes do computador. Observe a Figura 1.1. CPU Portas de I/O MEMÓRIA Controlador de DMA Figura 1.1: Componentes de um computador Segundo Tokheim [12], “Em relação à Eletrônica, o estudante de hoje ou o especialista de amanhã deve ter um conhecimento de microprocessadores e de sistemas baseados em microprocessadores. Isto inclui conhecimentos tanto em software como de hardware. O microprocessador é a base de toda uma linguagem de máquinas e dispositivos inteligentes. O microprocessadores serão encontrados em diversos produtos: de brinquedos a processadores de palavras; de computadores de bolso a eletrodomésticos; de robôs industriais a termostatos. Com o advento de microprocessadores microprogramáveis espera-se no futuro uma aceleração do desenvolvimento das máquinas inteligentes. ” Nosso cotidiano está sendo tomado cada vez mais por máquinas inteligentes, e para desenvolvimento de máquinas mais velozes e mais eficientes temos que ter um conhecimento básico de como a informação é processada por essas máquinas. 4 Segundo Stalling [9], a organização básica de um sistema de computador constitui-se de Unidade Central de Processamento conectada aos barramentos de dados, endereços e controle, como ilustrado na Figura 1.2. Figura 1.2: Organização básica de um computador A estrutura é o caminho pelo qual os componentes são relacionados e a função é operar cada componente individualmente como parte da estrutura. Operações básicas em um computador: • Processamento de dados; • Armazenamento de dados; • Transferência de dados; • Controle. A estrutura deve compor-se de 4 componentes: • Unidade Central de Processamento (CPU); • Memória Principal; • I/O – Transfere dados entre o computador e o meio externo; • Sistema de comunicação. A parte mais complexa do processador (CPU) é a sua unidade de controle responsável pela geração dos sinais de sincronismo de todos os circuitos do processador. Na literatura [13][4] temos descrito várias soluções para implementação da unidade de controle. Algumas técnicas permitem que a unidade de controle seja mais versátil para modificações e ampliação, como a técnica de microprogramação. Hennessy e Patterson [7] descrevem em suas obras detalhes para projeto de processadores mais rápidos, utilizando técnicas de pipeling. O projeto do processador se torna 5 bem mais complexo, para se conseguir este objetivo. No protótipo desenvolvido, esta técnica não foi utilizada por dificuldades de implementação. A compactação das arquiteturas de computadores atuais e a velocidade com que as informações são processadas, dificulta a visualização e o entendimento do seu funcionamento. Com o Desenvolvimento da Unidade Processadora Microprogramável, que possui uma arquitetura simples e onde a velocidade e a compactação dos circuitos não são itens essenciais, é possível verificar e entender como as informações são processadas. Com o protótipo em funcionamento, torna-se possível este entendimento básico de processamento e muitos caminhos poderão ser abertos para o desenvolvimento de outras arquiteturas com tecnologias mais avançadas, pois o requisito básico já foi fixado. 6 2 - OBJETIVO O presente projeto tem como meta os seguintes objetivos: • Estudo das técnicas de arquitetura para processador digital. • Desenvolvimento de um protótipo de processador digital. • Implementação de outras técnicas de arquitetura de processadores digitais. • Testes de novas técnicas de arquitetura. • Divulgar o estudo e pesquisa na área de arquitetura de processadores digitais dentro e fora do departamento. • Formar uma equipe de pesquisa no departamento para atuar na área de arquitetura de processadores e computadores. • Propor novas pesquisas na área de projetos e desenvolvimentos de arquitetura de processadores e computadores. 7 3 - PROPOSIÇÃO A Unidade Processadora Discreta Microprogramável é um protótipo desenvolvido dentro do estudo de várias arquiteturas de processadores digitais. Neste estudo observou-se que a maioria das arquiteturas segue a arquitetura dos primeiros computadores eletrônicos, ou seja, na Arquitetura de von Neumann [10]. O objetivo do projeto baseia-se no desenvolvimento de um protótipo de um microprocessador com uma arquitetura simples e de fácil entendimento, para o desenvolvimento de tecnologias mais avançadas. Na Figura 3.1 apresentamos blocos com as partes básicas que constituem o protótipo do microprocessador. Observa-se que o processador gerencia todos os componentes externos (portas de entrada /saída e memória). Figura 3.1: Componentes que constituem o protótipo do microprocessador Em geral, o computador básico constitui-se de 3 partes: Unidade Central de Processamento (CPU), Portas de Entrada /Saída e Memórias. A CPU contém elementos de armazenamento (registradores), circuitos computacionais representado pela Unidade Lógica Aritmética (ULA), Circuitos de Controle e Temporização. As funções primárias da CPU são: • Buscar, decodificar, e executar instruções do programa armazenado na memória; • Transferir dados da e para memória e para portas de entrada e saída; • Prover os sinais de controle e temporização para todo o sistema. A Unidade Lógica Aritmética da CPU executa operações como somar, deslocar, rodar, comparar, incrementar, decrementar, negar, AND, OR, XOR, complementar e zerar. Para a 8 execução de uma operação de soma, a ULA utiliza dois registradores (Acumulador e Temporário). O conteúdo do Acumulador é somado com o conteúdo do registrador temporário e o resultado é enviado ao acumulador. De grande importância para o programador é o registrador de código de condição dos flags. Os flags incluem indicadores de zero, de resultado negativo, de vai-um, etc. Os flags são usados para tomadas de decisão quando posteriormente, se usam instruções de desvio. Os registradores temporário e acumulador podem ser considerados parte da ULA. A seção de CONTROLE E TEMPORIZAÇÃO é a parte mais complexa e afeta todos os eventos da CPU no microcomputador. Cada instrução do programa pode ser dividida em estágios de busca, decodificação e execução. Esses pequenos estágios ainda podem ser subdivididos em outros passos que podem ser chamadas de microprograma. O microprograma para cada instrução reside na seção de decodificação de instruções e é executado pela seção de controle e temporização da CPU. A sequência de busca-decodificação-execução de instrução é fundamental para a operação do computador. A primeira instrução buscada da memória de programa é tomada como sendo o código de operação da primeira instrução e é colocada no registrador de instruções pela seção de controle da CPU. O código, é então, interpretado pelo decodificador de instrução. O decodificador de instruções identifica o microprograma que a seção de controle e temporização deve seguir para executar uma instrução específica. Existe um conjunto de instruções que o microprocessador pode executar. As instruções podem ser classificadas de diversas maneiras: • Instruções aritméticas • Instruções lógicas • Instruções de transferência de dados • Instruções de desvio • Instruções de chamada de sub-rotina • Instruções de retorno • Instruções de pilha Nas instruções aritméticas temos: • Somar, Somar com vai -um, • Subtrair, Subtrair com vai-um , Empréstimo 9 • Incrementar • Decrementar • Comparar • Negar Nas instruções lógicas temos: • AND • OR • XOR • NOT Nas instruções de transferência e dados temos: • Carregar • Armazenar • Mover • Zerar Nas instruções de desvio temos: • Desvio Incondicional • Desvio de zero • Desvio se não zero • Desvio se igual • Desvio se desigual • Desvio se positivo • Desvio se negativo Nas instruções de pilha temos: • Empilhar • Desempilhar 10 Uma unidade central de processamento, ou CPU, é o principal componente dos computadores digitais. É a parte do computador responsável pela manipulação e transformação dos dados ou informações [4][5]. Desde o primeiro computador digital, até hoje, é utilizado no projeto do processador a topologia denominada arquitetura de von Newmann. O que diferencia a arquitetura dos atuais processadores são a tecnologia de fabricação, velocidade de processamento, complexidade do projeto, dentre outras [6]. Este projeto propõe o projeto de uma CPU simples, que contém as características básicas de um processador digital. D7..D0 A7..A0 CLOCK /MEM /IO /RESET /WR /RD Figura 3.2: A unidade central de processamento proposta A CPU proposta neste projeto possui a seguinte estrutura externa básica, mostrada na Figura 3.2. Os sinais de entrada e saída da CPU proposta possuem as seguintes funções e características: • D7..D0 – Barramento de dados externo (8 bits) • A7..A0 – Barramento de endereço (8 bits) • /MEM – sinal de habilitação da memória, ativa em nível zero • /IO – sinal de habilitação da porta de entrada/saída, ativa em nível zero • /WR – indica ciclo de escrita em porta ou memória, ativa em nível zero • /RD – indica ciclo de leitura em porta ou memória, ativa em nível zero • CLOCK – sinal de sincronismo • /RESET – sinal de inicialização, ativo em nível zero 11 A CPU não é o único componente de um computador. Existem circuitos auxiliares que em conjunto com a CPU formam um sistema de computador. Dentre estes circuitos, existe a memória e as portas de entrada/saída que são conectadas à CPU como é mostrado na Figura 3.3. D7..D0 MEMÓRIA A7..A0 /CS /WR /RD D7..D0 PORTA E/S S7..S0 /CS /WR /RD E7..E0 CPU D7..D0 CLOCK A7..A0 /MEM /RESET /IO /WR /RD Figura 3.3: Um sistema de computador com memória e porta entrada/saída A memória é responsável pelo armazenamento das instruções (ou comandos do processador) e dos dados. Uma memória, em geral, tem uma grande capacidade de armazenamento. Cada informação é armazenada em uma posição da memória que é identificada por um endereço (conjunto de bits). Através deste endereço, é possível recuperar a informação armazenada na memória. As portas de entra/saída são circuitos que permitem a troca de informações entre o computador e o ambiente externo. As portas de entrada enviam dados gerados por circuitos externos para a CPU, que por sua vez pode armazená-los na memória. As portas de saída permitem que a CPU transmita dados para circuitos externos. Para permitir a comunicação da CPU com os circuitos auxiliares, a própria CPU gera os sinais responsáveis pelo controle da memória e das portas de E/S. Os sinais de controle da memória são: • /MEM – habilita a memória para leitura ou escrita, ativo em zero. • /RD – habilita leitura, ativo em zero. • /WR – habilita escrita, ativo em zero. 12 Os sinais de controle da porta de entrada/saída são: • /IO – habilita leitura ou escrita da porta, ativo em zero. • /RD – habilita leitura, ativo em zero. • /WR – habilita escrita, ativo em zero. 3.1 - COMPONENTES DA CPU Para facilitar o projeto e estudo da CPU, ela é dividida internamente em duas unidades fundamentais: • Unidade de dados • Unidade de controle Estas unidades componentes funcionam em conjunto e conectadas entre si. Elas podem ser visualizadas na Figura 3.4, onde se observa a ligação entre elas. A unidade de dados possui as seguintes funções: • Cálculos aritméticos • Funções lógicas • Manipulação de dados • Armazenamento temporário de dados • Recebimento de dados • Envio de dados A unidade de controle possui as seguintes funções: • Geração dos sinais de controle da unidade de dados • Geração dos sinais de controle externos • Sincronização dos sinais de controle • Inicialização do sistema • Geração do endereço de memória 13 • Busca e armazenamento das instruções e dados CPU Barramento de dados interno CLK Sinais de controle internos Unidade de dados Unidade de Controle Status da ULA (flags) /RESET Sinais de controle externos Barramento de dados externo Barramento de endereço Figura 3.4: Unidades da CPU 3.2 - UNIDADE DE DADOS A ULA (Unidade Lógica Aritmética) é a responsável pelas operações lógicas e aritméticas da CPU. A ULA proposta é mostrada na Figura 3.5 com os sinais de entrada e saída. Ela é capaz de realizar as operações descritas na Tabela 3.1, conforme o código da operação gerado pela unidade de controle. FLAGS 1o operando 4 8 Resultado 8 2o operando 8 4 /ULA operação Figura 3.5: ULA 14 Tabela 3.1: Código de operação da ULA Código Op. (binário) Resultado Símbolo 0000 Não faz nada NOP 0001 Soma (1o op. + 2o op.) ADD 0010 Subtrai (1o op. – 2o op.) SUB 0011 1o op. AND 2o op. AND 0100 1o op. OR 2o op. 0101 1o op. XOR 2o op. XOR 0110 Complementa 1o op. NOT 0111 1o op. + 1 INC 1000 1o op. - 1 OR DEC o 1001 Deslocamento 1 op. para direita de 1 bit SHR 1010 Deslocamento 1o op. para esquerda de 1 bit SHL 1011 Nega o 1o op. NEG A ULA é composta internamente por circuitos lógicos somadores, subtratores, deslocadores, e inversores para a realização da operação selecionada. Ela possui os seguintes sinais de entrada e saída: a) Entradas: • 8 bits do 1o operando • 8 bits do 2o operando • 4 bits do código de operação (vide tabela) • 1 bit de habilitação da ULA (ativa em zero) b) Saídas: • 4 bits de “flags”: carry-out, sinal (positivo, negativo), zero, overflow • 8 bits do resultado Se a ULA estiver habilitada, então nos 8 bits do resultado estará o resultado da operação, entre o 1o e 2o operandos, selecionada pelos 4 bits do código de operação. Os quatro sinais de flags identificam o status da ULA de acordo com o resultado obtido pela realização de uma operação. O flag de zero é ativado (colocado em nível lógico 1) 15 se o resultado possue todos os bits em zero. O flag de sinal é ativado se o resultado da ULA é um número negativo em complemento de dois (bit mais significativo do resultado em 1). O flag de carry-out é ativado se ocorre um vai-um no último bit do resultado. E finalmente o flag de overflow é ativado se o resultado da operação realizada pela ULA não é válido. A unidade de dados é composta de ULA, registradores, multiplexadores, buffers tristate e barramentos, conforme é mostrado na Figura 3.6. 8 CLK Registrador de Flags /RF 4 FLAGS 4 CLK ULA A C U M U L A D O R A 8 MUX B 4 /ULA operação 8 /LAC MAC 8 /CLR 8 BUFFER TRI-STATE 8 8 Barramento de dados interno 8 8 CLK A 8 /BAC BUFFER TRI-STATE DR 8 8 MUX /BDI BUFFER TRI-STATE Barramento de dados externo B /BDE MDR /LDR 8 Figura 3.6: Diagrama da unidade de dados Os registradores (acumulador, DR e flags) armazenam o dados temporariamente antes de serem manipulados. O acumulador também é utilizado para o armazenamento do resultado da operação realizada pela ULA. Estes registradores são compostos por flip-flops, onde cada flip-flop é capaz de armazenar um único bit. Os multiplexadores (MUX) são responsáveis pela seleção de um determinado dado que está em suas duas entradas (A e B). Isto permite a opção de escolha de um dado que será 16 disponibilizado na saída do multiplexador, de acordo com o sinal de controle gerado pela unidade de controle. Por exemplo, o registrador acumulador poderá receber um dado proveniente da saída da ULA ou um dado proveniente do barramento de dados interno. O buffers tri-state são simplesmente circuitos que conectam um dos dois dados de entrada na sua saída. Tem como função fazer com que a cada momento apenas um circuito coloque o dado no barramento. Desta forma, o barramento pode ser usado por vários circuitos sem perigo de provocar um curto-circuito. Os barramentos são simplesmente fios condutores por onde os sinais elétricos dos dados trafegam, sendo um fio para cada bit de dado. Os sinais de controle da unidade de dados, os quais provêm da unidade de controle, possuem as seguintes funções: • /ULA – habilita a ULA, ativo em zero • operação – (4 bits) seleciona a operação que a ULA realiza de acordo com a Tabela 3.1 • /RF – habilita a carga do registrador dos flags, ativo em zero, sensível a transição positiva do clock • MAC – seleciona o dado a ser armazenado no acumulador (0 – A, 1 – B) • /LAC – habilita a carga do acumulador, ativo em zero, sensível a transição positiva do clock • /BAC – habilita o buffer do acumulador para envio do dado ao barramento de dados interno, ativo em zero • MDR – seleciona o dado a ser armazenado no Registrador de Dados (0 – A, 1 – B) • /LDR – habilita a carga do Registrador de Dados, sensível a transição positiva do clock • /BDI – habilita buffer do Registrador de Dados para envio do dado ao barramento de dados interno, ativo em zero /BDE – habilita buffer do Registrador de Dados para envio do dado ao barramento de dados externo, ativo em zero 17 3.3 - UNIDADE DE CONTROLE A unidade de controle é composta pelo contador de programa, pelos registradores (de endereço e instruções) e circuito de controle. Isto é mostrado na Figura 3.7. A MUX 8 REGISTRADOR DE ENDEREÇO B 8 8 CLK CONTADOR DE PROGRAMA /LCP /ICP 8 MRE CLK /LRE /RESET 8 Barramento de dados interno 8 8 8 REGISTRADOR DE INSTRUÇÕES UNIDADE DE DADOS /LRI CLK 8 CONTROLE CLK FLAGS 12 CIRCUITO DE CONTROLE /RESET 4 Barramento de dados externo Barramento de endereço 8 /MEM /IO /RD /WR Figura 3.7: Unidade de controle com a unidade de dados Os componentes da unidade de controle possuem as seguintes características e funções: • Registrador de endereço – registrador de 8 bits, com controle de carga (/LRE) e sensível a transição positiva do clock. Tem como função armazenar o endereço da memória que está sendo acessado. 18 • Registrador de instruções – registrador de 8 bits, com controle de carga (/LRI) e sensível a transição positiva do clock. Tem como função armazenar o código da instrução buscada na memória, e que será executada. • Contador de programa – contador crescente de 8 bits, com controles de clear assíncrono (/RESET), incremento síncrono (/ICP), e carga síncrona (/LCP), sensível a transição positiva do clock. Tem como função indicar a posição de endereço de memória onde está armazenado a próxima instrução a ser buscada. • Circuito de controle – máquina sequencial que gera os sinais de controle para a unidade de dados, unidade de controle, porta de entrada/saída e para a memória, de acordo com o dado armazenado no registrador de instruções. Sensível a transição negativa do clock. A máquina sequencial permite que a CPU execute as instruções indicadas na Tabela 3.2. Os sinais de controle da unidade de controle são: • /LCP – habilita a carga do contador de programa, ativo em zero, sensível a transição positiva do clock. • /ICP – habilita a contagem (incremento) do contador de programa, ativo em zero, sensível a transição positiva do clock. • /RESET – limpa (zera) o contador de programa e inicializa o circuito de controle, ativo em zero, assíncrono. • MRE – seleciona o dado a ser armazenado no Registrador de Endereço. • /LRE – habilita a carga do Registrador de Endereço, ativo em zero, sensível a transição positiva do clock. • /LRI – habilita a carga do Registrador de Instruções, ativo em zero, sensível a transição positiva do clock. FLAGS - (4 bits) identifica o status da ULA 19 Tabela 3.2: Código de instruções Código Descrição Símbolo Instrução (hexadecimal) 00 Não faz nada NOP 08 Soma: ACC=ACC+M(X) ADD X 10 Subtração: ACC=ACC-M(X) SUB X 18 ACC=ACC and M(X) AND X 20 ACC=ACC or M(X) ORA X 28 ACC=ACC xor M(X) XOR X 30 Complementa ACC: ACC=/ACC NOT 38 ACC = ACC + 1 INC 40 ACC = ACC - 1 DEC 48 ACC = ACC/2 SHR 50 ACC = ACC*2 SHL 58 ACC = -ACC NEG 80 ACC = 0 CLR 88 ACC = M(X) LDA X 90 M(X) = ACC STA X A0 Pula incondicionalmente para posição X JMP X A8 Pula para posição X se ACC = 0 JEZ X B0 Pula para posição X se ACC positivo ou zero JGE X B8 Pula para posição X se ACC negativo JLZ X C0 Pula para posição X se houve vai-um JMC X C8 Pula para posição X se houve overflow JMO X D0 Lê a porta de entrada e armazena no ACC INP D8 Escreve o conteúdo de ACC na porta de saída OUT FF Pára o processamento HLT X – endereço de memória de 8 bits M - memória ACC – Registrador acumulador 20 3.4 - FUNCIONAMENTO DA CPU A CPU possui o funcionamento descrito a seguir. Inicialmente, o sinal de reset é ativado, fazendo o contador de programa começar com o valor zero. A CPU então está pronta para executar instruções armazenadas na memória, obedecendo dois ciclos de funcionamento: ciclo de busca da instrução (ciclo de fetch), e ciclo de execução. Ciclo de busca da instrução Após a ativação do sinal de reset, é carregado o valor do contador de programa no barramento de endereço. A memória é ativada para leitura, e seu dado é carregado no registrador de instruções. O contador de programa é incrementado automaticamente preparando para ler o próximo dado na memória. Ciclo de execução Após o ciclo de fetch, a instrução carregada é decodificada pelo circuito de controle que gera os sinais de controle em sequência para execução da instrução. Se um dado é buscado na memória na execução da instrução, o contador de programa é atualizado. Quando termina de executar a instrução, o ciclo de fetch é reiniciado com o novo valor do contador de programa. Circuito de controle O circuito de controle é a parte mais complexa da CPU. Existem várias formas para implementação do circuito de controle [13][4]: microprogramado, máquina de estado e contador de sequência. O método proposto é o contador de sequência por ser mais simples. Ele é mostrado na Figura 3.8 e descrito a seguir. 21 Vêm do registrador de Instruções 8 Decodificador de instruções CLK /RESET N O P T0 T1 T2 Contador Deslocador T T T . . . A D D S U B ... Circuito Combinacional H L T Vêm do registrador de Flags 4 Tn T ... Sinais de Controle internos e externos Figura 3.8: Circuito de controle O contador deslocador gera sinais sequenciais a cada pulso de clock (transição negativa) de acordo com as formas de onda mostradas na Figura 3.9. A sua função é marcar o tempo e ordem de ativação dos sinais de controle. O decodificador de instruções ativa a sua saída correspondente a instrução armazenada no registrador de instruções. O circuito combinacional gera os sinais de controle na sequência apropriada para busca da instrução (durante ativação de T0, T1 e T2), e posteriormente gera os sinais de controle para execução da correspondente instrução (durante ativação de T3 à Tn). T0 T1 T2 Tn ... ... ... ... ... ... ... ... Figura 3.9: Sinais gerados pelo contador deslocador 22 4 - METODOLOGIA E MATERIAIS Para a implementação do protótipo do processador proposto foi desenvolvido uma placa ISA (Industry Standart Architecture) para conexão em um computador IBM-PC compatível [3], que contém um CPLD (FLEX10K10©) do fabricante Altera Corporation (vide Anexo F). Por meio desta placa e dos arquivos de configuração do CPLD utilizado, é possível implementar vários circuitos digitais de maneira simples e eficiente através do computador, inclusive o projeto do processador desenvolvido. Os CPLD’s, Circuitos Lógicos Programáveis Complexos (Complex Programmable Logic Devices), seguem a tecnologia dos PLD’s. PLD’s, Dispositivos Lógicos Programáveis (Programmable Logic Devices), são circuitos integrados configuráveis pelo usuário, usados para implementar funções lógicas quaisquer [1]. Sendo assim, os CPLD’s são de arquiteturas mais complexas, mais eficientes e de maiores capacidades em comparação com os PLD’s. Os CPLD’s são fabricados com células RAM ou EEPROM que permitem a sua configuração. Para configurar os CPLD’s existem várias ferramentas (softwares) em computador que geram arquivos de programação, específicos de cada fabricante. Como exemplo tem-se o MAXPLUS© II do fabricante Altera Corporation [2]. Os sinais, ou dados, de configuração são transferidos ao CPLD por meio de memórias previamente gravadas, cabos para download, ou mesmo por um microprocessador. A configuração do CPLD pode ser refeita tantas vezes forem necessárias. O uso de um computador IBM-PC compatível para programar um CPLD torna o processo de configuração mais versátil e rápido, uma vez que os arquivos de programação podem ser gerados por software e transmitidos ao CPLD diretamente. Por isso doi utilizado tal recurso para a implementação desse hardware. Os arquivos de configuração são gerados pelo computador via software (MAXPLUS© II) e são transmitidos ao CPLD por meio do barramento ISA. Os sinais de configuração são gerados por um software de comunicação, desenvolvido em conjunto com a placa. Esse software utiliza de um arquivo de configuração para gerar os sinais corretamente para o hardware. 23 4.1 - O HARDWARE O hardware proposto utiliza o padrão de interfaceamento ISA para conexão a um computador IBM-PC compatível. Esta interface foi escolhida pela facilidade de implementação e facilidade de uso. O componente principal da placa, o CPLD FLEX10K10©, é conectado ao barramento ISA através de buffers. Foi adotado este componente devido ao seu baixo custo e simplicidade de configuração dentre os outros CPLD’s. A comunicação da placa com o computador é controlada por circuitos de controle e de decodificação implementados em circuitos PAL’s (vide Anexo D). O diagrama abaixo (Figura 4.1) mostra a estrutura do hardware proposto. No Anexo C é mostrado o esquema completo da placa. No Anexo E, é mostrado o layout da placa. INTERRUPÇÃO BUFFERS DECODIFICADOR CPLD I S A C O N E C T O E R S REGISTRADOR DE CONTROLE SINALIZAÇÃO Figura 4.1. Estrutura do Hardware Proposto O Barramento ISA é a interface entre o computador e o hardware proposto. Por ele é possível trocar dados e enviar sinais de controle aos blocos endereçáveis (Buffers e CPLD). O barramento também possibilita ao computador receber um sinal de interrupção diretamente do CPLD, otimizando a comunicação com a placa. O circuito Decodificador realiza a decodificação de endereços do Barramento ISA. Os sinais resultantes são enviados para o Registrador de Controle. O Registrador de Controle é o responsável pela geração e armazenamento dos sinais de controle do CPLD. Tal bloco ainda tem a função de controlar a leitura e a escrita de dados 24 entre o CPLD e o computador posteriormente à programação. O Registrador de Controle opera diretamente nos buffers de dados e nos sinais de configuração do CPLD. O circuito de Sinalização é composto por três LED’s ligados diretamente a alguns sinais provenientes do Registrador de Controle. Por meio dessa sinalização visual, tem-se uma idéia do andamento da programação do CPLD. O CPLD recebe toda a programação proveniente do barramento por meio dos Buffers de dados. Após a programação, ele está pronto para operar isoladamente ou em comunicação contínua com o PC através dos próprios Buffers de dados. Sua função dependerá estritamente do conteúdo do arquivo de programação recebido. Estão ligados diretamente ao CPLD três conectores para utilização externa: dois padrão DB25 fêmea e um padrão PS/2. Este conectores podem ser utilizados para entrada e/ou saída de dados digitais. 4.2 - OS SOFTWARES Para obter os arquivos de configuração do CPLD utilizado, é necessário utilizar o software do fabricante (MAXPLUS© II). O circuito digital do processador que se deseja implementar pode ser projetado pelo usuário do software em modo gráfico ou texto. No modo gráfico, são utilizados desenhos de portas lógicas conectadas. No modo texto é utilizado uma linguagem de descrição de hardware de um nível abstrato para um nível concreto, como o VHDL [8] por exemplo. O software se encarrega de compilar o projeto e gerar os arquivos necessários à programação do CPLD. Com o CPLD utilizado, é possível fazer uso de 7.000 a 31.000 portas lógicas com muitas combinações diferentes em um só circuito, representadas em um só arquivo de programação. O software de comunicação desenvolvido (Anexo G), por sua vez, transfere o arquivo de configuração para o CPLD por meio do barramento e buffers. Sinais de controle do barramento e do CPLD são gerados pelo software para esta função. O esquema abaixo (Figura 4.2) ilustra o processo. 25 MAXPLUS II SOFTWARE DE COMUNICAÇÃO COMPILADOR EDITOR Gráfico ou texto Arquivos de Configuração PLACA RECONFIGURÁVEL Sinais de Configuração Figura 4.2. Processo de Configuração do Hardware Após a programação, o CPLD está pronto para ser utilizado pelo usuário, conforme os dados do arquivo de configuração. 4.2.1 - O Software de Comunicação Para o desenvolvimento do Software de Comunicação foi realizada uma pequena modelagem objeto orientada no intuito de facilitar a sua construção. O objetivo foi fazer um software de interface simples para a programação da placa e que funcionasse com eficácia. A modelagem constitui-se basicamente do diagrama de classe e de fluxogramas das partes mais complexas ou mais importantes do software. A implementação foi realizada na linguagem C++, possibilitando a transcrição do modelo. Utilizando o compilador mingw32, versão 2.95.2, o executável foi gerado. Os testes foram realizados logo após a compilação e algumas correções foram necessárias até que o software funcionasse como desejado. A modelagem apresentada já apresenta as correções feitas. Diagrama de Classe O diagrama de classe permite a visualização da estrutura estática do software. Na Figura 4.3 está apresentado o software na íntegra representado nesse diagrama. 26 ifstream Detalhes não mostrados clChipProgramavel – static const TEndereco ENDERECO_nWS = 0x0301 – static const TEndereco ENDERECO_nCS = 0x0302 – static const TEndereco ENDERECO_nCONFIG = 0x0303 – static const TEndereco ENDERECO_nSTATUS = 0x0304 – static const TEndereco ENDERECO_CONF_DONE = 0x0305 – bool nWS – bool nCS – bool nCONFIG – bool nSTATUS – bool CONF_DONE – bool RDYnBSY – bool INIT_DONE – bool IO9_27 – bool IO11_29 – bool IO13_35 – bool IO15_37 – clBarra mentoISA barramento – clBufferLeituraControle bufferLC + void setnWS(void) + void resetnWS(void) + void setnCS(void) + void resetnCS(void) + void setnCONFIG(void) + void resetnCONFIG(void) + void setnSTATUS(void) + void resetnST ATUS(void) + bool getnST ATUS(void) + void setCONF_DONE(void) + void resetCONF_DONE(void) + bool getCONF_DONE(void) + bool getRDYnBSY(void) + bool getINIT_DONE(void) + bool getIO9_27(void) + bool getIO11_29(void) + bool getIO13_35(void) + bool getIO15_37(void) + static const unsigned int TAMANHO_DADO = 14750 clArquivoUPDM clPlacaUPDM – TDado* cabecalho – TDado* conteudo – const char* nome – unsigned int tamanho – unsigned int tamanhoConteudo – unsigned int tamanhoCabecalho – TStatus status + static const T Status CERTO =0 + static const T Status NAO_CRIADO = 1 + static const T Status TAM_MUITO_MAIOR = 2 + static const T Status POUCO_CONTEUDO = 3 + static const T Status CONT EUDO_DEMAIS = 4 + static const T Status TIPO_NOME_INVALIDO =5 + static const unsigned int TAM_VET_CONTEUDO = 16000 – clBufferEscritaDados bufferED – clChipP rogramavel chip – static const unsigned int TBASE =2 – static const unsigned int TIME_OUT = (unsigned int)(50000 / TBASE) – static const unsigned int TCF2WS = 5 – static const unsigned int TCFG =2 – static const unsigned int TCD2UM = 2 – static const unsigned int TCF2S T1 = 4 – static const unsigned int TWSP =1 – static const unsigned int TWS2B =1 – static const unsigned int TBUSY =2 principal – int status + principal(int argC, char** argV) + int getStatus(void) – void enviarMensagemArquivo(T Status estado, const char* nomeArquivo) – void enviarMensagemPlaca(T Sta tus estado) usa 1 1 usa 1 1 – T Status status + static const TStatus CERTO =0 + static const TStatus OCUPADA = 1 + static const TStatus ERRO_setCFG = 2 + static const TStatus ERRO_resetCFG = 3 + static const TStatus ERRO_BUSY_WS = 4 + static const TStatus ERRO_ST_WS = 5 + static const TStatus ERRO_ID_CD = 6 + static const TStatus ERRO_CD_TO = 7 + static const TStatus ERRO_NAO_ESPERADO =8 – void extrairCabecalho(void) – void extrairConteudo(void) – void atualizarStatus(void) + clArquivoUPDM(const char* nomeArquivo) + ~clArquivoUPDM(void) + TDado* getCabecalho(void) + TDado* getConteudo(void) + TStatus getStatus(void) + const char* getNome(void) + unsigned int getTamanho(void) + unsigned int getTamanhoCabecalho (void) + unsigned int getTamanhoConteudo(void) – void aguardar(unsigned int tempo) – void resetar(void) + clPlacaUPDM(void) +bool configurar(const unsigned int tamanhoDado, TDado* dadosConfig) +T Status getStatus(void) 1 1 clBufferLeituraDados – TDado dado – static const TEndereco ENDERECO = 0x0300 – clBarramentoISA barramento clBufferLeituraControle usa 1 1 clBufferEscritaDados – TDado dado – static const TEndereco ENDERECO = 0x0301 – clBarramentoISA barramento – TDado dado – static const TEndereco ENDERECO = 0x0300 – clBarramentoISA barramento + TDado& getDado(void) + void setDado(TDado& d) 1 1 usa 1 + T Dado& getDado(void) 1 clBarramentoISA 1 usa usa 1 – TDado dado – TEndereco endereco 1 +inlineTDado inportb(TEndereco end) +inlinevoid outportb(TEndereco end, TDado d) 1 usa Figura 4.3. Diagrama de Classe do Software de Comunicação 27 Através de representação de atributos e métodos, cada classe do diagrama de classe é construído. Os atributos são as variáveis, tipos e constantes da implementação. Os métodos são as funções e os procedimentos. A classe Principal é a classe que faz a chamada inicial de todo o processamento do programa. Ela é a responsável pelo interfaceamento entre o computador e o usuário. Através do método construtor principal, o programa faz os testes com os argumentos passados na linha de comando, cria o objeto da classe clArquivoUPDM e programa a placa usando um objeto da classe clPlacaUPDM. Eventuais mensagens de erro são enviadas através do objeto dessa classe via console, em linha de comando. A classe clArquivoUPDM é responsável pelos métodos de tratamento do arquivo a ser programado na placa. Ela herda a classe de tratamento de arquivos ifstream da biblioteca padrão do compilador mingw32. Os dados provenientes do arquivo de extensão .rbf, gerado pelo software MAXPLUS© II, são armazenados por essa classe no vetor conteudo; para tanto usa-se o método extrairConteudo. Alguns teste são processados para a previsão de possíveis erros que o usuário possa cometer ao usar a clArquivoUPDM. Através de status é possível obter o possível erro ocorrido e reportá-lo ao usuário, se necessário. A classe clPlacaUPDM contém o método configurar como sendo o principal. Essa é a classe responsável pela programação propriamente dita da placa. A configuração segue as recomendações que o fabricante do chip programável apresenta nos seus manuais. A elaboração de um fluxograma (Figura 4.4) colaborou com a construção do método configurar pois permitiu que se tivesse uma melhor visão do processamento a ser feito. Agregadas à clPlacaUPDM estão as classes clChipProgramavel e a classe clBufferEscritaDados, buffer usado para enviar as palavras de configuração ao chip. A classse clChipProgramavel foi criada para se acessar aos pinos de configuração do CPLD. Essa permite uma representação direta desses pinos de configuraçâo, aumentando a clareza do código e facilitando a construção do software. As constantes de endereço correspondem aos endereços para alcance dos pinos. Ela usa a classe clBarramentoISA para enviar os sinais de configuração ao hardware e a classe clBufferLeituraControle para ler os sinais de controle do chip. As classes clBufferLeituraDados, clBufferEscritaDados e clBufferLeituraControle usam a classe clBarramentoISA para operar. Suas funções são, respectivamente, ler os dados, escrevê-los e ler os dados de controle ou de configuração do chip programável. Cada qual acessa a placa através da classe clBarramentoISA, atribuindo o endereço apropriado. Por fim a classe clBarramentoISA, que faz a ligação do hardware com o software. Através dos métodos inportb e outportb, escritos em assembly, pode-se acessar a interface 28 ISA e os sinais provindos da mesma. Mas ela só opera em versões de sistemas operacionais que permitem o acesso direto à essa interface. Fluxogramas São vários os métodos elaborados nesse software, mas somente de alguns se teve a necessidade da modelagem em fluxogramas para facilitar a programação e a clareza do código. As Figuras 4.3, 4.4, 4.5 e 4.6 mostram esses fluxogramas. O método extrairConteudo, da classe clArquivoUPDM, lê o arquivo de configuração passado como parâmetro e guarda o seu conteúdo no vetor conteudo. O seu fluxograma, na Figura 4.4, mostra a sua realização. início sim tamanho > TAM_VET_CONTEUDO ?? não status ← TAM_MUITO_MAIOR alocar memória posiciona leitura de arquivo em 0 fim i←0 sim fim de arquivo? não ler palavra (1 byte) guardar no vetor em i tamanho ← i fim Figura 4.4. Fluxograma do Método extrairConteudo Para temporização dos tempos de programação em clPlacaUPDM usa-se o método aguardar. Tal método parte do princípio de que todo acesso à interface ISA dure no mínimo 2 microssegundos para executar. Sendo assim, como mostrado no fluxograma da Figura 4.6, cada iteração realizada em aguardar conta o tempo necessário de espera. 29 início nroIteracoes ← tempo/TBASE sim nroIteracoes <= 0? não nroIteracoes ← 1 sim nroIteracoes == 0? não blc.getDado() nroIteracoes-- fim Figura 4.6. Fluxograma do Método aguardar O método configurar, da classe clPlacaUPDM, configura a placa de acordo com os dados dos manuais do chip. Na Figura 4.5 o processo é ilustrado. 30 início resetar ativar nCONFIG sim nSTATUS ou CONF_DONE ativado? não desativar nCONFIG resetar aguardar (TCF2ST1 + TCF2WS) us status ← ERRO_set_CFG false sim nSTATUS ativado? não ativar CS resetar “inicialização do envio de dados” posPalavraCorrente ← 0 status ← CERTO enviaProxima ← true status ← ERRO_reset_CFG false não enviaProxima? sim enviar palavra na posicao posPalavraCorrente status ← ERRO_NÃO_ESPERADO ativar nWS false desativar nWS aguardar TW2B + TBUSY tempoEspera ← 0 sim RDYnBSY ativado? não status ← OCUPADA tempoEspera >= TIME_OUT? sim não enviaProxima ← false status ← ERRO_BSY_WS false status ← CERTO nSTATUS ativado? não não PosPalavraCorrente >= (tamanhoDado – 1)? sim enviaProxima ← false resetar status ← ERRO_ST_WS PosPalavraCorrente++ sim enviaProxima ← true false Figura 4.5.a. Fluxograma do Método configurar (parte 1) 31 continuação tempoEspera ← 0 tempoEspera < TIME_OUT? não sim não enviaProxima ← false CONF_DONE ativado? resetar sim tempoEspera++ status ← ERRO_CD_TO aguardar TCD2UM false INIT_DONE ativado? não enviaProxima ← false sim enviaProxima ← false status ← CERTO resetar true status ← ERRO_ID_TO false Figura 4.5.b. Fluxograma do Método configurar (parte 2) Os demais métodos são de entendimento mais simples, que podem ser vistos diretamente no código do programa. 32 5 - RESULTADOS O projeto do processador descrito no capítulo 3, foi implementado utilizando linguagem VHDL e seus componentes ligados por editor gráfico do software MAXPLUS II. No Anexo A são apresentados as listagens dos arquivos em VHDL e os desenhos gráficos. O projeto, no ambiente do software MAXPLUS II, foi compilado para implementação do circuito do processador na CPLD FLEX10K10. Em seguida o arquivo de configuração da CPLD foi transferido para a placa desenvolvida utilizando o software de comunicação. Imediatamente após a transferência do arquivo de configuração, a CPU desenvolvida estava operando, executando o programa exemplo em sua memória de programa também implementada na CPLD. Os resultados do processamento da CPU puderam ser visualizados na porta de saída da CPU. A CPU, bem como a memória e portas de E/S, foi simulada também utilizando o software MAXPLUS II. No Anexo B são apresentados as formas de onda dos resultados da simulação, quando a CPU executava o programa exemplo, provando a eficiência do projeto. 33 6 - CONCLUSÃO A Unidade Processadora Discreta Microprogramável apresentada neste relatório de pesquisa, mostrou-se simples, eficaz e robusta. Esta unidade contém a mesma arquitetura utilizada pelos mais modernos processadores digitais, porém de uma maneira simples. Assim é possível o seu entendimento e estudo de novas tecnologias de projeto. O uso dos softwares de edição, compilação e programação, combinado com o uso do hardware programável, permite que novas propostas de arquitetura de processadores possam ser testadas e implementados de maneira rápida e eficiente. Dentre as aplicações possíveis para a placa desenvolvida, além da implementação de novos propostas de arquiteturas de processadores (objetivo principal deste projeto de pesquisa), é possível a implementação de quaisquer circuitos digitais, desde que respeitado o limite de portas lógicas disponível na CPLD utilizada. AGRADECIMENTOS Ao Depto de Ciência da Computação da UFLA, pelo apoio dos professores e funcionários para o desenvolvimento do projeto. À FAEPE, pelo apoio à execução e acompanhamento do projeto de pesquisa. Agradecimento especial à FAPEMIG pelos recursos financiados para a execução do projeto e sem a qual seria improvável a realização do mesmo 34 REFERÊNCIAS BIBLIOGRÁFICAS [1] ALTERA CORPORATION. Data Book. San Jose, EUA: January 1998. 885p. [2] ALTERA CORPORATION. MAX+PLUS II: Getting Started. San Jose, EUA: September 1997. 353p. [3] EGGEBRECHT, Lewis C. Interfacing to the IBM Personal Computer. 2.ed. USA: Howard W. Sams and Company, 1990. 345p. [4] HAYES, John Patrick. Computer Architecture and Organization. Singapore: McGraw-Hill International, 2a edição, 1988, 702p. [5] LANGDON Jr, G. G. e FREGNI, E. Projeto de Computadores Digitais. Edgard Blucher Ltda, 1990. [6] MALVINO, A. Microcomputadores e Microprocessadores. McGraw-Hill, São Paulo, 1986. [7] PATTERSON, David A. e HENNESSY, John L. Computer Organization and Design: The Hardware/Software Interface. San Francisco: Morgan Kaufmann, 2a edição, 1998, 980p. [8] PERRY, Douglas. VHDL. 3.ed. New York, EUA: McGraw-Hill, 1998. 493p. [9] STALLINGS, WILLIAM. Computer Organization and Architecture – Designing for Performance. Fourth Edition. Prentice Hall, 1996. [10] TANEMBAUM, Andrew S. Organização Estruturada de Computadores. Rio de Janeiro: Livros Técnicos e Científicos, 1999, 3a edição, 460p. [11] TAUB, Herbert. Circuitos Digitais e Microprocessadores. Editora McGraw-Hill, São Paulo, 1984. 35 [12] TOKHEIM, L. R. Introdução aos Microprocessadores. MacGraw-Hill do Brasil, São Paulo, 1985. [13] ZUFFO, João Antônio. Fundamentos da Arquitetura e Organização dos Microprocessadores. Editora Edgard Blucher Ltda, São Paulo, 1978. [14] ZUFFO, João Antônio. Microprocessadores: Dutos de Sistema, Técnicas de Interface e Sistemas de Comunicação de Dados. Editora Edgard Blucher Ltda, São Paulo, 1981. PROPOSTAS DE CONTINUIDADE Propõe-se as seguintes idéias para continuação deste projeto: • Melhoria da unidade de dados do processador desenvolvido, utilizando registradores com ponteiros. • Utilização de uma CPLD com maior capacidade para implementação do processador. • Utilização de tipos de pipeline no projeto do processador. • Projeto de placa com barramento PCI, no lugar do barramento ISA. • Implementação da placa com memórias tipo RAM estática para economizar portas lógicas da CPLD. • Acréscimo do número de instruções do processador projetado, com maior complexidade. • Melhoria da ULA, implementando mais operações. • Utilização da placa para a implementação direta de algoritmos. Lavras, outubro de 2001 _______________________________ Wilian Soares Lacerda 36

Baixar