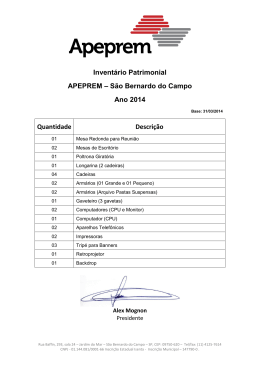

CPU (Central Processing Unit) 1 CPU UNIDADES FUNCIONAIS DE UM COMPUTADOR Como a CPU controla os outros subsistemas? 2 CPU ESTRUTURA INTERNA DO PROCESSADOR Quais são os barramentos básicos de comunicação necessários? 3 CPU • CONCEITO FUNDAMENTAIS " Instruções e dados armazenados na memória – Arquitetura de Von Neumann " Instruções ocupam posições sequenciais na memória " A CPU “sabe” a posição da próxima instrução a ser executada a partir do registrador PC – Program Counter " Um outro registrador especial, o IR – Instruction Register – informa à Unidade de Controle qual o código da instrução em execução BUSCA DE UMA INSTRUÇÃO IR [[PC]] PC [PC] + 1 Busca o conteúdo da posição de memória indicada por PC, colocando em IR e incrementa o conteúdo de PC Instrução que ocupa mais de uma palavra de memória? 4 CPU ESTRUTURA INTERNA DE UMA CPU DE BARRAMENTO SIMPLES Quais operações são necessárias entre os blocos para executar uma instrução? 5 CPU OPERAÇÕES TIPICAMENTE EXECUTADAS PELA CPU " Busca de palavra da memória 1. 2. 3. 4. MAR ß [R1] Leitura Espera o sinal MFC (Memory Function Completed) – Modelo Assíncrono R2 ß [MDR] " Armazenamento de palavra na memória 1. 2. 3. 4. MAR ß [R1] MDR ß [R2] Escrita Espera o sinal MFC (Memory Function Completed) – Modelo Assíncrono É possível realizar outras operações enquanto aguarda o sinal MFC? 6 CPU " Transferência entre Registradores Ø Os sinais in e out são emitidos pela UC para comandar as transferências Ø O sinal in comanda o registrador para que ele copie o conteúdo do barramento interno Ø O sinal out comanda o registrador para que ele coloque o seu conteúdo no barramento interno Quais ações são necessárias para transferir o conteúdo de R1 para R4? 7 CPU " Execução de instruções aritméticas e lógicas Ø Qual a sequencia de operações para adicionar o conteúdo do registrador R1 com o conteúdo do registrador R2 e armazenar o resultado no registrador R3? Quantas operações são permitidas com único barramento? 8 CPU " Execução de instruções aritméticas e lógicas (continuação) 1. R1out, Yin 2. R2out, Add, Zin 3. Zout, R3in " Controle dos registradores Quais são os três estados para o chaveamento? 9 CPU " Temporização das transferências de dados Por que R2 é desligado depois de Zin? 10 CPU EXECUÇÃO DE UMA INSTRUÇÃO COMPLETA " Instrução exemplo: Soma o conteúdo de uma posição de memória com o conteúdo do registrador R1 ADD (R3), R1 " Ações necessárias: Ø Busca da instrução Ø Busca do primeiro operando (“apontado” por R3) Ø Executar a adição Ø Carregar o resultado para R1 11 CPU " Sequência de controle para a execução de ADD (R3), R1 Passo Ação 1 2 3 4 5 6 7 PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin, R3out, MARin, Read Rlout, Yin, WMFC MDRout, Add, Zin Zout, Rlin, End 12 CPU " Instruções de desvio incondicional Passo 1 2 3 4 5 6 Ação PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin, PCout, Yin Offset-field-of-IRout, Add, Zin Zout, PCin, End 13 CPU " Instruções de desvio condicional (desvio se negativo) Passo 1 2 3 4 5 6 Ação PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin, PCout, Yin, If N = 0 then End Offset-field-of-IRout, Add, Zin Zout, PCin, End 14

Download