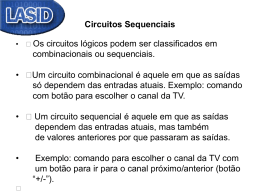

Aula 6 – Sumário Introdução Definição Latches aos circuitos sequenciais de circuito sequencial Circuitos sequenciais (básculas) Tipo SR Tipo SR com controlo Tipo D Flip-flops D Edge-triggered JK Edge-triggered 2 1 Circuitos Sequenciais Circuitos Sequenciais Definição: Modelo geral Um circuito diz-se sequencial quando os valores lógicos das saídas dependem não só dos valores das entradas, mas também do estado do circuito. Circuito sequencial Entradas Um circuito sequencial possui elementos de memória O estado do circuito corresponde aos valores lógicos armazenados nesses elementos de memória Saídas Lógica combinatória Estado actual Próximo estado Elementos de memória A mesma combinação de valores nas entradas pode originar valores diferentes nas saídas, em instantes de tempo diferentes. Latches e Flip-flops 3 Elementos de memória Latch 4 Latches ou báscula Vamos começar por analisar este circuito… Elemento básico que permite armazenar um bit de informação (guardar ‘0’ ou ‘1’) R (reset) Flip-flop S (set) Q QN R 1 0 0 0 S 0 0 1 0 Q 0 0 1 Tal como os latches, também armazena um bit de informação 1 tempo Para a combinação de entradas S=0 e R=0, os valores da saída são diferentes em instantes de tempo diferentes. E o armazenamento da informação é sincronizado com um sinal de referência Esta situação comprova que se trata de um circuito sequencial. 5 6 1 Latch SR Latch SR Sintetizando… Exemplo S R Qt+1 0 0 Qt Manter o mesmo estado 0 1 0 Reset (guardar ‘0’) 1 0 1 Set (guardar ‘1’) 1 1 0 Não se utiliza * de evolução temporal Obs. Reset Set R S Símbolo * Pode conduzir a um estado indefinido S Q Nota: Qt – significa estado actual Q ?? Q ?? R Inicialmente não se conhece o estado Qt+1 – significa estado seguinte Impossível de prever 7 Latch SR com controlo 8 Latch RS com controlo O latch SR com controlo tem uma variável adicional C. Só quando essa variável está activa é que se podem fazer operações como Set e Reset. S Q C Latch SR R Funcionamento Símbolo R Q C QN S S Portas de controlo C S R Qt+1 0 x x Qt Obs. Manter o mesmo estado 1 0 0 Qt Manter o mesmo estado 1 0 1 0 Reset 1 1 0 1 Set 1 1 1 - Não se utiliza Q Circuito equivalente com NANDs (implementação mais comum) C QN R 9 10 Latch D Flip-flops O latch D é obtido a partir de um latch SR com controlo, acrescentando uma negação entre as entradas S e R. Geralmente são compostos por 2 latches ligados em série e lógica adicional Permitem sincronizar o armazenamento da informação com as transições de um sinal de referência (Sinal de relógio ou Clock) Símbolo: D C S C R Q D C Q C 0 1 1 D Qt+1 x Qt 0 0 1 1 Circuito sequencial Entradas Estado actual Os latches D são usados como células de memória Sinal de relógio 11 Saídas Lógica combinatória Próximo estado Flip-flops 12 2 Flip-flop D edge-triggered D Clock D Q S C Q Flip-flop D edge-triggered Funcionamento (negative edge): Q C Q R Clock 0 D x 1 x 0 1 Um FF do tipo edge-triggered só guarda valores em Q quando ocorre uma transição no nível lógico do sinal de relógio (Clock) Símbolos: Qt+1 Qt Qt 0 1 Negative edge-triggered D Q Positive edge-triggered Nos instantes em que o sinal de relógio vai de ‘1’ para ‘0’, o valor que estiver na entrada D é guardado no flip-flop (passa para Q). O flip-flop D representado no esquema reage nos instantes em que Clock varia de ‘1’ para ‘0’ – FF D negative edge-triggered. D Q 13 14 Flip-flop JK edge-triggered Flip-flop JK Edge-Triggered Funcionamento (positive-edge) J Clock K D Q Clk Q Q J K Qt+1 0 0 Qt Manter o mesmo estado 0 1 0 Reset 1 0 1 Set 1 1 Qt Obs. Complementar o estado Símbolos: Um FF JK edge-triggered pode ser construído a partir de um FF D. J Possui duas entradas, J e K, que possibilitam mais operações do que o FF D. Positive edge-triggered Q J K Q Negative edge-triggered K 15 16 Tabelas de Funcionamento Flip-flop JK edge-triggered Sintetizando... Exemplo de funcionamento ao longo do tempo (positive edge) Flip-flop JK Flip-flop D Clock D Qt+1 0 0 1 1 J K Q D Q J K Qt+1 0 0 Qt 0 1 0 1 0 1 1 1 Qt J Q K tempo Set Reset Mantem o estado Troca o estado Mantem o estado Importantes para a análise e o projecto de circuitos sequenciais. Troca o estado 17 18 3 Diagramas de estado Entradas assíncronas Flip-flop D D=0 Flip-flop JK 1 D=1 0 1 JK=00,01 0 0 00,10 JK=10,11 1 Set – Inicializa a ‘1’; Reset ou Clear – Inicializa a ‘0’ Estas operações assíncronas são independentes do sinal de relógio e sobrepõem-se às restantes 01,11 J As “bolas” representam os estados As “setas” representam as transições de estados É frequente os FFs terem entradas assíncronas que permitem inicializar o estado: K a cada transição estão associados valores das entradas 19 Set Reset Q J K Q Clear 20 Flip-flops master-slave Os flip-flops master-slave são construídos com base em dois latches SR com controlo Tal como nos edge-triggered, os valores de Q só se actualizam em resposta a uma transição do sinal de relógio No entanto há uma diferença fundamental: Nos FF master-slave, para determinar o próximo estado é necessário ter em conta alterações aos valores das entradas durante todo o período de tempo em que o relógio está activo (por exemplo a ‘1’). Nos FF edge-triggered, para determinar o próximo estado apenas se consideram os valores das entradas no momento da transição do relógio 21 4

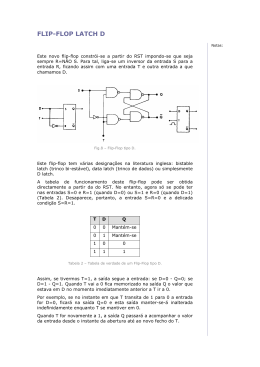

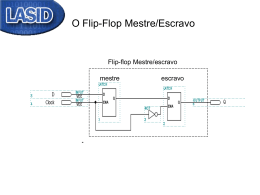

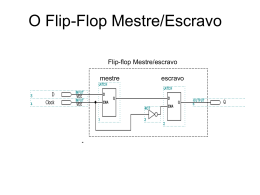

Baixar