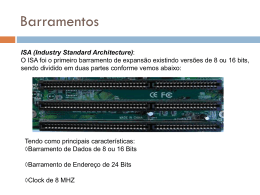

Arquitetura dos Microprocessadores 8086 e 8088 Sistemas Embarcados Introdução Microprocessadores Intel Primeira Geração 8086 8088 80186 Linha X86 Segunda Terceira Geração Geração 80286 Ano Surgimento 1978 1979 1982 1982 Nº bits barramento 16 8 16 16 Nº transistores 2900029000 100000 134000 4,77 a 4,77 a Vel. MHz 10 10 8 a 16 8 a 12,5 CoProcessador 8087 8087 8087 80287 Quarta Geração Linha Pentium Quinta Geração 80386 80486 Pentium 1985 1989 1993 32 32 32/64 375000 1200000 3100000 16 a 40 80387 25, 33 e 50 60, 66 e 90 80487 Interno Introdução Vamos concentrar nossos estudos no 8086/8088! Por que? Motivos históricos: o primeiro PC (o IBM PC) possuía um 8088 embarcado Todo software produzido para a família 80X86 mantém compatibilidade com os microprocessadores futuros Arquitetura do 8086/8088 Arquitetura Von Neumann (CISC): dados e endereço no mesmo barramento 20 bits de endereço => 1Mbyte 16 bits de dados do barramento comum (8086) 8/16 bits de dados do barramento comum (8088) Barramento de controle: 16 bits independentes do barramento comum 8086 e 8088 possuem arquiteturas internas semelhantes, com interfaces com o barramento diferentes! Pinagem do 8086/8088 Diagrama Funcional do 8086/8088 Quando uma instrução requer acesso à memória ou a um dispositivo periférico, então a EU solicita à BIU uma leitura/escrita de dados. EU obtém instruções de uma fila gerenciada pela BIU Unidade de Execução do 8086/8088 Contém uma ALU para realização de operações aritméticas (+,-,* e /) e lógicas (AND, OR, NOT e XOR) A ALU pode realizar operações de 8 ou 16 bits Contém registradores endereçados por nome para armazenamento temporário durante operações Unidade de Controle do 8086/8088 Controla a comunicação de dados entre a Unidade de Execução e os dispositivos periféricos (memória e E/S) Controla a transmissão de sinais de endereço, de dados e de controle Controla a sequência busca e execução instruções de de Mecanismo de pre-fetch: busca até 6 instruções futuras, deixando-as na fila de instruções => Aumento de velocidade Modos Máximo e Mínimo do 8086/8088 Modo Mínimo O processador gera todos os sinais de controle do barramento Não permite o uso de coprocessador Modo Máximo Alguns sinais de controle do barramento são gerados pelo 8286/8288 Permite o uso do coprocessador 8087 O 8086/8088 no Modo Mínimo O 8086/8088 no Modo Máximo Operação de Barramento Um esquema de multiplexação permite a utilização de um único barramento físico hora para endereçamento e hora para transmissão/recepção de dados (arquitetura Von Newman) Vantagem: uso eficiente do hardware disponível (minimização do hardware necessário) Desvantagem: lentidão no processo de transmissão/recepção de dados Temporização no Modo Mínimo Temporização no Modo Máximo Conjunto de Registradores De Uso Geral Uso Preferencial Usados em operações aritméticas de 8 ou 16 bits Usados em operações aritméticas e para acessar variáveis de memória. Conjunto de Registradores De Uso Específico Permite que a CPU possa acessar até 4 seguimentos distintos ao mesmo tempo Usados para particionamento de memória Cada segmento lógico possui 64kB Onde são usados? Algumas instruções usam certos registros implicitamente. IN AX,0C8h IN AX,DX OUT 0C8h,AX OUT DX,AX MUL CX => AX*CX ->resultado em DX:AX DIV CX => DX:AX/CX ->resultado: quociente em AL e resto em AX Segmentação da Memória As Famílias 8086/8088 e 80186/80188 possuem um espaço de memória de 1MB (de 00000h a FFFFFh) Um segmento (unidade lógica de memória) pode ter no máximo 64kB (de 0000h a FFFFh) Segmentação da Memória Os segmentos podem ser adjacentes, disjuntos, parcialmente sobrepostos ou completamente sobrepostos Uma memória física pode ser mapeada em um ou mais segmentos lógicos Segmentação da Memória Veremos em laboratório como podemos fazer o papel do sistema operacional e assim obter controle sobre os segmentos, alterando o valor dos registradores de segmento (DS, CS, SS e ES) Segmentação da Memória Segmentação da Memória O Seletor e o Descritor de segmento são controlados pelo sistema operacional O Offset é controlado pelo programa de aplicação Normalmente o Descritor de segmento possui alguns bits associados para determinação de características de proteção do segmento, isto é, permissões para leitura, escrita e/ou execução Um Cache de Descritor de segmento evita dois acessos simultâneos à memória Geração do Endereço Físico O endereço físico é um valor de 20 bits que identifica a localização de um byte na memória. Operação Realizada pela BIU Um eventual carry gerado pela adição é ignorado! Endereço Físico versus Endereço Lógico Endereço Lógico • O endereço lógico de memória pode vir de diferentes fontes, dependendo do tipo de referência que está sendo feito. • A BIU (Unidade de Interface de Barramento) é quem determina a fonte do endereço lógico com base no tipo de referência de memória . • Entretanto, o programador é capaz de direcionar a BIU para usar um segmento endereçável qualquer. Exemplo: MOV ax,1000h MOV ds,ax Endereço Lógico • As instruções são sempre buscadas no segmento de código corrente • O registrador CS possui a base do segmento, enquanto que o registrador IP possui o offset, formando, assim, o endereço lógico de uma instrução • Instruções de pilha sempre operam no segmento de pilha corrente • O registrador SS possui a base do segmento, enquanto que o registrador SP possui o offset que leva ao topo da pilha. Entretanto, o endereço lógico de uma instrução envolvendo a pilha usa o registrador BP para apontar a base da pilha. Implementação de Pilha • Um sistema pode possuir múltiplas pilhas, só uma é diretamente endereçável por vez através dos registradores SS e SP • Uma pilha pode ter até 64kB, sendo que SS determina a base e SP o topo • O ponto de origem da pilha é o topo (não a base) • As pilhas armazenam palavras de 16 bits • Portanto, para armazenar um elemento na pilha, deve-se decrementar SP de 2 (2 bytes), e então escrever a palavra em SP • Ao ler um elemento da pilha, deve-se incrementar SP de 2 • A pilha cresce em direção à sua base • Operações de pilha nunca movem ou apagam os elementos armazenados Implementação de Pilha Memória Reservada RESET Instrução JUMP Até 256 Interrupções distintas 16 bits de endereçamento de segmento 16 bits de endereçamento de offset Totalizando um apontador de 4 bytes Endereçamento de Entrada/Saída Operações de Entrada/Saída podem endereçar um máximo de 64k de registradores de 8 bits (1 byte) ou 32k de registradores de 16 bits (1 word) O endereçamento de Entrada/Saída apresenta o mesmo formato que o endereçamento de memória no barramento formado por A15-A0, porém com A19-A16 iguais a zero O registrador DX é usado como apontador de endereço de Entrada/Saída Interface Externa – Reset de Processador e Inicialização RESET = HIGH por um período superior a 4 CLK Todas as operações já em andamento no instante em que o RESET vai para nível alto são terminadas, permanecendo o processador em estado de espera logo após isso e enquanto RESET=HIGH A transição de RESET para nível baixo aciona uma sequência de resets internos por aproximadamente 10 CLKs Finalmente, executa-se a instrução no endereço FFFF0H Interface Externa – Reset de Processador e Inicialização RESET Instrução JUMP Interface Externa – Operações de Interrupção Existem duas classes de interrupções: de hardware e de software Interrupções de software são tratadas posteriormente quando falarmos dos conjuntos de instruções Interrupções de hardware são classificadas ainda como Não-Mascaráveis (NMI) ou Mascaráveis (INTR) Interface Externa – Operações de Interrupção Até 256 Interrupções distintas Interface Externa – Interrupção NãoMascarável (NMI) Interrupção NMI possui maior prioridade do que uma mascarável (INTR) Um uso típico de uma interrupção NMI seria para ativação de uma rotina para tratar uma falha de alimentação Interrupção NMI é ativada durante uma transição LOW-toHIGH, permanecendo HIGH por pelo menos 2 CLKs Interface Externa – Interrupção Mascarável (INTR) Interrupção INTR pode ser mascarada internamente via software, resetando o bit status FLAG Uma interrupção mascarável é ativada durante uma transição LOW-to-HIGH em INTR BUSCAR MAIS DETALHES! Conjunto de Registradores De Uso Específico SITUAÇÃO DE RESET CS inicializa em FFFFh SS, DS e ES inicializam em 0000h Programas podem acessar e manipular qualquer registrador de segmento Exemplo: DEBUG do DOS CS aponta para o Segmento de Código, onde há dinstruções a serem ->Comandos ee buscadas SS aponta para o Segmento de Pilha, usado para operações de colocar e/ou retirar dados da pilha DS aponta para o Segmento de Dados, onde normalmente estão armazenadas as variáveis de programa ES aponta para o Segmento Extra, tipicamente usado para armazenamento de dados Organização da Memória O 8086/8088 é um microprocessador little-endian! Registro de Flags Processor Status Word (PSW) 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 Os flags CF, PF, AF, ZF, SF e OF são alterados pela EU de acordo com resultados de operações lógicas ou aritméticas Os flags TF, IF e DF são usados para alterar operações do processador, podendo ser setados ou resetados O Reset inicializa o PSW como F000h

Baixar