Organização de Computadores

Paulo Maciel

Arquitetura de Computadores

Introdu₤₧o

Resumo Histórico

Componentes computador

Componentes de um

processador

Opera₤ões de um

processador

Sistema de Interconex₧o

Estruturas Estáticas e

Dinâmicas

Barramentos

Memória Interna

Memória Semicondutora

Memória Cache

Memória Externa

Disco Magn₫tico

CD-ROM

Fita Magn₫tica

Dispositivos de Entrada e Saída

I/O Programado

Tratado por Interrup₤₧o

DMA

Canais

SCSI

Arquitetura de Computadores

Suporte do Sistema Operacional

Vis₧o Geral de um Sistema

Operacional

Escalonamento

Gerenciamento de Memória

Unidade de Processamento

Componentes

Via de Dados

Unidade de Controle

Aritm₫tica

Controle Hardwired

Controle Microprogramado

RISC versus CISC

Arquitetura de Computadores

Arquitetura X86

Modos de opera₤₧o

Modelo de software

Descri₤₧o funcional

Opera₤ões sobre o

barramento

Pipelining

Processador Super-escalar

Previs₧o de desvio

Memória cache

Cache de instru₤₧o e de

dados

Unidade de Ponto Flutuante

Software

Modos de endere₤amento

de dados e programa

Instru₤ões

Introdu₤₧o à

programa₤₧o

Interrup₤ões

Classifica₤₧o

Processamento de

Interrup₤ões

Macroassembly

Programando com Servi₤os

do Sistema Operacional

Arquitetura de Computadores

Material Didático:

Computer Organization and Architecture

Autor: William Stallings

Editora : Prentice-Hall, Inc

The Pentium Microprocessosr

Autor - James L. Antonakos

Editora: Prentice-Hall, Inc.

Outros Livros

Computadores Mecânicos

Máquina de Pascal

Máquina Analítica

– Opera₤ões:Soma e

– Componentes:

Subtra₤₧o

– Manivela

» Armazenamento

» Engenho

» Se₤₧o de Entrada

» Se₤₧o de Saída

– Cartões Perfurados

– Charles Babbage (17921871)

– Ada Lovelace

Blaise Pascal (1623-1662)

Computador El₫trico

Advento da Energia El₫trica

Desenvolvimento da tecnologia

eletrot₫cnica

– dispositivos eletromagn₫ticos

– rel₫s

Automatiza₤₧o dos processos

mecânicos

Máquinas de Aiken

– Rel₫s

– Dígitos decimais

– Fita de papel perfurado

Computador Eletrônico

– Máquina Enigma

COLOSSUS (1943)

» 1° computador eletrônico

Alan Turing

1ª Gera₤₧o (1945-1955)

– ENIAC

» Tecnologia - Válvulas e rel₫s

» Arquitetura: 20 registradores

10 digitos decimais

» Programa₤₧o: Chaves

Jonh Mauchley

– UNIVAC

– IBM 7090

1ª Gera₤₧o (1945-1955)

EDSAC - Jonh von Neumann

– Tecnologia - Válvulas e rel₫s

– Arquitetura:

» Componentes

• Memória

• Unidade lógico-aritm₫tica

• Unidade de controle

• Equipamentos de entrada

• Equipamentos de saída

» Aritm₫tica binária

Arquitetura de von Neumann

Memória

Unidade

de

Controle

– Programa em linguagem de

baixo nível armazenado em

memória

Entrada

ULA

Acumulador

Saída

Camadas de um Sistema

Computacional

Aplica₤ões

Linguagens

Sistemas Operacionais

Máquinas

SO

Máquina

1ª Gera₤₧o (1945-1955)

Nesta ₫poca os

conceitos de linguagem

de programa₤₧o e de

sistemas operacionias

n₧o estavam claros

Máquinas

– UNIVAC

– IBM 7090

Linguagens

Um único grupo de

Código Absoluto

pessoas projetava,

Fios e Paineis

construia, programava,

operava e efetuava

manuten₤₧o das máquinas

2ª Gera₤₧o (1955 - 1965)

Advento do Transistor

– redu₤₧o de dimensões

– redu₤₧o do consumo de

pot₨ncia

– possibilita a constru₤₧o de

equipamentos mais complexos

TX-0

» 1° Computador transistorizado

– MIT

PDP-1

– Metade do desempenho do

IBM 7090

– ~5% o valor do IBM 7090

– DEC

IBM 1401

IBM 7094

2ª Gera₤₧o (1955 - 1965)

Linguagens de Alto Nível

Sistema Operacional Batch

FORTRAN

– Fortran Monitor System

ALGOL

– IBSYS

Distin₤₧o clara das atividades e

grupos de pessoas na execu₤₧o de

tarefas

3ª Gera₤₧o (1965 - 1980)

Circuitos Integrados

– redu₤₧o de dimensões

– redu₤₧o do consumo de

pot₨ncia

– possibilita a constru₤₧o de

equipamentos mais complexos

– melhoria de desempenho

IBM System/360

– Família de Computadores com

diferentes desempenhos, precos,

mas compatíveis.

DEC PDP-11

– Minicomputador de 16 bits.

Microprocessadores

– INTEL

Microprocessadores

» 4004,8008,8080,8085,8086

– ZILOG

» Z80

– Motorola

» 68000

3ª Gera₤₧o (1965 - 1980)

Multiprograma₤₧o

Timesharing

Simula

Pascal

C

ML

Smalltalk

4ª Gera₤₧o (1980 - ?)

Very Large Scale Integration

Computadores

– Cray

– SUN - 20

– IBM SP2

Computadores Pessoais

Workstations

Processadores

– Intel PENTIUM

– ALPHA Digital

– PowerPC

4ª Gera₤₧o (1980 - ?)

Sistemas Operacionais para

C++

VisualBasic

Redes

Sistemas Operacionais

(Programa₤₧o Visual)

Distribuídos

Unix, Windows NT

Java

(Aplica₤ões para WEB)

Arquitetura de Computadores

Abordagens

de Hardware e de Software

Códigos de

Instru₤ões

Dados

Seqü₨ncia de

Fun₤ões Aritm₫tica

e Lógicas

Interpretador

de

Instru₤ões

Resultados

Programa₤₧o em Hardware

Controle

Dados

Fun₤ões Aritm₫tica Resultados

e Lógicas de

Propósito Geral

Programa₤₧o em Software

Arquitetura de Computadores

Diagrama

I/O Paralelo

Circuitos de

Temporiza₤₧o

em Bloco

I/O Serial

Circuitos de

Interrup₤₧o

CPU

Memória

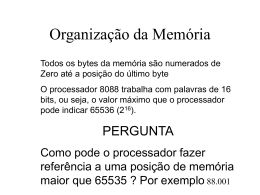

Sistema de Memória

Hierárquia

– Interna

» Registradores

» Cache

» Memória Principal

– Externa

» Disco Magn₫tico

» Fita

Desempenho × Custo

Princípio da Localidade

Reg.

Memória Principal

Memória de Massa

Processador Hipot₫tico

Barramento de Dados

Data buffer

Reg. Aux.

ALU

Reg. Inst

A

•Desempenho

•Espa₤o de endere₤amento

Flags

Reg. Uso

Geral

Dec. Inst

Unidade de Controle

.......................

Latch End.

Barramento de Controle

Barramento de Endere₤os

Arquitetura de Computadores

Ciclo

–

–

–

–

–

de Instrução

Ciclo de Busca

Ciclo de Decodificação

Ciclo de Leitura

Ciclo de Execução

Ciclo de Escrita

Arquitetura de Computadores

Formato

Genérico de Uma Instrução

Código da Instrução Dado, Endereço ou Modo de Endereçamento

Exemplos:

– mov al,01h

– mov al,[0400]

– mov al,[bx+si]

Arquitetura de Computadores

Diagrama

de Estado do Ciclo de Instrução

Lê

Operand.

Busca

Inst.

Escrev.

Operand.

Múltiplos

Resultados

Múltiplos

Operandos

Cal. End.

Prox. Inst.

Dec.

Inst.

Cal. End.

Operand.

Instrução Finalizada. Busca

Nova Instrução

Exec.

Operaç.

Retorna para string ou vetor

Cal. End.

Operand.

Arquitetura de Computadores

Interrupções

–

–

–

–

Internas

- erro de paridade, divisão por zero

Externas

- relógio, teclado

Mascarável - pode ser inibida

Não Mascarável - não pode ser inibida

Arquitetura de Computadores

Interrupções

– Hardware

– Software

na Arquitetura x86

Internas

Externas

Mascarável

Não-Mascarável

Sistema Operacional

Usuário

Arquitetura de Computadores

Programa do Usuário

1

2

i

i+1

m

Servi,co de Interrupção

Arquitetura de Computadores

Diagrama

de Estado do Ciclo de Instrução

com Interrupção

L₨

Operand.

Busca

Inst.

Escrev.

Operand.

Múltiplos

Resultados

Múltiplos

Operandos

Cal. End.

Prox. Inst.

Dec.

Inst.

Cal. End.

Operand.

Instrução Finalizada. Busca

Nova Instrução

Exec.

Operaç.

Retorna para string ou vetor

Verif. se

há interrp.

Sem

Interrup.

Cal. End.

Operand.

Interrupção

Arquitetura de Computadores

Múltiplas Interrupções

Programa do Usuário

Serviço da Interrupção X

1

2

i

i+1

j

j+1

m

Serviço da Interrupção Y

Arquitetura de Computadores

Interrupções Aninhadas

Programa do Usuário

Serviço da Interrupão X

1

2

J

j+1

i

i+1

Serviço da Interrupção Y

m

Arquitetura de Computadores

•Desempenho

•Espaço de endereçamento

Barramento

I/O

I/O

Dados

Endereço

Controle

CPU

Memória

Arquitetura de Computadores

Barramento

Linhas de Controle Típicas

Escrita

em memória

Leitura de memória

Escrita em I/O

Leitura de I/O

Solicitação de Barramento

Reconhecimento da Solicitação do Barramento

Solicitação de Interrupção

Reconhecimento de Interrupção

Clock

Reset

Arquitetura de Computadores

Barramento Hierárquico

Barr. Local

Cache

CPU

Controlador

Locoal de I/O

Memória

Barr. do Sistema

Interface

de Expansão

Modem

I/O Serial

SCSI

Network

Expansão do Bus

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Tipo

Multiplexado

Dedicado

Vantagem

I/O Paralelo

•Menos linhas

•Possível menor

Custo

I/O Serial

Desvantagem

CPU

Memória

•Circuitos dos

módulos é

mais complexo

•Desempenho

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Tipo

Multiplexado

Dedicado

Vantagem

I/O Paralelo

I/O Serial

Barr. de I/O

Desvantagem

•Mais linhas

•Custo

Adaptador

Adaptador

Barr. local

CPU

•Menor contenção

•Desempenho

Memória

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Método de Arbitragem

Centralizado

Distribuído

Req0

LM0

Req1

P1

P0

Árbitro

Gnt0

SM

Gnt1

I/O

LM1

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Método de Arbitragem

Centralizado

Distribuído

I/O

SM

Term.

Barr.

Term.

Busy

BPO Barr.

BPI

LM0

BPI

BPO

P0

LM1

BPI

BPO

P1

LM2

P2

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Temporização

AD bus

Síncrono

mrq

Assíncrono

CPU

rd

clk

clk

mrq

Circuitos de

Temporiza₤₧o

rd

add

data

Memória

Válido

P/ CPU

Leitura de Memória

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Temporização

AD bus

Síncrono

Assíncrono

msyn

data

CPU

rd

ssyn

rd

add

msyn

Válido

P/ CPU

ssyn

Leitura de Memória

Memória

Arquitetura de Computadores

Elementos de Projeto de um Barramento

Largura

Baramento de Dados : desempenho

Barramento de Endereço: espaço de endereçamento

Arquitetura de Computadores

PCI - Peripherical Component Interconnect

Barr. Local

CPU

Ponte/

Controlador de

Memória

DRAM

Cache

Vídeo

Contolador de

Vídeo

Network

Áudio

SCSI

Barramento PCI

Ponte para

Expansão

Dispositivos I/O

Expansão do Bus

Arquitetura de Computadores

PCI - Peripherical Component Interconnect

Estrutura

Pinos de Sistema (reset e clock)

Pinos de Dados e Endereços (32 linhas multiplexadas de dados e

endereços, erro de paridade)

Pinos de Controle de Interface (Coodernação e controle de

transações entre dispositivos - IRDY, TRDY, IDSEL, DEVSEL)

Pinos de Arbitragem - (Req, GNT)

Pinos de Erro - (PERR,SERR)

Pinos de Interrupção - (INTA,INTB,INTC,INTD)

Pinos de Suporte à Cache - (SOB,SDONE)

Pinos de Extensão para Barr. de 64 Bits - (Linhas de endereço e

dados multipliexadas, linhas de erro etc)

Pinos JTAG - ( Procedimentos de teste definidos no padrão IEEE 1149.1)

Arquitetura de Computadores

PCI - Peripherical Component Interconnect

Comandos

Reconhecimento de Interrupção

Ciclo Especial - (Utilizado por um iniciador para enviar comando

para mais de um destino ao memo tempo)

Leitura e Escrita de I/O

Leitura de Memória

Leitura

Leitura de Linha

Leitura Múltipla

Escrita em Memória

Escrita em Memória com Invalidação

Leitura de Configuração de Dispositivo

Escrita de Configuração de Dispositivo

Ciclo de Endereçamento Dual - (Endereçamento de 64 bits)

Sistema de Memória

Hierárquia

– Registradores

– Cache

– Memória Principal

• Memória Interna

– Disco Magnético

– CDROM

• Memória Externa

– Fita

• Memória Off-line

Sistema de Memória

Memória Principal - semicondutora Volateídade Categoria

Volátil

Tipo

Apagamento Escrita

E/L

RAM

Elétrico

Elétrico

Só leitura

ROM

Ñ é Possível

Máscara

PROM

Ñ volátil

Elétrico

Quase só

EPROM

UV

de leitura

EEPROM Elétrico

Sistema de Memória

Vcc

Memória ROM

Vcc

An-1

Dm-1

A0

nm

ROM

A0

CS

Lógica

de

Decod.

D0

Diagrama em Bloco

Vcc

An-1

CS

D0

D1

Estrutura Interna

D m-1

Sistema de Memória

Vcc

Memória PROM

Fusível

Vcc

An-1

Dm-1

A0

nm

PROM

A0

CS

Lógica

de

Decod.

D0

Diagrama em Bloco

Vcc

An-1

CS

D0

D1

Estrutura Interna

D m-1

Sistema de Memória

Memória EPROM

An-1

Entradas

CS OE/Vpp

Saídas

Ler/

Verificar

Saída

Desabilitada

VL

VL

dados_saída

VL

VH

Alta Imp.

Standby

VH X

Alta Imp.

Programa

VL VPP

Dados_entrada

Dm-1

nm

EPROM

A0

Modo

OE/

CS Vpp D0

Diagrama em Bloco

Sistema de Memória

Memória EEPROM

An-1

A0

Dm-1

Diagrama em Bloco

Entradas

CS OE

WE

Saídas

Ler

VL

Escreve

VL VH

VL Dados_ent.

Standby

VH X

X

A0

nm

EEPROM

WE CS OE D0

Modo

VL

VH Dados_saída

An-1

Alta imp.

Sistema de Memória

Ent_ Dados

Memória RAM Estática

Célula

An-1

A0

RW

Dm-1

A0

Diagrama em Bloco

An-1

Buffer de Saída

A0

Lógica

de

Decod.

nm

RAM

CS D0

R/W

Registradores

An-1

Buffer de Entrada

Saída_Dados

CS

Sistema de Memória

Memória RAM Estática

Célula

Vdd

Q1

Q2

A0

An-1

Q3

Ent_ Dados

R/W

Buffer de Saída

A0

Lógica

de

Decod.

Registradores

An-1

Q4

Buffer de Entrada

Célula

Saída_Dados

CS

Sistema de Memória

Ent_ Dados

Memória RAM Dinâmica

R/W

Célula

Ak-1/An-1

Din

n 1 Dout

RAM

A0/Ak

A0

RW RAS CAS

An-1

A0

Lógica

de

Decod.

Matrix

An-1

Diagrama em Bloco

Saída_Dados

CS

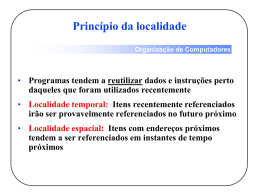

Memória Cache

Princípio da Localidade

– Instruções

Processador

Cache

– Dados

Operação

Next:

MOV CX,1000

SUB AX,AX

ADD AX,[SI]

MOV [SI],AX

INC SI

LOOP Next

Memória

Memória Cache

Princípio da Localidade

– Tacc=HitRate Tcache+(1- HitRate)

(Tcache+Tmem)

Processador

– Tcache=10 ns

– Tmem= 70 ns

– HitRate= 0,9

Cache

Memória

Tacc= 17 ns

Memória Cache

Política de Busca

– Demanda

» Busca uma linha i

Define quando e quais

informações buscar na

CACHE

quando esta se faz

necessário

– Pré-busca

» Busca a linha i+1

quando a linha i for

referida

Memória Cache

Política de Escrita

– Writethrough

» Garante consistência dos

Define quando uma palavra

deve ser alterada na

memória principal.

dados

» Aumenta o tráfego no

barramento

– Writeback

» Reduz o tráfego no

barramento

» Necessita de mecanismos

para manutenção de

consistência

Memória Cache

Política de Substituição

Define como uma linha da

memória CACHE deve ser

substituída.

– RAND - Aleatório

– FIFO - First in First Out

– LRU - Least Recently Used

Memória Cache

Organização

Mapeamento Direto

Tag

Linha

20

7

Endereço de 32 bits

5

– Vantagem

Simplicidade do Hardware

Algoritmo de Substituição ₫

simples

– Desvantagem

Não é flexível

Diversos blocos de memória são

mapeados na mesma linha da

CACHE

TAG

Dado

0

TAG

Dado

1

.

.

.

.

.

.

TAG

Dado

25 = 32 bytes

Número de Linhas

27 = 128

127

Memória Cache

Organização

Completamente Associativa

Tag

Linha

27

Endereço de 32 bits

5

– Vantagem

Flexibilidade

– Desvantagem

Complexidade do Hardware

TAG

Dado

0

TAG

Dado

1

.

.

.

.

.

.

TAG

Dado

25 = 32 bytes

127

Memória Cache

Organização

Associativa por Conjunto

(Set Associative)

Tag

Linha

21

6

5

Endereço de 32 bits

TAG

Dado

TAG

Dado

0

TAG

Dado

TAG

Dado

1

.

.

.

.

.

.

.

.

.

.

.

.

TAG

Dado

TAG

Dado

25 = 32 bytes

25 = 32 bytes

63

Coer₨ncia de Cache em Sistemas

Multiprocessadores

Protocolo de coerência

de Cache MESI

– Modified - a linha corrente

foi modificada (diferente da

informação na memória

principal) e pertence a uma

única cache.

– Exclusive - linha são

modificada e exclusiva de uma

única cache. Escrevendo-se

nesta linha, esta passa para o

estado Modified.

– Shared - linha corrente

pertence a mais de uma cache.

Ao escrever-se nesta linha, um

writethrough é gerado e

invalidam-se as outras cópias

em outras caches.

– Invalid - a linha corrente

está vazia. Uma leitura desta

linha gera um miss.

Coerência de Cache em Sistemas

Multiprocessadores

p3

P1

X=7

I

cache

I

cache

D

cache

D

cache

Barramento

p4

P2

I

cache

D

cache

X=10

Memória

I

cache

D

cache

X=30

Arquitetura de Computadores

Classifica₤₧o de Flyn

– SISD - Processadores von

Neumann

– SIMD - Array Processors

– MISD

– MIMD - Multiprocessadores

/Multicomputadores

Classifica₤₧o para

Arquiteturas Paralelas

– Computadores Pipeline

– Array Processors

– MIMD

Multiprocessadores - UMA

P1

P2

Pn

Sistema de Interconex₧o

I/O

SM1

•Fortemente Acoplados

•Aplica₤ões Gerais

Time-sharing

SMm

Memória

Compartilhada

Multiprocessadores - NUMA

Modelo Cedar

GSM

- University Illinios

GSM

GSM

Rede de Interconex₧o Global

P

CSM

P

CSM

P

CSM

P

CSM

C1

C2

Multiprocessadores - COMA

P

Cache

P

P

Cache

Cache

Rede de Interconex₧o Global

•DDM - Swedish Institute of Computer Science

Multicomputadores

M

P

Rede

de

Interconex₧o

M

P

•Intel iPSC/1 •Intel Paragon •MIT J-Machine-

M

P

M

P

Memória Externa

• Disco Magnético

Setor

– Organização dos Dados

Gap

•

•

•

•

Superfícies

Trilhas (separadas por gaps)

Setores (separados por gaps)

Densidade

Trilha

Memória Externa

• Disco Magnético

Trilhas

– Características Físicas

• Cabeças Móveis

Cabeça

Memória Externa

• Disco Magnético

Trilhas

– Características Físicas

• Cabeças Fixas

Cabeças

Memória Externa

• Disco Magnético

•

– Características Físicas

• Cabeças Fixas

• Cabeças Móveis

• Removíveis (Floppy disk)

Memória Externa

• Disco Magnético

•

– Características Físicas

•

•

•

•

Cabeças Fixas

Cabeças Móveis

Removíveis (Floppy disk)

Fixos (hard disk)

Memória Externa

• Disco Magnético

•

– Características Físicas

• Sistema das Cabeças de R/W

– Contact (Floppy disk)

– Fixed Gap

– Gap Aerodinâmico (Winchester)

Memória Externa

• Disco Magnético

Cabeças de Leitura/Gravação

Superficies

Setor

Trilha

Gap

Tacesso=Tseek + Tlat + Ttrans

Taxatransf = bytes transf./ Tacesso

Memória Externa

• CD-ROM

– Tecnologia

• Disco feito de resina

• Coberto por alumínio reflexivo

• Informação gravada através criados por raios lazer

• Proteção final feita por um lacquer

• Leitura feita através da relexão de raios lazer sobre a

superfície

Memória Externa

• CD-ROM

* CD-ROM

Velocidade

Angular Constante

•Desvantagem

Capacidade dos

setores externos fica

limitada a do mais

interno

Vantagem

Simplicidade no

endereçamento de

setores

Velocidade

Linear Constante

Desvantagem

Vantagem

Maior capacidade Sistema de

de armazenamento endereçamento

mais complexo

Memória Externa

• CD-ROM

•Espaçamento entre

trilhas (eet)= 1.6 m

#trilhas = r/eet =20344

(aparentes)

r=32,55m

•De fato, tem-se uma espiral!

•Comprimento da espiral = 5,27Km

•VLC = 1,2 m/s

Tempo para percorrer o disco = 4391s = 73,2 min

•Densidade de Armazenamento = 176,4 Kbytes/s

Capacidade = 774,57 Mbytes

Memória Externa

• CD-ROM

– Organização dos Dados

• Superfícies

• Trilhas (separadas por gaps)

• Blocos

– Formato do Bloco

00 FF×1000 End M

Sync

Id

2048 bytes

Dados

Modos

•M0 - campo de

dados em branco

•M1 - 2048 bytes + ECC

•M2 - 2336 sem ECC

288 bytes

ou ECC

M2=dados, M1=ECC

Memória Externa

• WORM (Write Once Read Many)

– Tecnologia

• Disco feito de resina

• Coberto por alumínio reflexivo

• Pré-formatação feita através de raios lazer que cria uma

série de “bolhas”

• Gravação feita por um sistema lazer (não tão poderoso)

que rompe as “bolhas”

• Leitura feita através da relexão de raios lazer sobre a

superfície

– Layout - VAC

– Capacidade característica = 650 Mbytes

Memória Externa

• Erasable Optical Disk

– Tecnologia

• Disco feito de resina

• Coberto por um material cuja reflexibilidade pode ser Alta, Baixa ou

indeterminada.

• A gravação é feita através de raio lazer que altera o estado

de reflexivo do material

• Leitura feita através da relexão de raios lazer sobre a

superfície

– Layout - VAC

– Capacidade Característica : 650 Mbytes

Memória Externa

• Fita Magnética

– Tecnologia

• Material recoberto por oxido magnético.

– Organização dos dados

Gap

Trilhas

Registro

Memória Externa

• Fita Magnética

–

–

–

–

Número Típico de Trilhas - 9, 18, 36

Acesso Seqüencial

Vantagem : Custo

Desvantagem : Tempo de Acesso

Entrada/Saída

• Técnicas para Controle de I/O

– I/O programado

– Baseado em Interrupções

– Baseado em DMA

Entrada/Saída

• Modelo de Genérico de Dispositivo de I/O

Bus de end.

Bus de dados

Bus de controle

Módulo I/O

status e

controle

dados

Disp. Externo

Dados do/para o ambiente

Entrada/Saída

• Categorias de Dispositivo Externo

– Para Interação com Pessoas (Teclado, vídeo etc)

– Para Interação com Máquinas (Unidade de disco)

– Para Comunicações (Dispositivo remoto)

Entrada/Saída

• Modelo Genérico de um Dispositivo Externo

Controle do módulo I/O

Status para módulo I/O

Lógica

de

Controle

Dados de/para o módulo I/O

Buffer

Transdutor

Dados de/para o ambiente

Entrada/Saída

• Modelo Genérico do Módulo I/O

Dados

Interface

com

Disp.

Externos

Reg. de dados

Regs. Status e de Controle

Endereço

Controle

Lógica

de I/O

Interface

com

Disp.

Externos

Dados

Controle

Status

Dados

Controle

Status

Entrada/Saída

• Técnicas para Controle de I/O

– I/O programado

• Comandos

–

–

–

–

Controle - informa ao periférico o que fazer

Teste - testa condições

Leitura - ler dados do periférico

Escrita - escreve dados no periférico

Entrada/Saída

• Técnicas para Controle de I/O

– I/O programado

Envia Comando

de Leitura

para Módulo I/O

Condição de

erro

pronto

Lê status do

Módulo I/O

Ver.

status

Escreve

palavra na

Memória

Lê palavra do

Módulo I/O

Não está

pronto

não

Feito ?

sim

Próxima Instrução

Entrada/Saída

• Técnicas para Controle de I/O

– Baseado em Interrupção

Vai fazer qualquer coisa

Envia Comando

de Leitura

para Módulo I/O

Condição de

erro

pronto

Lê status do

Módulo I/O

Ver.

status

Escreve

palavra na

Memória

Lê palavra do

Módulo I/O

Interrupção

não

Feito ?

sim

Próxima Instrução

Entrada/Saída

•Técnicas para Controle de I/O - Baseado em Interrupção

Hardware

Software

INTERRUPT

SERVICE

PROCEDURE

Controlador ou

Periférico solicita

Interrupção

Processador Finaliza

Processamento

da Interrupção

Salva Estado

Execução de

Instrução Corrente

Processador

Reconhece

Interrupção

PUSH FLAGS

PUSH IP

FETCH ISR ADDRESS

Processa Interrupção

POP IP

POP FLAGS

Restaura Estado

Retorno

Entrada/Saída

• Técnicas para Controle de I/O

– Baseado em DMA

Quantidade

de Dados

Bus de Dados

Reg. de

Dados

Bus de Endereço

Reg. de

Endereço

DMA_Req

DMA_Ack

Int_req

Rd

Wr

Lógica

de

Controle

Diagrama Genérico

do Controlador de

DMA

Entrada/Saída

• Técnicas para Controle de I/O

– Baseado em DMA

Envia

Solicitação

de DMA

Aguarda

Reconh.

Solicitação

de DMA

Lê dados do

Dispositivo ou

da Memória

Escreve na

Memória ou

no Dispositivo

Reconhecimento

da solicitação DMA

Envia Comando

de Leitura/Escrita

DMA

para Módulo I/O

Controlador DMA

não

Feito ?

sim

Vai fazer

qualquer coisa

Processador

Solicitação

de DMA

Envia

Reconh. DMA

Suspensão

Próxima Instrução

Retira

Solicitação de DMA

Arquitetura de Computadores

Arquiteturas RISC X

CISC

– Complex Instruction Set Computer

– Reduced Instruction Set Computer

» RISC : SPARC

» CISC : Intel 386

Arquitetura de Computadores

Caracteristicas CISC

– Instruções complexas

– Modos de

endereçamento

complexos

– Controle

implementado por

ROM

– Micro-instruções

Problemas CISC

– Desempenho

– ROM interna

aumenta as

dimensões da pastilha

– Mau uso, pelos

programadores, das

instruções e modos de

endereçamento

disponíveis

Arquitetura de Computadores

CISC

•SE CARACTERIZA POR:

•CONJUNTO DE INSTRUÇOES E MODOS DE

ENDEREÇAMENTO SOFISTICADOS

•CONTROLE MICROPROGRAMADO

•UM NÚMERO REDUZIDO DE INSTRUÇÕES NO

CÓDIGO COMPILADO

•COMPILADOR DE CONSTRUÇÃO MAIS SIMPLES

Arquitetura de Computadores

CISC

MEMÓRIA DE

MICROPROGRAMA

CONTROLE

VIA DE

DADOS

PC

CONTADOR DE

MICROPROGRAMA

+1

LÓGICA DE

SELEÇÃO

DE

ENDEREÇO

REGISTRADOR

DE INSTRUÇÃO

UNIDADE DE CONTROLE

STATUS

MEMÓRIA

Arquitetura de Computadores

RISC

Objetivos das Maquinas RISC

– Melhoria de desempenho

– Reduzir acesso à memória principal (arq. load/store)

– Instruções e modos de endere₤amento simples (Controle

hardware wired)

– Bom uso dos registradores

– Pipelining (execução super-escalar)

– Uso extensivo do compilador

Arquitetura de Computadores

RISC

SE CARACTERIZA POR:

•CÓDIGOS DE INSTRUÇÃO MAIS SIMPLES

•COMPILADORES MAIS SOFISTICADOS

•PEQUENOS CICLOS DE CLOCK

•PEQUENOS NÚMEROS DE CICLOS POR

INSTRUÇÃO

•EFICIENTE PIPELINING DE FLUXO DE

INSTRUÇÕES

Arquitetura de Computadores

RISC

DATAPATH

HARDWIRED

OUTPUT AND

NEXT-STATE

CONTROL

REGISTE

R

LOGIC

FILE

STATE

REGISTER

ALU

STATUS

DATA

INSTRUCTIO

N REG.

INSTR.

CACHE

CACHE

MEMORY

CONTROL UNIT

Arquitetura de Computadores

Petium

8086

– 16 bits

– Espaço de endereçamento :

1 Mb

– Endereço da primeira

instrução executada:

FFFF0H

286

– 16 bits

– Espaço de endereçamento :

16 Mb (24 bits)

– Memória Virtual

386

– 32 bits

– Espaço de

endereçamento : 32

bits

– Registradores de 32

bits

486

– Cache interna de 8K

– Co-processador 80387

interno

Arquitetura de Computadores

Petium

Pentium é uma máquina CISC com características

de RISC

– Pipelines

- Superescalar

– Cache Interna - Dados, Instrução

– Registradores de uso geral - 32

– Previsão dinâmica de desvios

– Co-processador aritmético interno com 7

registradores de ponto flutuante de 80 bits

Modos de Operação

Modo

Real

– 1 Mbyte

Modo

–

–

–

–

Protegido

4 Gbytes

Multitarefa

Memória Virtual

Gerenciamento e Proteção de Memória

Modo

Virtual

Modo de Gerenciamento

Modelo de Software

Registradores de Uso Geral

Registradores de Segmento

EAX

AH

AX AL

Acumulador

EBX

BH

BX BL

Base

CS

Codigo

ECX

CH

CX CL

Contador

DS

Dados

EDX

DH

DX DL

Dados

EBP

ESI

EDI

Pilha

SS

BP

Base de Pilha

ES

SI

Índice Fonte

FS

DI

Índice Dest.

EIP

IP

Apont. Inst.

ESP

SP

Apont.Topo de Pilha

EFlags

Flags

Flags

GS

Extras

Modelo de Software

Registrador

NT

IOPL

de Flags

OF

DF

IF

TF

» CF - Vai-um

» PF - Paridade

» AF - Vai-um auxiliar

» ZF - Zero

» SF - Sinal

» OF - Estouro

SF ZF

AF

PF

CF

» IF – Interrupção

»DF - Direção

»TF - Passo Simples

»IOPL - Nível de Prioridade

da Tarefa

»NT - Tarefa Aninhada

Modos de Endereçamento de

Dados

Imediato

Op_Code

Dado

– Ex.: mov cx,1024H

Registrador

Op_Code

Regist.

Regist.

– Ex.: mov al,ah

Dado

Modos de Endereçamento de

Dados

Direto

Op_Code

Ender.

Dado

– Ex.: mov al,[0300h]

mov ax,counter

Registrador Indireto

Op_Code

Regist.

BX,SI,DI

– Ex.: mov ch,[bx]

Ender.

Dado

Modos de Endereçamento de

Dados

Indexado

Op_Code Regist. de Índice Desl.

SI,DI

Desl.

– Ex.: mov ch,[bx]

Ender.

Dado

Modos de Endereçamento de

Dados

Base

Op_Code Regist. de Base

BX,BP

Desl.

Desl.

– Ex.: mov ch,[bx+02]

Ender.

Dado

Modos de Endereçamento de

Dados

Base

Indexado

Op_Code Regist. de Base Regist. de Índice

BX,BP

Regist. de Índice

– Ex.: mov ch,[bx+si]

Ender.

Dado

Modos de Endereçamento de

Dados

Base

Indexado com Deslocamento

Op_Code Regist. de Base Regist. de Índice

Desl.

Desl.

BX,BP

Regist. de Índice

– Ex.: mov ch,[bx+si+03]

Ender.

Dado

Modos de Endereçamento de

Dados

Porta

Op_Code

Ender. ou DX

– Ex.: in al,80h

in al,dx

out 90h,al

out dx,al

;espaço de

; endereçamento = 256

; espaço de

; endereçamento = 65536

Modos de Endereçamento de

Dados

Modo

de Endereçamento de 32 bits

Reg. de Seg. CS,DS,ES,FS,GS,SS

Reg. de Base EAX,EBX,ECX,EDX,EBP,ESI,EDI,ESP

*

Reg. de Índice

Fator de Escala

EAX,EBX,ECX,EDX,EBP,ESI,EDI

{1,2,4,8}

Deslocamento Nada, 8 bits, 32 bits

Ex.:

Endereço

MOV EAX,[EBX],[ECX*4+6]

Arquitetura do Pentium

Branch

target

buffer

Floating

point unit

Instruction pointer

Branch target address

32

Prefetch

address

8kb

instruction 256

cache

TLB

Floating

point registers

P b

r u

e f

f f

e e

t r

c

h

I d

n e

s c

t o

r d

u e

t.

C

o

n

t

r

o

l

Control

ROM

Page

Unit

u

n

i

t

Add.

generate

V pipe

Add.

generate

U pipe

ALU

V pipe

Integer

register

file

ALU

U pipe

8kb

data

cache

Shifter

32

Address bus - 32 bits

Add.

Control bus

Bus Unit

Add. Bus

32 bits

Data

Data bus - 64 bits

Data bus - 64 bits

TLB

Arquitetura do Pentium

Dois

pipelines de 5 estágios: U e V

– Estágios

» PF - prefetch

» D1 - instruction decode

» D2 - address generate

» EX - execute, cache, ALU access

» WB - writeback

Arquitetura do Pentium

P b

r u

e f

f f

256 bits e e

t r

c

h

I d

n e

s c

t o

r d

u e

t.

Prefet.

Buffer

V

64 bytes

Decod.

D1

V

256 bits

Prefet.

Buffer

U

64 bytes

Decod.

D1

U

Arquitetura do Pentium

Para o

BTB

Decod.

D1

V

Decod.

D2

V

Ger.

End.

V

Ger.

End.

U

Decod.

D1

U

Decod.

D2

U

Para o BTB

Arquitetura do Pentium

Decod.

D1

V

Decod.

D2

V

ALU

V

Decod.

D1

U

Decod.

D2

U

Unidade de

Microcódigo

REG

ALU

U

Arquitetura do Pentium

FPU

Conrole

Decod.

D1

V

Decod.

D2

V

Reg. File

ADD

DIV

MUL

Dados

Decod.

D1

U

Decod.

D2

U

Unidade de

Microcódigo

Arquitetura do Pentium

Execução Super-Escalar

– Ambas as instruções devem

ser simples.

– Sem dependência de dados.

– As instruções não podem ter

modos de endereçamento

imediato e indireto.

– Instruções com prefixo só

podem ser executadas no

pipelin U.

Não requerem micro-código para serem

executadas. Normalmente levam 1

ciclo de clock para serem executadas.

ADD AX,BX (não podem ser executadas

ADD AX,CX em paralelo)

MOV TABLE[SI],7

MOV ES:[DI],AL

Arquitetura do Pentium

Execução

Ciclos

de clock

PF

D1

D2

1

I1

Super-Escalar

2

I2

3

I3

I4

I1

I2

I5

I3

I1

4

5

I6

I7

I8

I9

I10

I4

I5

I6

I7

I8

I3

I4

I5

I6

I1

I2

I3

I4

I1

I2

I2

EX

WB

Previsão Dinâmica de Desvio

NT

T

H:11

P:T

Branch

target

buffer

TLB

T

Instruction pointer

T

H:01

P:T

H:00

P:NT

P b

r u

e f

f f

e e

t r

c

h

I d

n e

s c

t o

r d

u e

t.

NT

T

Branch target address

Prefetch

address

8kb

instruction 256

cache

H:10

P:T

NT

NT

Address Instruction Targ. Add.

.

.

.

History

Prediction

Memória Cache

Princípio da Localidade

– Instruções

Processador

Cache

– Dados

Operação

Next:

MOV CX,1000

SUB AX,AX

ADD AX,[SI]

MOV [SI],AX

INC SI

LOOP Next

Memória

Memória Cache

Princípio da Localidade

– Tacc=HitRate Tcache+(1- HitRate)

(Tcache+Tmem)

Processador

– Tcache=10 ns

– Tmem= 70 ns

– HitRate= 0,9

Cache

Memória

Tacc= 17 ns

Memória Cache

Política de Busca

– Demanda

Usada para decidir quando

e quais informações buscar

na CACHE

– Pré-busca

Memória Cache

Política de Busca

– Demanda

» Busca uma linha i

Usada para decidir quando

e quais informações buscar

na CACHE

quando esta se faz

necessário

– Pré-busca

» Busca a linha i+1

quando a linha i for

referida

Memória Cache

Política de Escrita

– Writethrough

» Garante consistência dos

O momento em que uma

palavra deve ser alterada

na memória principal, após

uma escrita, depende da

política de escrita.

dados

» Aumenta o tráfego no

barramento

– Writeback

» Reduz o tráfego no

barramento

» Necessita de mecanismos

para manutenção de

concist₨ncia

Memória Cache

Política de Substituição

– RAND - Aleatório

Define como uma linha da

memória CACHE deve ser

substituída.

– FIFO - First in First Out

– LRU - Least Recently Used

Memória Cache

Organização

Mapeamento Direto

Tag

Linha

20

7

Endereço de 32 bits

5

– Vantagem

Simplicidade do Hardware

Algoritmo de Substituição ₫

simples

– Desvantagem

Não é flexível

Diversos blocos de memória são

mapeados na mesma linha da

CACHE

TAG

Dado

0

TAG

Dado

1

.

.

.

.

.

.

TAG

Dado

25 = 32 bytes

Número de Linhas

27 = 128

127

Memória Cache

Organização

Completamente Associativa

Tag

Linha

27

Endere₤o de 32 bits

5

– Vantagem

Flexibilidade

– Desvantagem

Complexidade do Hardware

TAG

Dado

0

TAG

Dado

1

.

.

.

.

.

.

TAG

Dado

25 = 32 bytes

127

Memória Cache

Organização

Associativa por Conjunto

(Set Associative)

Tag

Linha

21

6

5

Endereço de 32 bits

TAG

Dado

TAG

Dado

0

TAG

Dado

TAG

Dado

1

.

.

.

.

.

.

.

.

.

.

.

.

TAG

Dado

TAG

Dado

25 = 32 bytes

25 = 32 bytes

63

Memória Cache

Organização do Pentium

Two-way-set - associative

128 Conjuntos - 256 linhas (entradas)

32 bytes por linha (64 por conjunto)

8Kb de CACHE de instrução

TAG

8Kb de CACHE de dados

TAG

Triple ported

– Pipeline U

– Pipeline V

– Opera₤ões de Bus snooping

Estrutura

Dado

TAG

Dado

Dado

TAG

Dado

.

.

.

.

.

.

.

.

.

.

.

.

TAG

Dado

TAG

Dado

25 = 32 bytes

25 = 32 bytes

Set 0

Set 1

Set 127

Arquitetura do Pentium

Branch

target

buffer

Floating

point unit

Instruction pointer

Branch target address

32

Prefetch

address

8kb

instruction 256

cache

TLB

Floating

point registers

P b

r u

e f

f f

e e

t r

c

h

I d

n e

s c

t o

r d

u e

t.

C

o

n

t

r

o

l

Control

ROM

Page

Unit

u

n

i

t

Add.

generate

V pipe

Add.

generate

U pipe

ALU

V pipe

Integer

register

file

ALU

U pipe

8kb

data

cache

Shifter

32

Address bus - 32 bits

Add.

Control bus

Bus Unit

Add. Bus

32 bits

Data

Data bus - 64 bits

Data bus - 64 bits

TLB

Memória Cache

Translation Lookaside Buffer

Endereço linear

TLB

Endereço Físico

para

Cache

T

Tag

Linha

16

4

0T

T

End

End

.

.

.

.

.

.

.

.

.

End

T

End

T

T

End

End

.

.

.

T

Endereço Físico

para Cache

12

20

Endereço Linear

End

End

T

T

End

End

.

.

.

.

.

.

.

.

.

.

.

.

T

End

T

End

T

1

12

0

1

15

Coerência de Cache em Sistemas

Multiprocessadores

Protocolo de coerência

de Cache MESI

– Modified - a linha corrente

foi modificada (diferente da

informação na memória

principal) e pertence a uma

única cache.

– Exclusive - linha não

modificada e exclusiva de uma

única cache. Escrevendo-se

nesta linha, esta passa para o

estado Modified.

– Shared - linha corrente

pertence a mais de uma cache.

Ao escrever-se nesta linha, um

writethrough é gerado e

invalia-se as outras cópias em

outras caches.

– Invalid - a linha corrente

está vazia. Uma leitura desta

linha gera um miss.

Coerência de Cache em Sistemas

Multiprocessadores

p3

P1

X=7

I

cache

I

cache

D

cache

D

cache

Barramento

P2

p4

I

cache

D

cache

X=10

I

cache

D

cache

X=30

Dimensões das Caches

Pentium

– Um nível de cache interno.

– Cache de dados : 8kb

– Cache de instruções: 8kb

Pentium MMX

– Um nível de cache interno

– Cache de dados: 16kb

– Cache de Instruções: 16kb

Pentium Pro

– Dois níveis de cache internos.

– Cache dados nível 1: 8kb

– Cache de instrução nível 1:

8kb

– Cache nível 2: 256kb, 512kb,

1MB

Dimensões das Caches

Petium II

– Dois níveis de cache internos.

– Cache de dados nível 1: 16kb

– Cache de instrução nível 1:

16kb

– Cache nível 2: 512kb

Petium III

– Dois níveis de cache internos.

– Cache de dados nível 1: 16kb

– Cache de instrução nível 1:

16kb

– Cache nível 2: 512kb

Unidade de Ponto Flutuante

PF - pré-busca

D1 - decodificação de instrução

D2 - geração de endereço

EX - leitura de memória e

registradores. Converção do

formato de ponto flutuante em

formato de memória. Escrita em

memória.

X1 - primeiro estágio de execução.

Dados da memória são convertidos

no formato ponto flutuante.

Escreve o operando para os

registradores de ponto flutuante.

X2 - segundo estágio de execução.

WF - arrendonda o resultado e

escreve nos registradores de ponto

flutuante.

ER - sinalização de erro e

atualização da palavra de status.

Unidade de Ponto Flutuante

Pipeline U

Fluxo de

instruções

e de dados

PF

D1

D2

EX

Bypass

Fluxo de

dados

ER

Registradores

de

Ponto Flutuante

WF

80 bits

X2

ST(0)

ST(1)

ST(2)

ST(3)

ST(4)

ST(5)

ST(6)

ST(7)

X1

Operações de Barramento

M/IO D/C W/R Cache KEN Descrição

0

0

0

1

x

Recon. Int.

0

0

1

1

x

Ciclo Especial

0

1

0

1

x

Leit. I/O

0

1

1

1

x

Escr. I/O

1

0

0

1

x

Leit. de Código ñ cache

1

0

0

x

1

Leit. de Código ñ cache

1

0 0

0

0

Leit. de Código em Rajada de 32 bytes

1

1 0

1

x

Leit. Mem. Acima de 8 bytes ñ cache

1

1 0

x

1

Leit. Mem. Acima de 8 bytes ñ cache

1

1 0

0

0

Leit. Mem em Rajada de 32 bytes

1

1 1

1

x

Escr. Mem. Acima de 8 bytes ñ cache

1

1 1

0

x

Escrita de 32 bytes - writeback

Opera₤ões de Barramento

Ciclos Especiais

BE7

BE6

BE5

BE4

BE3

BE2

BE1

BE0

Ciclo

1

1

1

1

1

1

1

0

shutdown

1

1

1

1

1

1

0

1

flush cache

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

halt

writeback

flush ack.

br. tr. mess

Ciclos de Leitura/Escrita

t1

t2

ti

t1

t2

ti

Clk

ADS

Válido

Válido

Address

W/R

BRDY

P/ CPU

da CPU

Data

Ciclos Burst

O

pentium suporta ciclos de leitura e escrita

em rajada de 32 bytes.

– Cada oito bytes são transferidos a cada ciclo de clock.

– O Processador passa o endere₤o inicial, os demais

endere₤o devem ser gerados pelo sistema de memória

1° end.

2 ° end.

3° end.

4° end.

0

8

10

18

8

0

18

10

10

18

0

8

18

10

8

0

Ciclos Burst

t1

t2

t2

t2

t2

ti

Clk

ADS

Válido

Address

W/R

BRDY

CACHE

KEN

P/ CPU

P/ CPU

P/ CPU

P/CPU

Data

Operações Locked e BOFF

Lock

– Operacões atômicas não podem

ser quebradas em operações

menores

– Semáforos

– Requerem leitura seguida de

escrita

– XCHG

– LOCK é ativado indicando que

o ciclo no ciclo corrente o

barramento está bloqueado e

não pode ser interrompido

BOFF

– Este sinal de entrada prover

uma forma para que em

sistemas multiprocessados

um Pentium possa “tomar

conta” do barramento.

– Este terminal(BOFF) ₫

verificado a cada ciclo de

clock. Caso o seu valor seja

baixo, o barramento ₫

colocado em alta

impedância.

Operações Bus Hold e

Reconhecimento de Interrupção

Bus Hold

– Uma segunda forma para

que o processador “tome

conta”do barramento.

– A entrada HOLDé

verificada a cada ciclo de

clock, caso seja alto, no

final do ciclo de

barramento, o barramento é

colocado em alta

impedância.

– A saída HLDA é ativada

para indicar que o Pentium

está neste estado.

Reconhecimento de

Interrupção.

– Dois destes ciclos são

gerados em reconhecimento

a solicitação de interrupção

(INTR).

– M/IO=D/C=W/R =0

– CACHE = 1

Reconhecimento de Interrupção

vcc

INT0

.

.

.

‘148

INT7

A2

A1

A0

‘374

.

.

.

D

0

GS

EI

vcc

DQ

clk

clr

D

7

Pentium

INTR

M/IO

D/C

W/R

ADS

Cache Flush e Shutdown

Cache Flush

– Como resposta a uma entrda

ativa no terminal FLUSH o

Pentium executa o writeback

nas linhas modificadas e as

torna inválidas

– BE1 =0

– Quando o writeback é

executado o processador

executa um cache ack. para

informar que na cache foi

realizado um flush.

– BE4 =0

Shutdown

– Se o processador

detecta um erro de

paridade um ciclo

shutdown é gerado.

– A execução é suspensa

até o processador que

ocorrar um NMI, INIT

ou RESET

– Cache internas

permancem inalteradas

– BE0=0

Halt e Inquire Cycles

Halt

– Ciclo realizado quando

da execução de uma

instrução HLT

– Similar ao shutdown

exceto que a execução

só será retomada pelo

sinal INTR

– BE2 = 0

Inquire Cycle

– Usado para manter a

coerência de cache

– Ao detectar-se (no

snooping cycle) um acesso,

por outro processador, a

uma posição de memória,

o processador gera um

inquire interno para

verificar se esta posição

esta na cache interna. Caso

esteja, a cache pode ser

modificada.

Tipo de Instruções

Transferência de dados

Aritmética

Manipulação de bit

Laços e saltos

Subrotinas e interrupções

Controle

String

Tipo de Instruções

Instruções Monádicas

Instruções Diádicas

– inst opr dest

– inst opr dest, opr fonte

opr dest - operando destino

opr dest - operando destino

opr fonte - operando fonte

Transferência de Dados

Instruções

– POP

–

–

–

–

–

–

–

MOV

MOVSX

MOVZX

PUSH

PUSHW/PUSHD

PUSHA/PUSHAD

PUSHF/PUSHFD

movimenta₤₧o

ext. sinal

ext. c/ zero

empilhamento

imedit./ 32 bits

todos reg/ 32 bits

16 bits flags/32 bits

desemp.

– POPA/POPAD

todos reg/32 bits

– POPF/POPFD 16 bits flags/32 bits

– IN

input

– OUT

output

– XCHG

permuta

– XLAT

translate-table

– LEA

carga de end. efetivo

– LDS e similares carga de ponteiro

– BSWAP

troca

– LAHF

carga de flags em AH

– SAHF

arm. de AH nos flags

Transferência de Dados

Sintaxe:

MOV OP_DEST,OP_DEST

EX.: MOV AL,01

MOV AX,[BX+2]

MOV AL,[0400H]

Transfer₨ncia de Dados

Sintaxe:

MOVSX OP_DEST,OP_DEST

EX.: MOVSX AX,AL

Transfer₨ncia de Dados

Sintaxe:

MOV OP_DEST,OP_FONT

EX.: MOVZX AX,AL

Transfer₨ncia de Dados

Sintaxe:

PUSH OP_FONTE

EX.: PUSH BX

Transfer₨ncia de Dados

Sintaxe:

PUSHW/PUSHD OP_FONTE (imedit./ 32 bits)

EX.: PUSHW 34ADh

PUSHD EAX

- PUSHD pode ser usado para

empilhar valor de um reg. de 32 bits

Transfer₨ncia de Dados

Sintaxe:

PUSHA/PUSHAD

EX.: PUSHA

PUSHAD

(todos reg/ 32 bits)

Transfer₨ncia de Dados

Sintaxe:

PUSHF/PUSHFD

EX.: PUSHF

PUSHFD

16 bits flags/32 bits

Transfer₨ncia de Dados

Sintaxe:

POP OP_DEST

EX.: POP BX

Transfer₨ncia de Dados

Sintaxe:

POPA/POPAD

EX.: POPA

POPAD

todos reg/32 bits

Transfer₨ncia de Dados

Sintaxe:

POPF/POPFD

EX.: POPF

POPFD

16 bits flags/32 bits

Transfer₨ncia de Dados

Sintaxe:

IN ACUMULADOR,END/DX

EX.: IN AL,60H

IN AL,DX

input

Transfer₨ncia de Dados

Sintaxe:

OUT END/DX,ACUMULADOR

EX.: OUT DX,AL

OUT 80H,AX

output

Transfer₨ncia de Dados

Sintaxe:

XCHG OP_DEST,OP_FONTE

EX.: XCHG AL,AH

XCHG AL[BX]

permuta

Transfer₨ncia de Dados

Sintaxe:

XLAT

translate-table

O registrador BX deve ter o endere₤o inicial da

lista.

O valor de AL ₫ o índice.

EX.: MOV AL,3

MOV BX,0400H

XLAT

Transfer₨ncia de Dados

Sintaxe:

LEA OP_DEST,LABEL

EX.: LEA BX,LISTA

carga de end.

Transfer₨ncia de Dados

Sintaxe:

LDS OP_DEST,OP_FONTE

OP_DEST

carga de ponteiro

- registrador

LES,LFS,LGS,LSS

-

EX.: LDS BX,[SI]

LES DX,end_lista

s₧o similares

Transfer₨ncia de Dados

Sintaxe:

BSWAP OP_DEST

- OP_DEST

- troca (swapping)

- registrador de 32 bits

EX.: MOV EAX,12345678H

BSWAP EAX

EAX = 78563412H

Transfer₨ncia de Dados

Sintaxe:

LAHF

EX.: POPF

LAHF

- Carrega AH com flags

Transfer₨ncia de Dados

Sintaxe:

SAHF

EX.: MOV AH,0FFH

SAHF

- Armazena AH nos flags

Aritmética

Instruções

– ADD

– ADC

– INC

–

–

–

–

–

SUB

SBB

DEC

CMP

MUL

– IMUL

– DIV

– IDIV

adição

incremento

subtração

– NEG

– CBW

complemento a 2

mudança de módulo

– CWD

– DAA

ajuste BCD

– DAS

decremento

comparação

multiplicação

divisão

– AAA

– AAS

– AAM

– AAD

ajuste ASCII

Aritm₫tica

Sintaxe:

ADD OP_DEST,OP_DEST

EX.:

ADD AL,CH

ADD CX,[SI]

ADD DX,4

- adi₤₧o

Aritm₫tica

Sintaxe:

ADC OP_DEST,OP_DEST

EX.:

ADC AL,CH

ADC [BX],DX

ADC DX,4

- adi₤₧o com vai um

Aritm₫tica

Sintaxe:

INC OP_DEST

EX.:

INC AL

INC [BX]

INC [0400H]

- Incremento

Aritm₫tica

Sintaxe:

SUB OP_DEST,OP_DEST

EX.:

SUB AL,CH

SUB CX,[0300H]

SUB DX,4

- Subtra₤₧o

Aritm₫tica

Sintaxe:

SBB OP_DEST,OP_DEST

EX.:

SBB AL,CH

SBB CX,[0300H]

SBB DX,4

- Subtra₤₧o com vem um

Aritm₫tica

Sintaxe:

DEC OP_DEST

EX.:

DEC AL

DEC [BX]

DEC [0400H]

- Decremento

Aritm₫tica

Sintaxe:

CMP OP_DEST,OP_DEST

EX.:

CMP AL,CH

CMP CX,[0300H]

CMP DX,4

- Compara₤₧o

Aritm₫tica

Sintaxe:

CMPXCHG OP_DEST, OP_FONTE - compara e permuta

Compara o operando destino com o acumulador e caso o acumulador seja

igual ao operando destino, o operando fonte ₫ copiado no destino. Caso

sejam diferentes, o valor do acumulador ₫ substituído pelo valor do

destino.

10

10

AL

BL

30

CL

EX.: CMPXCHG BL,CL

CMPXCHG CX,[0300H]

CMPXCHG EDX,EBX

10

30

30

AL

BL

CL

10

20

AL

BL

CL

20

20

30

AL

BL

30

CL

Aritmética

Sintaxe:

MUL OP_FONTE

EX.:

MUL BL

MUL DX

MUL ECX

- multiplicação

Aritmética

Sintaxe:

IMUL OP_FONTE

EX.:

IMUL BL

IMUL DX

IMUL ECX

- multiplicação sinalizada

Aritmética

Sintaxe:

DIV OP_FONTE

EX.:

DIV BL

DIV DX

DIV ECX

- divisão

Aritmética

Sintaxe:

IDIV OP_FONTE

EX.:

IDIV BL

IDIV DX

IDIV ECX

- divisão sinalizada

Aritm₫tica

Sintaxe:

NEG OP-DEST - complemento de dois

EX.:

NEG AL

NEG [0200H]

NEG DX

Aritm₫tica

Sintaxe:

CBW

- converte byte de AL em palavra

etendendo-se o sinal

CWD

- converte a palavra de AX em duplapalavra estendendo-se o sinal (DX:AX)

CWDE - converte a palavra de AX em duplapalavra estendendo-se o sinal (EAX)

CDQ

- converte a dupla-palavra de EAX em

quádrupla-palavra estendendo-se o sinal

(EDX:EAX)

EX.: CBW

CWDE

CWD

CDQ

Aritm₫tica

Sintaxe:

DAA

- ajuste decimal para adi₤₧o (BCD

compactado)

EX.:

MOV AL,15H

MOV BL,25H

ADD AL,BL

;AL=3AH

DAA

;AL=40H

Aritm₫tica

Sintaxe:

DAS

- ajuste decimal para subtra₤₧o (BCDcompactado)

EX.:

MOV AL,10H

MOV BL,02H

SUB AL,BL

;AL=0EH

DAS

;AL=08H

Aritm₫tica

Sintaxe:

AAA

- ajuste ASCII para adi₤₧o

EX.:

MOV AX,0033H

MOV BL,39H

ADD AL,BL

;AL=6CH

AAA

;AX=0102H

Aritm₫tica

Sintaxe:

AAS

- ajuste ASCII para subtra₤₧o

AAM

- ajuste ASCII para multiplica₤₧o

AAD

- ajuste ASCII para divis₧o

Lógica e Manipulação de Bit

Instruções Lógicas

– NOT

– AND

Algumas Instruções Manipulação de bit

– SHL/SAL

- desloc. esquerda

– SHR

- deslc. direita

– SAR

– OR

– XOR

– TEST

– ROL

– ROR

– RCL

– RCR

- rotação

Lógicas

Sintaxe:

NOT OP-DEST

- complemento de um

EX.:

NOT AL

NOT [0200H]

NOT DX

Lógicas

Sintaxe:

AND OP_DEST,OP_FONTE

EX.:

AND AL,CH

AND CX,[SI]

AND DX,FFFFH

- opera₤₧o lógica e

Lógicas

Sintaxe:

OR OP_DEST,OP_FONTE

EX.:

OR AL,00H

OR CX,[SI]

OR DX,FFFFH

- opera₤₧o lógica ou

Lógicas

Sintaxe:

XOR OP_DEST,OP_FONTE - opera₤₧o lógica ou exclusivo

EX.:

XOR AL,CH

XOR CX,[SI]

XOR DX,DX

Lógicas

Sintaxe:

TEST OP_DEST,OP_FONTE

EX.:

TEST AL,CH

TEST CX,[SI]

TEST DX,FFFFH

- opera₤₧o lógica e

Lógicas

Sintaxe:

SETcc OP_DEST

- atribui 01 a operando destino se a condi₤₧o

testada for verdadeira. Caso contrário,

atribui-se 00.

EX.:

SETZ AL

SETLE AX

SETNC DX

Lógicas

Sintaxe:

BSF/BSR OP_DEST,OP_FONTE - procura pelo 1°bit igual a um no

operando fonte a partir do LSB ou MSB. A posi₤₧o encontrada será informada

em operando destino.

OP_DEST deve ser REG. de 16 ou 32 bits

OP_FONTE deve ser REG. ou mem de 16

ou 32 bits

EX.:

BSF EAX,EBX

Lógicas

Sintaxe:

BT/BTC,BTS,BTR OP_DEST,OP_FONTE - testa, complementa,

seta ou reseta um bit do operando destino especificado no opernado fonte.

OP_DEST deve ser REG. de 16 ou 32 bits

OP_FONTE deve ser REG. ou mem de 16

ou 32 bits

EX.:

BT AX,BX

BTC AX,15

BTS AX,1

BTR AX,0

Laços, Desvios, Subrotinas e

Interrupções

Laços e Desvios

– JMP

– Jcc

-desvio incondicional

- desvio condicional

– JCXZ

– LOOP - laço

– LOOPE

– LOOPNE

Subrotinas e Interrupções

– CALL

- subrotinas

– INT

- interrupções

– INTO

– RET

– IRET

- retorno

Controle

– CLC

– STC

– CMC

– CLD

– STD

– CLI

– STI

- Limpa CF

- Faz CF=1

- Complementa CF

- Limpa DF

- Faz DF=1

- Limpa IF

- Faz IF=1

Controle

Sintaxe:

HLT

- Parada

Para o sistema. O processador fica neste estado at₫ ocorrer um reset ou uma

interrup₤₧o NMI ou INTR.

Controle

Sintaxe:

LOCK

- Instru₤₧o prefixo

Bloqueia o barramento

EX.: LOCK XCHG

Sintaxe:

NOP

N₧o executa nada.

- No operation

Strings

Sintaxe:

REP

- Instru₤₧o prefixo

Repete enquanto CX for diferente de zero. Deve ser usada antes das

instru₤ões MOVS, STOS, INS e OUTS

EX.: REP MOSVB

Strings

Sintaxe:

REPE/REPZ

- Instru₤₧o prefixo

Repete enquanto CX for diferente de zero e ZF = 1. Deve ser usada antes das

instru₤ões C,MPS e SCAS.

EX.: REPE CMPSB

Strings

Sintaxe:

REPNE/REPNZ

- Instru₤₧o prefixo

Repete enquanto CX for diferente de zero e ZF = 0. Deve ser usada antes das

instru₤ões C,MPS e SCAS.

EX.: REPNE SCASW

Strings

Sintaxe:

MOVS/ MOVSB/ MOVSW/ MOVSD

- move

Move o elemento apontado por SI no segmento de dados para área

apontada por dI no segmento de extra. DI e SI ser₧o

incrementados ou decrementados de 1, 2, 0u 4 dependendo do flag

DF e do tipo do dado.

EX.:

MOV AX,0300H

MOV ES,AX

XOR DI,DIH

MOV AX,0500H

MOV DS,AX

XOR SI,SIH

MOV CX,5H

CLD

MOV AL,4EH

REP MOVSB

Strings

Sintaxe:

CMPS/ CMPSB/ CMPSW/ CMPSD

- compara

Compara o elemento apontado por DI no segmento extra com o

elemento apontado por SI no segmento de dados. DI e SI ser₧o

incrementados ou decrementados de 1, 2, 0u 4 dependendo do flag

DF e do tipo do dado.

EX.:

MOV AX,0300H

MOV ES,AX

XOR DI,DIH

MOV AX,0500H

MOV DS,AX

XOR SI,SIH

MOV CX,5H

CLD

MOV AL,4EH

REPE CMPSB

Strings

Sintaxe:

SCAS/ SCASB/ SCASW/ SCASD

- scan

Compara o elemento apontado por DI no segmento extra com o

conteúdo do acumulador (AL,AX ou EAX). DI será incrementado

ou decrementado de 1, 2, 0u 4 dependendo do flag DF e do tipo do

dado.

EX.:

MOV AX,0300H

MOV ES,AX

MOV DI,6H

MOV CX,6H

STD

MOV

AL,4EH

REPNZ SCASB

Strings

Sintaxe:

LODS/ LODSB/ LODSW/ LODSD

- carrega

Carrega o elemento apontado por SI no segmento de dados no

acumulador (AL,AX ou EAX). SI será incrementado ou

decrementado de 1, 2, 0u 4 dependendo do flag DF e do tipo do

dado.

EX.:

MOV AX,0510H

MOV DS,AX

MOV SI,5H

STD

LODSW

Strings

Sintaxe:

STOS/ STOSB/ STOSW/ STOSD

- armazena

Armazena na área apontada por DI no segmento de extra o conteúdo

do acumulador (AL,AX ou EAX). DI será incrementado ou

decrementado de 1, 2, 0u 4 dependendo do flag DF e do tipo do

dado.

EX.:

MOV AX,04A8H

MOV ES,AX

MOV DI,8H

CLD

MOV AL,’M’

REP STOSB

Diretivas do Macro-Assembler

Programa .EXE

– Tamanho:

Programa .COM

memória total

– Ponto de Entrada: qualquer ponto

64 Kbytes

offset 100h

– Arquivo produzido

deve ser convertido

pelo link:

executável

pelo EXE2BIN

– PSP:

apontado por DS

nos 100h bytes iniciais

e ES

do segmento

Formato de um Programa .EXE

S1 SEGMENT STACK ‘STACK’

DW 100 DUP(?)

S1 ENDS

D1 SEGMENT

DEFINIÇÃO DE VARIÁVEIS

D1 ENDS

C1 SEGMENT

ASSUMECS:C1, DS:D1,ES:D1,SS:S1

P1

PROC FAR

MOV AX,D1

MOV DS,AX

MOV ES,AX

CoRPO DO PROGRAMA

MOV AH,4CH

INT 21H

P1

ENDP

R1

PROC NEAR

CORPO DA ROTINA

RET

R1 ENDP

C1 ENDS

END P1

Formato de um Programa .COM

C1 SEGMENT

ASSUMECS:C1, DS:C1,ES:C1,SS:C1

ORG 100H

I: JMP P1

DEFINIÇÃO DE VARIÁVEIS

P1 PROC NEAR

CORPO DO PROGRAMA

MOV AH,4CH

INT 21H

P1 ENDP

R1 PROC

CORPO DA ROTINA

RET

R1 ENDP

C1 ENDS

END

Diretivas do Macro-Assembler

COMMENT - INSERÇÃO DE COMENTÁRIO

– FORMATO: COMMENT * COMENTÁRIO *

– EXEMPLO: COMMENT * MEU PRIMEIRO PROGRAMA*

ASSUME - INFORMA AO MONTADOR A FUNÇÃO DE CADA

SEGMENTO.

– FORMATO: ASSUME REG_SEG:NOME_SEG, ..., REG_SEG:NOME_SEG

– EXEMPLO: ASSUME CS:C1,DS:D1,ES:D2,SS:S1

ORG - ESPECIFICA O ENDEREÇO PARA UMA INSTRUÇÃO OU DADO.

– FORMATO: ORG EXPRESSÃO

– EXEMPLO: ORG 100H

Diretivas do Macro-Assembler

SEGMENT - DEFINE SEGMENTO

– FORMATO:

NOME SEGMENT [ALINHM.][COMB.][CLASSE]

– ALINHAMENTO: Define onde inicia o segemento

BYTE - 1° byte livre

WORD - 1° endereço par livre

DWORD - 1° endereço divisível por 4 livre

PARA - 1° endereço divisível por 16 livre

PAGE - 1° endereço divisível por 256 livre

Diretivas do Macro-Assembler

SEGMENT - DEFINE SEGMENTO

– FORMATO:

NOME SEGMENT [ALINHM.][COMB.][CLASSE]

– COMBINAÇÃO: Define como combinar segmentos de mesmo nome

PUBLIC - concatena todos os segementos de mesmo nome

de forma a se obter um único segemento

STACK - O mesmo que o tipo PUBLIC. Para segementos

de pilha.

COMMOM - cria um segmento pela superposição de

segmentos com mesmo nome.

AT endereço - define o endereço inicial de um segemento.

Este segmento não contém inicialização de

dados o código. Usado para definir um

segmento em uma área de dados ou código

Diretivas do Macro-Assembler

SEGMENT - DEFINE SEGMENTO

– FORMATO:

–

NOME SEGMENT [ALINHM.][COMB.][CLASSE]

CLASSE: Define que os segmentos, embora de nomes diferente, mas de mesma

classe, devem ser agrupados na linkedição.

‘CODE’

‘DATA’

‘STACK’

Diretivas do Macro-Assembler

ENDS - FINALIZAÇÃO DE SEGMENTO

– FORMATO:

NOME ENDS

– EXEMPLO:

INICIO SEGMENT

P1

P1

PROC FAR

...

CALL ROT

...

RET

ENDP

ROT

ROT

PROC NEAR

....

RET

ENDP

INICIO ENDS

Diretivas do Macro-Assembler

END - Finalização do programa

– FORMATO:

END nome

nome é o ponto de entrada do programa.

Diretivas do Macro-Assembler

DEFINIÇÃO DE ÁREA DE ARMAZENAMENTO

DB - DEFINE COMO BYTE

DW - DEFINE COMO WORD

DD - DEFINE COMO DOUBLE WORD

DQ - DEFINE COMO QUADWORD

DT - DEFINE COMO DEZ BYTES

– FORMATO: NOME DB/DW/DD/DQ/DT VALOR/LISTA DEVALORES

– EXEMPLO:

X

DB

2AH

LISTA DB

30D,43D,74D

Y

DW

402BH

Z DB 01001110B

Diretivas do Macro-Assembler

EQU - DEFINE CONSTANTE

– FORMATO: NOME

EQU

VALOR

– EXEMPLO:

CONST1

EQU 0

CONST2

EQU 4

CONST3

EQU CONST2 + 3

BYTE/WORD/..../NEAR/FAR PTR - FORÇA EXPRESSÃO A SER DE

UM TIPO BYTE, WORD, ....OU GERAR UM CÓDIGO DO TIPO NEAR OU FAR.

– FORMATO:

BYTE/WORD/DWORD/QWORD/TBYTES/NEAR/FAR PTR EXPRESSÃO

EXEMPLO:

X DB 02H

ROT PROC NEAR

MOV AX,WORD PTR X

....

CALL FAR PTR ROT

RET

...

ROT ENDP

Diretivas do Macro-Assembler

SHORT - USANDO-SE EM UMA INSTRUÇÃO JMP FAZ COM QUE O

MONTADOR GERE UM CÓDIGO SEJA DE APENAS DOIS BYTES. O

DESVIO NÃO PODE SER SUPERIOR A -128 OU +127 BYTES.

– FORMATO:

JMP

SHORT

NOME

OFFSET - FORNECE O DESLOCAMENTO DE UMA VARIÁVEL OU

RÓTULO DENTRO DO SEGMENTO ONDE ESTÁ DEFINIDO.

–

FORMATO:

OFFSET EXPRESSÃO

–

EXEMPLO: MENS DB

MOV DX,OFFSET MENS

‘Bom Dia$

SEG - FORNECE O SEGMENTO DE UMA VARIÁVEL OU RÓTULO.

– FORMATO:

– EXEMPLO :

SEG EXPRESSÃO

MOV AX, SEG MENS

Diretivas do Macro-Assembler

ESTRUTURAS - É uma coleção de objetos (dados) os quais

podem ser lidos/escritos como um único objeto. Os dados de uma

estrutura podem ter diferentes tamanhos e podem acessados

simbolicamente.

–

–

FORMATO DA DECLARAÇÃO:

nome struc

declarações

nome ends

FORMATO DA DEFINIÇÃO DA VARIÁVEL

[nome] nome_da_estrutura <[valor_inicial [,valor_inicial]]>

Diretivas do Macro-Assembler

ESTRUTURAS -

date STRUC

month

db

?

day

db

?

year

dw

?

CODIGO

SEGMENT

PARA 'CODE'

ASSUME CS:CODIGO,DS:DADOS,SS:PILHA

INICIO PROC

FAR

date ENDS

DADOS

SEGMENT

date

<09,03,2000>

today

date

<09,04,2000>

tomorrow

date

<09,05,2000>

anotherday

date

<>

someotherdays date 20 DUP (<>)

ENDS

AX,DADOS

DS,AX

MOV

MOV

MOV

MOV

LEA

MOV

AL,yesterday.day

AH,today.day

DL,tomorrow.day

anotherday.day,DL

BX,someotherdays

[BX].day,dl

PARA 'DATA'

yesterday

DADOS

MOV

MOV

Diretivas do Macro-Assembler

MACRO - Possibilita atribuir um nome a um bloco de código e

utiliza-lo, através deste nome, no seu programa.

–

FORMATO DA DECLARAÇÃO:

nome macro [parâmetro[,parâmetro]]

statements

nome endm

–

FORMATO PARA CHAMAR A MACRO

nome [argumento [,argumento]]

Diretivas do Macro-Assembler

MACRO -

DADOS

SEGMENT

RenataN1

db

06

RenataN2

db

08

Renatatpontos

db

?

DADOS

SEGMENT PARA 'CODE'

PARA 'DATA' CODIGO

ASSUME CS:CODIGO,DS:DADOS,SS:PILHA

ENDS

totalpontos MACRO n1,n2

MOV AL,n1

MOV AH,n2

CLC

ADD AH,AL

ENDM

INICIO PROC

MOV

MOV

FAR

AX,DADOS

DS,AX

totalpontos RenataN1,RenataN2

MOV Renatatpontos,AH

MOV AH,4CH

INT 21H

INICIO ENDP

CODIGO ENDS

END

INICIO

Interrupções

O

que é uma interrupção?

– É um evento interno ou externo ao

processador provocado por um usuário

que solicita sua atenção.

Quais

os tipos de interrupção?

– Interrupções por software

» Instruções INT

– Interrupções por hardware

» NMI

» IRQ’s conectadas ao pino INTR

– Exception Handlers (Int. Excepcionais)

Arquitetura de Computadores

Interrupções

– Hardware

– Software

na Arquitetura x86

Internas

Externas

Mascarável

Não-Mascarável

Sistema Operacional

Usuário

Interrupções

Exemplos

de Exception Handlers

– Erro irrecuperável de HW;

– Divisão por zero;

– Breakpoint;

– Passo a Passo;

– Overflow;

– Violação dos limites da memória.

Resposta do Processador

a uma Interrupção

PUSH FLAGS

CLEAR IF

CLEAR TF

PUSH CS

PUSH IP

FETCH ISR ADDRESS

INTERRUPT

SERVICE

PROCEDURE

PUSH REGISTERS

POP IP

POP CS

POP FLAGS

POP REGISTERS

IRET

Vetores de Interrupção

Processadores da Família 8086

INT (Hex)

00 - 01

02

03 - 07

08

09

0A

0B

0C

0D

0E

0F

10 - 6F

70

71

72

73

74

75

76

77

78-FF

IRQ

Exeption Handlers

Non-Maskable IRQ

Exeption Handlers

Hardware IRQ0

Hardware IRQ1

Hardware IRQ2

Hardware IRQ3

Hardware IRQ4

Hardware IRQ5

Hardware IRQ6

Hardware IRQ7

Software Interrups

Hardware IRQ8

Hardware IRQ9

Hardware IRQ10

Hardware IRQ11

Hardware IRQ12

Hardware IRQ13

Hardware IRQ14

Hardware IRQ15

Software Interrups

COMMON USES

Non-Maskable IRQ (Parity Errors)

System Timer

Keyboard

Redirected

Serial Comms. COM2/COM4

Serial Comms. COM1/COM3

Reserved / Sound Card

Floppy Disk Controller

Parallel Comms.

Real Time Clock

Redirected IRQ2

Reserved

Reserved

PS/2 Mouse

Math's Co-Processor

Hard Disk Drive

Reserved

-

Controlador de Interrupção

Programável - PIC 8259

Foi

projetado para permitir

priorização e tratamento de

interrupções de dispositivos

periféricos, multiplexando vários

sinais de interrupção na entrada

de interrupção do processador.

Diagrama em Blocos - PIC 8259

Diagrama em Blocos - PIC 8259

Interrupt

Request Register (IRR):

Monitora as entradas de interrupção

para verificar as que estão ativas. Se