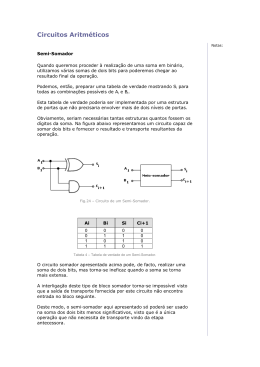

Eletrônica Digital Projeto de Circuitos Combinacionais Aritméticos Prof. Wanderley Introdução São circuitos combinacionais especiais por serem a base de funcionamento das ALUs (Aritmetic Logic Unities) de microprocessadores. Circuitos aritméticos básicos: Meio Somador (Half-Adder) – realiza a soma de dois bits Somador Completo (Full-Adder) – realiza a soma de três bits Subtrator O Meio Somador Considere a operação aritmética abaixo O Meio Somador é capaz de realizar apenas a soma de A0 com B0! O Meio Somador Identificação do Problema Obtenção das expressões Booleanas Construção da tabela verdade Geração do Circuito Lógico O Meio Somador Considere a operação aritmética O Somador Completo é capaz de somar Cn-1, An e Bn, n=1,2,3,... O Somador Completo Identificação do Problema Geração de Sn Construção da tabela verdade O Somador Completo Geração de Sn O Somador Completo Identificação do Problema Geração de Cn Construção da tabela verdade O Somador Completo Geração do Circuito Lógico O Somador Completo a partir de Meio Somadores O Somador Completo a partir de Meio Somadores Da tabela verdade, temos que Cn An Bn Cn 1 An Bn Cn 1 An Bn Cn 1 An Bn Cn 1 Cn 1 An Bn An Bn An Bn Cn 1 Cn 1 Cn 1 An Bn An Bn O Somador Completo a partir de Meio Somadores Como Cn Cn 1 An Bn An Bn Então, o circuito do somador completo a partir de meio somadores se reduz a O Somador de 4 Bits Observe que os Carrys se propagam. Isso demanda um tempo precioso! O Somador de 8 Bits A medida que o número de bits a serem somados aumenta, aumenta também o tempo de transporte de carry! Geração Antecipada de Carry A medida que o número de bits a serem somados aumenta, aumenta também o tempo de transporte de carry! Como solução, podemos projetar circuitos somadores com vai um antecipado. Geração Antecipada de Carry Geração Antecipada de Carry Geração Antecipada de Carry Geração Antecipada de Carry Geração Antecipada de Carry O Complementador a 2 Foi visto em aulas passadas que a operação de subtração de números binários pode ser transladada a uma operação de soma envolvendo o complemento do número negativo. Logo, em termos de circuito, se agregarmos um complementador a 2 ao circuito somador já existente, obteremos um subtrator. O Complementador a 2 O Complementador a 2 O Complementador a 2 O Complementador a 2 O Complementador a 2 O Complementador a 2 Na prática, implementa-se como segue O Subtrator de 4 Bits em Complemento de 2 Considerando Minuendo (M) ≥ Subtraendo (S) Há estouro! O Subtrator de 4 Bits em Complemento de 2 Considerando Minuendo (M) < Subtraendo (S) Neste caso não há estouro, isto é, C4=0. Neste caso o resultado da soma M+C2S deve passar por um novo complemento de 2, isto se o objetivo for obter a real magnitude da subtração. Em operações internas de computador, resultados negativos permanecem complementados a 2. True/Complement True/Complement para Restaurar a Magnitude do Resultado Somador/Subtrator de 4 Bits

Download