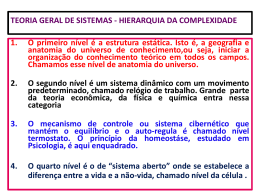

Latches e Flip-Flops (1/2) Material cedido por: ANTONIO AUGUSTO LISBOA DE SOUZA Latches e Flip-Flops (1/2) 1 Plano da aula • Introdução aos Circuitos Sequenciais • Princípio de construção de células de memória • Latch RS implementado com NAND • Latch RS implementado com NOR • Latch RS controlado (gated) Latches e Flip-Flops (1/2) 2 Circuitos Sequenciais Circuitos Combinacionais: saídas dependem apenas das entradas atuais Ai Bi Ai 0 0 1 1 Meio Somador Exemplo visto: Ci+1 Bi 0 1 0 1 Si 0 1 1 0 C i+1 0 0 0 1 Si Meio Somador Binário Tabela Funcional Circuitos sequenciais: saídas dependem das entradas atuais e do “histórico” de entradas passadas (estado atual). + 1s + 1s + 1s Exemplo: relógio 10:52:58 10:52:59 10:53:00 10:53:01 + [(24·3600)-3]s Como armazenar o estado atual?? Latches e Flip-Flops (1/2) 3 Circuitos Sequenciais Como armazenar o estado atual?? Resp.: Usando células de memória!! Célula de memória genérica Latches e Flip-Flops (1/2) 4 Circuitos Sequenciais Exemplos de configuração de sinais de entrada: Q n Entradas de dados Célula de Mem ória Q Nesta configuração, o estado da célula de memória pode mudar (de acordo com as entradas de dados) no instante em que as entradas de dados mudam Entradas de dados Entrada de c ontrole n Q Célula de Mem ória Q Nesta configuração, o estado da célula de memória pode mudar (de acordo com as entradas de dados) no instante em que a entrada de controle habilita a mudança (acionamento) Latches e Flip-Flops (1/2) 5 Circuitos Sequenciais Q n Entradas de dados Célula de Mem ória Q Entradas de dados n Entrada de c ontrole Q Célula de Mem ória Q Circuitos digitais podem ser síncronos ou assíncronos. Os circuitos síncronos são aqueles em que as células de memória podem mudar de estado apenas em um “determinado” instante: existe a necessidade de um sinal de “relógio” global (CLOCK) como sinal de controle para todas as células de memória. Circuitos assíncronos são os que não atendem a este requerimento: podem ser formados por células de memórias sem entradas de controle, ou onde as entradas de controle não são “globais”. Latches e Flip-Flops (1/2) 6 Circuitos Sequenciais Latches e Flip-Flops (1/2) 7 Princípio de construção de células de memória Circuitos típicos vistos até agora: Perceba que a saída de uma porta alimenta a entrada de outra. Como então fazer com que um circuito armazene sua saída?? Latches e Flip-Flops (1/2) 8 Princípio de construção de células de memória Como então fazer com que um circuito armazene sua saída?? Resp.: usando realimentação! O que aconteceria ao ligar o circuito abaixo? Este circuito tem alguma serventia? Latches e Flip-Flops (1/2) 9 Princípio de construção de células de memória QUIZ em sala: como funciona este circuito? SET Q Q RESET LATCH RS Latches e Flip-Flops (1/2) 10 Princípio de construção de células de memória Latches e Flip-Flops (1/2) 11 Latch RS implementado c/ NAND Nível Baixo Ativo (NBA) Latches e Flip-Flops (1/2) 12 Latch RS implementado c/ NAND Latches e Flip-Flops (1/2) 13 Latch RS implementado c/ NOR Nível Alto Ativo (NAA) Latches e Flip-Flops (1/2) 14 Exemplo de aplicação do Latch RS Problema com chaves Latches e Flip-Flops (1/2) 15 Latch RS Controlado (Gated) Compare com a Configuração vista: Latches e Flip-Flops (1/2) 16 Latch RS Controlado (Gated) NAA NBA Exemplo c/ controle NAA: Latches e Flip-Flops (1/2) 17 Exercício: Trazer na próxima aula Questão ENADE 2005 (e prova 2009.2): Importante: considere que dois sinais nunca ocorrem no mesmo instante, ou seja, em transições “simultâneas”, o R pode mudar antes do S ou vice-versa (fora do seu controle). Latches e Flip-Flops (1/2) 18

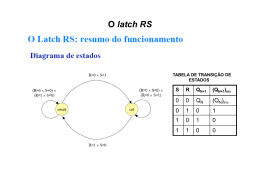

Download