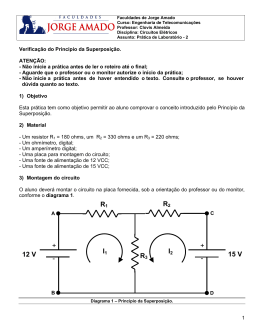

Soluções dos exercícios TTL 1 – O circuito que executa a função lógica Y=(A.B+C.D)’ é o seguinte: VCC VCC R RC QA A QB B Q1 VCC Y R QC C QD D Q2 De acordo com a função dada, a saída Y apresenta nível baixo somente quando as entradas A e B, C e D ou todas estiverem em nível alto ao mesmo tempo. Analisando o circuito, a saída Y é igual a 0V, quando um dos transistores Q1, Q2 ou ambos estiverem conduzindo. Para que o transistor Q1 entre em condução, é necessário que ambos os transistores de entrada QA e QB estejam em nível alto, pois neste caso a corrente que passa pelo resistor R é injetada na base de Q1. Com Q1 saturado, a tensão de saída é igual a VCEsat do transistor Q1, que equivale ao nível lógico 0. Quando uma das entradas A ou B, ou ambas, estiverem em nível baixo a corrente que passa pelo resistor R é desviada para o emissor do transistor de entrada (QA e QB), e assim nenhuma corrente é injetada na base de Q1. Neste caso o transistor fica polarizado na região de corte e a tensão na saída é VCC (sem nenhuma carga conectada na saída). A mesma análise vale para o circuito formado pelos transistores QC, QD e Q2. Assim, o circuito corresponde a função lógica dada. 2 – A figura abaixo mostra a tensões nos nós do circuito TTL. A tensão no resistor de 1kΩ é 0,7V. Assim a corrente que passa pelo por este resistor é dada por: I1k = 0,7 = 0,7 mA 1k A tensão no coletor de Q2 é a soma das tensões VBEQ3 com VCEsatQ2. Assim a corrente no resistor de 1,6kΩ é dada por: I1,6 k = VCC − (VBEQ3 + VCEsatQ 2 ) 1,6k = 5 − (0,7 + 0,2 ) = 2,56mA 1,6k VCC VCC VCC 4k 1,6k VCC 130 Q4 0,9V RL 1k 2,1V Vi 1,4V Q2 D Q1 0,7V Q3 A 1k O transistor de entrada Q1, com a entrada em nível alto esta trabalhando no modo reverso, ou seja, com o coletor e o emissor trocados. Assim, a corrente que passa no resistor de 4kΩ vai para a base de Q2. Está corrente é dada por: I 4k = VCC − VBQ1 4k = 5 − 2,1 = 0,725mA 4k A corrente que é drenada na entrada do inversor com nível lógico alto é dado por: Iin1 = βRI4k = 0,05.0,725 = 0,036mA Assim a corrente na base de Q2 é dada por: IBQ2 = Iin1+ ICQ2 = 0,036 + 0,725 = 0,761mA Assim, a corrente no emissor de Q2 é a soma das correntes I4k e I1,6k, que são respectivamente as correntes na base e no coletor de Q2. Assim, temos: IEQ2 = IBQ2 + ICQ2 = 0,761 + 2,56 = 3,321mA A corrente na base do transistor Q3 é a soma das correntes que entram e saem do nó A. Assim, IBQ3 é dada por: IBQ3 = IEQ2 - I1k = 3,321-0,7 = 2,621mA Observe que se Q2 está conduzindo, não há corrente na base do transistor Q4 e neste caso este transistor está cortado. Finalmente a corrente no resistor de carga, para VCEsatQ3=0,2V é dada por: I RL = VCC − VCEsatQ 3 1k = 5 − 0,2 = 4,8mA 1k O valor máximo de corrente de carga que mantém o transistor Q3 na saturação é dado por: IRLMAX = βIBQ3 = 9.2,621 = 23,589mA A pior situação par calcular o fanout é quando o circuito alimenta outra porta lógica com nível lógico baixo, pois quando o nível lógico da entrada da porta de carga for alto, a corrente drenada por esta porta é βRI4k. Quando a entrada do circuito está em nível lógico baixo, a corrente drenada na entrada do circuito é dada por: VCC − VBQ1 5 − 0,9 = = 1,025mA I in 0 = 4k 4k Assim, o fanout para o inversor TTL analisado é dado por: N= I RLMAX 23,589 = ≈ 23 I in 0 1,025 3 – A figura abaixo mostra o circuito do exercício 3 com 4 portas de entrada NOR. A máxima corrente na base de Q3 ocorre quando todas as entradas estiverem em nível alto, pois desta maneira os transistores da entrada estarão operando no modo inverso, injetando corrente na base dos transistores Q2, levando-os a condução. VCC VCC 4k VCC 4k VCC 1,6k VCC 4k VCC 4k 130 Q8 D Q2A A B Q1A Q2B C D Q1B Q2C E F Q1C Q2E G H Out Q1D Q3 1k Vamos determinar a corrente em 1 entrada NOR. Assim, considerando a entrada formada por Q2A, a corrente de base deste transistor é dada por: VCC − VBEQ3 − VBEQ 2 A − VCBQ1A 5 − 0,7 − 0,7 − 0,7 = = 0,725mA I BQ 2 A ≈ I 4 k = 4k 4k A corrente no resistor de 1,6kΩ é dada por: I1,6 k = VCC − VCEQ 2 B − VBE 3 1,6k = 5 − 0,2 − 0,7 = 2,56mA 1,6k A corrente no resistor de 1kΩ é dada por: I1k = VBEQ3 1k = 0,7 = 0,7mA 1k Portanto a corrente máxima na base do transistor Q3 é dada por: IBQ3MAX=4IBQ2+I1,6k-I1k = 4.0,725 + 2,56 - 0,7 = 4,76mA Para três entradas em nível lógico baixo, apenas um transistor Q2 contribui com a corrente IBQ3. IBQ3 = IBQ2+I1,6k-I1k = 0,725 + 2,56 - 0,7 = 2,585mA O tempo de atraso é dado por: t s = τs I B2 − IC I B1 − IC β β Para as quatro entradas em nível baixo, IC=0. Assim, para τs=10ns, o tempo de atraso é dado por: t s = 10.10 −9 I B2 4,76 = 10.10 −9 = 17,8ns I B1 2,585

Download