Sistemas Digitais (Part III)

Page 1 of 111

Sistemas Digitais (Part III)

Page 2 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 3 of 111

16aº Projecto

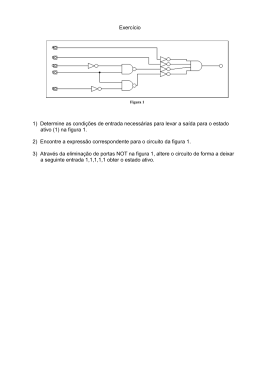

Esta é a primeira sessão dedicada à Síntese de Circuitos Sequenciais Síncronos, isto é, ao desenho de Circuitos

Sequenciais com flip-flops recebendo directamente impulsos de relógio da mesma fonte... Tal como as demais

sessões, ir-se-á partir de um Projecto concreto…

Considere-se um condutor que, para abrir a porta da viatura, recorre a um dispositivo de controlo remoto: clicao, e ele emite repetidamente, por rádio frequência (RF), e ao ritmo do relógio, a sequência de bits ‘1011’.

Ao lado, apresenta-se o diagrama temporal representativo da sequência referida – e o objectivo é precisamente

desenhar um circuito sequencial síncrono capaz de o gerar.

O essencial na Síntese de Circuitos Sequenciais Síncronos é discernir os Estados que o circuito pode assumir –

e como é que de um deles se transita para os outros. No caso entre mãos, é claro que o circuito vai passando

ciclicamente por quatro estados, denominem-se eles de {A, B, C e D}. Mais ainda: em cada momento, tanto a

evolução do circuito (por outras palavras: qual o estado seguinte?) como a saída, seja ‘Z’, dependem só do estado

em que o circuito se encontra. Um circuito assim diz-se autónomo: não contando, é claro, com o sinal de relógio,

não há quaisquer entradas externas, o seu estado é a única “entrada” de que a saída depende.

Em Projectos não tão simples, será exigir muito ao intelecto humano discernir sem mais quais os Estados

possíveis do circuito, e a relação entre eles – pelo que a praxis recomendável é começar pelo desenho do seu

Diagrama de Estados. Este deve, aliás, ser considerado o ponto crítico no desenho de um Circuito sequencial

síncrono: o que se lhe segue é automático – já que não será difícil conceber software que, recebendo como input

tal Diagrama, indique como se deverão interligar flip-flops e chips combinatórias para concretizar o circuito.

1. Considere-se o momento em que o condutor clica no seu dispositivo de controlo… Conforme ao enunciado,

o circuito deverá ingressar num estado – seja ‘A’ – em que irá produzir ‘1’ na saída; fá-lo-á até ao próximo impulso

de relógio (doravante, substitui-se impulso de relógio por, mais brevemente, clock). Graficamente,

– esse estado representa-se por um círculo nomeado por, embora não obrigatoriamente, uma maiúscula, ‘A’;

– a saída, ‘1’, é indicada no seio do círculo, precedida pelo símbolo ‘/’;

– o caracter inicial do estado é denotado por uma seta dirigida da esquerda para o próprio círculo.

2. Admita-se agora que ocorre um clock. Conforme ao enunciado, o circuito deverá ingressar num novo estado,

‘B’, em que irá produzir ‘0’. Graficamente,

– esse estado e saída representam-se como acima: um círculo nomeado ‘B’, em cujo seio se indica a saída ‘0’;

– a transição, entre os estados ‘A’ e ‘B’, representa-se por uma seta dirigida do círculo ‘A’ para o círculo ‘B’.

3. Com outro clock, o circuito irá ingressar num novo estado, ‘C’, em que irá gerar ‘1’. Intui-se como é que isso

se representa: uma seta dirigida de ‘B’ para um novo círculo, ‘C’, apropriadamente rotulado…

4. E com um novo clock, o circuito irá ingressar num novo estado, ‘D’, continuando a gerar o bit ‘1’. Isso

representa-se por uma seta dirigida de ‘C’ para um novo círculo, ‘D’, adequadamente rotulado…

5. Com o próximo clock, o circuito irá regressar ao estado inicial, ‘A’, continuando a gerar o bit ‘1’. Isso

representa-se por uma seta dirigida do círculo ‘D’ para o círculo ‘A’ …

O diagrama de estados ocupa uma superfície de papel não despicienda, pelo que se prefere convertê-la numa

bem mais compactada Tabela de Estados/Saída. Esta é constituída, de facto, por duas Tabelas:

– uma que indica, para cada estado actual ‘Q(t)‘, qual a saída actual, ‘Z(t)‘;

– e uma outra que indica, para cada estado actual ‘Q(t)‘, qual o estado seguinte, ‘Q(t+1)‘.

Na prática, dispõe-se:

– à esquerda uma coluna, ‘Q(t)‘, onde se listam, linha a linha, os estados que constam no diagrama de estados;

– à direita, duas colunas, ‘Z(t)‘ e ‘Q(t+1)‘, em que, linha a linha, se inscreve a saída e o estado seguinte, tais como

o indicam o diagrama de estados.

Por exemplo, o diagrama de estados indica que, para o estado actual ‘B’, a saída é ‘0’ e o estado seguinte é ‘C’;

isso volve-se em escrever, na linha ‘B’ da Tabela de Estados/Saída: ‘0’ na coluna de ‘Z(t)’ e ‘C’ na coluna ‘Q(t+1)’.

(Na vida real, e para maior segurança, os dispositivos de abertura da porta de viaturas geram sequências mais

longas e, aliás, variáveis; mas, para o fim em vista, basta uma sequência fixa de 4 bits, não é preciso complicar…)

Sistemas Digitais (Part III)

Page 4 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 5 of 111

Síntese Clássica com Flip-Flops T

De posse da Tabela de Estados/Saída, resta concretizá-la mediante flip-flops e chips combinatórios: ANDs,

ORs e NOTs, ou só NANDs, ou só NORs, como se fará adiante, ou decoders e ORs, ou multiplexers, etc…

O método de desenho dito clássico visa usar não mais que o menor número de flip-flops capaz de concretizar a

Tabela. A esse respeito, a Tabela ao lado apresenta quatro estados – do que se deduz que serão necessários, e

suficientes, dois flip-flops, designem-se eles de {Q1, Q0}.

Isso decidido, o passo seguinte é proceder à codificação dos estados – isto é, estabelecer uma correspondência

biunívoca entre cada estado e uma combinação particular de dois bits {Q1 Q0}. Aquela que se privilegia ao lado

usa o CBN (Código Binário Natural); mas há outras possibilidades, nomeadamente o código de Gray… De facto,

há muitas mais maneiras de codificar os 4 estados: após escolher, para codificar ‘A’, um dos 4 pares de bits

possíveis, sobram 3 pares; após escolher, para codificar ‘B’, um desses 3 pares, sobram 2 pares; e após escolher,

para codificar ‘C’, um desses 2 pares, resta 1 par, que será usado para codificar ‘D’: um total, portanto, de 4!=24

possibilidades distintas – que, se suspeitará, conduzem a circuito diferentes! Eles poderão ser mais ou menos

complicados – o que recomenda a praxis de explorar várias possibilidades, visando chegar à solução mais simples.

A etapa seguinte é transformar a Tabela de Estados/Saída na assim designada Tabela de Transições e Saídas –

ou preferivelmente, já antevendo o que seguirá, num Mapa de Karnaugh, vidé ao lado: cada literal {A, B, C, D}

designando um estado é substituído pelo par de bits {Q1 Q0} que o codifica…

Obtida essa Tabela de Transições e Saídas, torna-se viável escrever a expressão simplificada da saída ‘Z’ do

circuito; em geral, usar-se-á o método de Karnaugh, mas no caso presente nem isso é preciso: a expressão da POS

é suficiente…

Resta determinar as expressões simplificadas das entradas dos flip-flops – e isso exige, é claro, precisar o tipo

de flip-flop a usar – e de novo se intui que consoante a escolha, assim se obterão circuitos distintos! Poderão ser

mais ou menos complexos – o que recomenda a praxis de explorar várias possibilidades, visando a mais simples…

Admita-se que, neste Projecto, se opta por flip-flops T (advertindo desde já que a seu tempo, e no contexto de

novos Projectos, serão explorados outros tipos de flip-flops); como auxiliar de memória, apresentam-se ao lado o

diagrama de estados do flip-flop T e a correspondente Tabela de Excitação.

O passo imediato será obter a Tabela de Excitações do circuito: para tal, desdobra-se a Tabela de Transições em

duas Tabelas, uma por cada um dos estados seguintes de {Q1, Q0} - e depois substituem-se os valores nas colunas

‘Q1(t+1)’ e ‘Q0(t+1)’ pelos valores a impor nas entradas {T1, T0} para lograr as transições de estado em causa.

Considere-se, por exemplo, a linha em que Q1=0 e Q0=0. O estado seguinte de ‘Q1’ é ‘0’ e o estado seguinte de

‘Q0’ é ‘1’– e isso remete para a pergunta: para que aconteçam essas “transições” em {Q1, Q0}, como se devem

excitar as entradas dos flip-flops? A resposta da Tabela de Excitação do flip-flop T é: a transição ‘0’→‘0’ logra-se

aplicando ‘0’ na entrada ‘T1’ e a transição ‘0’→‘1’ logra-se aplicando ‘1’ na entrada ‘T0’. São precisamente esses

valores, ‘0’ e ‘1’, que se escrevem nas Tabelas de ‘T1’ e ‘T0’.

A etapa final é deduzir as expressões simplificadas das entradas {T1 e T0} dos flip-flops; em geral, usar-se-á o

método de Karnaugh, mas no caso presente nem isso é preciso, basta um olhar atento…

Conhecidas tais expressões, é hora de desenhar o logigrama do circuito com a geografia habitual:

– entradas à esquerda – o que neste caso, em que não há entradas externas, se reduz a dispor à esquerda os dois

flip-flops, ficando ‘Q1’ (a de maior peso) por baixo de ‘Q0’;

– saídas, que neste caso se reduzem a ‘Z’, à direita;

– à direita dos flip-flops: malha combinatória que produz ‘Z’ e os valores que excitam as entradas {T1 T0}

Ainda que não indispensável, convirá etiquetar as linhas com os nomes das funções (por exemplo, ‘T1’) que

“transportam”;

– setas apropriadas nas linhas em que o fluxo se processa da direita para a esquerda ou de baixo para cima;

– entradas de clock dos flip-flops ligadas à mesma fonte de clocks… No logigrama ao lado, pressupõe-se que

eles são edge-triggered comutando no flanco descendente do relógio – mas também seria válido ter-se escolhido

flip-flops edge-triggered comutando no flanco ascendente do relógio.

Sistemas Digitais (Part III)

Page 6 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 7 of 111

Análise de Circuito com Flip-flops T

Quando um Projectista se engaja no desenho de um circuito, e antes de o materializar de facto, e para evitar

posteriores dissabores, há que “fazer a prova dos nove”: será que o circuito concebido segue mesmo o diagrama de

estados desenhado inicialmente? E este passo de maneira nenhuma se deve omitir!

Essa “conferência” deve ser independente do método usado na síntese do circuito – e na prática suporta-se na

Equação característica dos flip-flops usados, como já se testemunhou algures e agora se volta a aplicar:

O circuito envolve dois flip-flops T – cujos estados se designam de {Q1, Q0}. O primeiro passo na análise do

circuito é, a partir do respectivo logigrama, escrever as expressões algébricas que traduzem o comportamento da

saída do circuito e das entradas dos flip-flops, vidé ao lado.

Tendo em mira o desenho do Diagrama de Estados, o segundo passo é substituir as expressões das entradas dos

flip-flops na equação característica do flip-flop T. O resultado são expressões que exprimem o estado seguinte de

cada flip-flop – em função dos estados dos flip-flops no instante em que ocorre o flanco descendente do relógio.

O terceiro passo é converter tais expressões nas assim denominadas Tabelas de Estado/Saída – que indicam,

para cada combinação das entradas internas {Q1, Q0} num instante ‘t’, a saída ‘Z’ do circuito nesse instante, e, a

ocorrer em ‘t’ o flanco descendente do relógio, os estados dos flip-flops no instante ‘t+1’ seguinte.

No total, existirão três Tabelas, para {Z, Q1 e Q0}:

– à esquerda, dispõem-se duas colunas, representando outros tantos flip-flops, {Q1, Q0};

– estando envolvidos dois flip-flops, e pois que cada um pode assumir dois valores {Q=0 e Q=1}, o circuito

poderá assumir quatro estados distintos, que convirá nomear por códigos binários: {‘00’, ‘01’, ‘10’ e ‘11’}.

O preenchimento das Tabelas não deverá provocar engulhos. As expressões de {Z, Q1 e Q0} são claras:

– ‘Z’ será ‘0’ apenas para a combinação Q1=0 e Q0=1;

– ‘Q1(t+1)‘ é o XOR de Q1(t) e Q0(t), pelo que será ‘1’ apenas quando ‘Q1(t)‘ e ‘Q0(t)‘ forem diferentes;

– e ‘Q0(t+1)‘ é o complemento de ‘Q0(t)‘, pelo que a coluna ‘Q0(t+1)‘ será o complemento da coluna ‘Q0(t)‘.

Resta desenhar o Diagrama de Estados: a cada estado, associa-se um círculo, etiquetado com um código

binário; depois, traçam-se setas rotuladas, descrevendo graficamente a Tabela obtida.

Veja-se como exemplo a primeira linha, relativa ao estado ‘00’: a saída é Z=1, e o estado seguinte será ‘01’;

isso volve-se numa seta dirigida do círculo ‘00’ para o círculo ‘01’. Para denotar que, no estado ‘00’, a saída é

Z=1, o correspondente círculo é rotulado por /1.

É hora de o Projectista comparar o diagrama de estados obtido a partir do logigrama do circuito com o

diagrama de estados que ele inicialmente concebeu – e ficar tranquilo, que o circuito a que chegou está ok: afora os

nomes, o número de estados, a interligação entre eles e as saídas são idênticos…

Uma questão que não é de somenos importância é a seguinte: quando se faz o power-on ao circuito, qual o

estado em que ele ingressa? A resposta é: não se sabe, em particular não se pode pressupor que os estados estão a

‘0’ inicialmente! No Projecto entre mãos, isso não terá provavelmente nenhuma importância: qualquer que seja o

estado inicial, entre {‘00’, ‘01’, ‘10’ e ‘11’}, e afora um eventual período transitório, o circuito acaba por gerar

repetidamente, ao ritmo do relógio, a sequência de bits ‘1011’… Mas haverá Projectos em que isso terá mesmo

importância – pelo que então há que recorrer a entradas assíncronas (Preset e Clear) para obrigar a que o estado

inicial seja um específico.

Sistemas Digitais (Part III)

Page 8 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 9 of 111

16bº Projecto

O 16aº Projecto é um sistema autónomo, isto é: não envolve entradas externas. É hora de avançar para um

Projecto já com uma entrada externa…

Admita-se que a abertura da porta de uma viatura pode ser detonada por um dispositivo de controlo remoto. Ela

dispõe dum receptor de RF cuja saída, seja ‘X’, é uma sucessão indefinida de ‘0’s e ‘1’s… Pretende-se um circuito

sequencial síncrono que reporte a detecção da sequência ‘1011’ (Não se consideram sequências sobrepostas).

O ponto crítico para obter um Circuito sequencial síncrono é o desenho do seu Diagrama de Estados:

1. Considere-se o momento em que se faz o power-on… O circuito nada “sabe” então do que se passou antes –

pelo que será pacífico iniciá-lo a um estado em que irá assinalar ‘0’ na sua saída. Graficamente, esse estado

representa-se por um círculo com um nome significativo, como seja ‘S0’, em cujo seio se indica, precedida pelo

símbolo ‘/’, a saída a assinalar, ‘0’, a ser mantida até ao próximo "clock; o caracter inicial do estado é denotado

por uma seta dirigida da esquerda para o círculo ‘S0’.

2. Recorde-se, entretanto, que tal circuito está recebendo, do receptor de RF, uma sucessão de ‘0’ e ‘1’s…

– admita-se que, logo após o power-on, ele recebe um ‘1’; o circuito pode “julgar” que ele é já o primeiro bit do

padrão ‘1011’ – pelo que irá transitar para um novo estado, em que continuará a gerar ‘0’ (pois só passará a gerar

‘1’ quando houver detectado todo o padrão ‘1011’). Essa situação representa-se por um círculo nomeado ‘S1’ (em

cujo seio se indica a saída ‘0’), e uma seta do círculo ‘S0’ para o círculo ‘S1’;

– mas suponha-se, em alternativa, que o primeiro bit a ser recebido é um ‘0’; então, o circuito irá permanecer

no mesmo estado, ‘S0’ – o que se representa por uma seta do círculo ‘S0’ para ele mesmo.

Em consequência, de ‘S0’ “saem” duas setas. Para distinguir o que motiva aquela dirigida para ‘S1’, ela é

rotulada por X=1, ou, conforme à lei do menor esforço, ‘1’; intui-se que a seta dirigida para ‘S0’ é rotulada por ‘0’.

Repare-se que o estado/círculo ‘S0’ fica assim completamente especificado: estando o circuito nesse estado,

sabe-se qual é então a sua saída, e como evolui o circuito se receber, do receptor de RF, um ‘0’ ou um ‘1’…

3. “Resolvido” o estado ‘S0’, considere-se, então, que o circuito se encontra no estado ‘S1’. Sabe-se qual a sua

saída, resta decidir como evolui ele quando receber, do receptor de RF, um ‘0’ ou um ‘1’; não custa descortiná-lo:

– se ele receber um ‘0’, o circuito pode “julgar” que esse é o segundo bit do padrão ‘1011’ – pelo que irá

transitar para um novo estado, em que irá continuar a assinalar ‘0’. Isso representa-se por um círculo nomeado ‘S10’

(onde se indica a saída ‘0’), e uma seta de ‘S1’ para ‘S10’;

– se, porém, receber um ‘1’, irá concluir que estava errada a suposição de que o ‘1’ precedente era o primeiro

bit do padrão ‘1011’ – mas talvez o ‘1’ que acaba de receber o seja; isso remete para uma seta de ‘S1’ para ‘S1’.

Para clarificar o que motiva as setas “saindo” de ‘S1’, elas são devidamente rotuladas – pelo valor de ‘X’ que

conduz à transição de estados que representam…

4. Considere-se, agora, que o circuito se encontra no estado ‘S10’. Como evolui ele quando receber outro bit?

– se receber um ‘1’, o circuito pode “julgar” que esse é o terceiro bit do padrão ‘1011’ – pelo que irá transitar

para um novo estado, em que irá continuar a gerar ‘0’. Isso representa-se por um círculo nomeado ‘S101’ (onde se

indica a saída ‘0’), e uma seta rotulada por ‘1’ de ‘S10’ para ‘S101’;

– se, porém, receber um ‘0’, concluirá que afinal os bits ‘10’ precedentes não eram o começo do padrão ‘1011’:

tem que regressar ao início – o que remete para uma seta rotulada por ‘0’ de ‘S10’ para ‘S0’.

5. Considere-se, agora, que o circuito se encontra no estado ‘S101’. Como evolui ele quando receber outro bit?

– se receber um ‘1’, o circuito conclui que esse é o quarto bit do padrão ‘1011’ – pelo que irá transitar para um

novo estado, seja ‘S1011’, em que irá assinalar ‘1’. Isso representa-se por um círculo nomeado ‘S1011’ (onde se indica

a saída ‘1’), e uma seta rotulada por ‘1’ de ‘S101’ para ‘S1011’;

– se, porém, receber um ‘0’, concluirá que afinal os bits ‘101’ precedentes não eram o começo do padrão ‘1011’

– mas talvez os últimos ‘10’ o sejam, o que remete para uma seta rotulada por ‘0’ de ‘S101’ para ‘S10’.

6. Considere-se, enfim, que o circuito se encontra no estado ‘S1011’. Como evolui quando receber um outro bit?

– se receber um ‘1’, o circuito pode “julgar” que ele é já o primeiro bit de um novo padrão ‘1011’ – pelo que irá

transitar para ‘S1’. Isso representa-se por uma seta rotulada por ‘1’ de ‘S1011’ para ‘S1’;

– se, porém, receber um ‘0’, concluirá que ainda não começou a receber o padrão ‘1011’: tem que regressar ao

início – o que remete para uma seta rotulada por ‘0’ de ‘S1011’ para ‘S0’…

Com isso, fica completo o Diagrama de Estados – a converter numa Tabela de Estados/Saída, vidé ao lado – em

que há que organizar a Tabela de ‘Q(t+1)’ em duas colunas, correspondendo aos casos em que X=0 e X=1.

Sistemas Digitais (Part III)

Page 10 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 11 of 111

Síntese Clássica com Flip-Flops D

De posse da Tabela de Estados/Saída, a sua concretização segundo o método de desenho dito clássico

acompanha pari passu as etapas seguidas aquando do 16aº Projecto; em particular, e porquanto a Tabela apresenta

cinco estados, deduz-se que serão necessários, e suficientes, três flip-flops, designem-se eles de {Q2, Q1, Q0}.

Isso decidido, o passo seguinte é proceder à codificação dos estados – isto é, estabelecer uma correspondência

biunívoca entre cada estado e uma combinação particular de três bits {Q2 Q1 Q0}. Aquela que se elegeu ao lado

usa o CBN (Código Binário Natural)…

A etapa seguinte é transformar a Tabela de Estados/Saída na assim designada Tabela de Transições e Saídas –

ou preferivelmente, já antevendo o que seguirá, num Mapa de Karnaugh, vidé ao lado: cada nome designando um

estado é substituído pelo trio de bits {Q2 Q1 Q0} que o codifica…

Repare-se que a Tabela de Estados se limita a cinco estados, todavia há oito combinações possíveis de três bits:

sobram três combinações, que de certo modo podem ser consideradas como codificando estados inexistentes – pelo

que as respectivas linhas na Tabela de Transições e Saídas são preenchidas com indiferenças, ‘X’…

Obtida essa Tabela de Transições e Saídas, a aplicação do método de Karnaugh habilita a escrever a expressão

simplificada da saída ‘Z’…

Resta determinar as expressões simplificadas das entradas dos flip-flops – e isso exige, é claro, precisar o tipo

de flip-flop a usar. Admita-se que, neste 16bº Projecto, se opta por flip-flops D; como auxiliar de memória,

apresentam-se ao lado o diagrama de estados do flip-flop D e a correspondente Tabela de Excitação.

O passo imediato será obter a Tabela de Excitações do circuito: para tal, começa-se por desdobrar a Tabela de

Transições em três Tabelas, uma por cada um dos estados seguintes de {Q2, Q1, Q0}. Considerando o que se fez a

propósito do 16aº Projecto, prevê-se que a seguir se deveria proceder à substituição dos valores nas colunas

‘Q2(t+1)’, ‘Q1(t+1)’ e ‘Q0(t+1)’ pelos valores a impor nas entradas {D2, D1 e D0} para lograr as transições de estado em

causa; acontece que, tendo-se agora optado pelo flip-flop D, isso é desnecessário: se se pretende que ele transite

para um estado genérico ‘Q’, o que há a fazer é impor, na sua entrada ’D’, o valor D=Q! Ou seja: as Tabelas de

{D2, D1 e D0} são exactamente iguais às de ‘Q2(t+1)’, ‘Q1(t+1)’ e ‘Q0(t+1)’, não é preciso duplicá-las…

A etapa final é – usando em geral o método de Karnaugh – deduzir as expressões simplificadas das entradas

{D2, D1 e D0} dos flip-flops… e proceder ao desenho do correspondente logigrama com a geografia habitual, vidé

ao lado, em que se pressupõe que os flip-flops são edge-triggered comutando no flanco descendente do relógio.

Uma peculiaridade deste circuito é que a saída, ‘Z’, depende apenas dos estados dos flip-flops: não depende

directamente da entrada, ‘X’! A isso não será alheio, certamente, a decisão de, ao desenhar o Diagrama de Estados

do circuito, seguir o assim denominado modelo de Moore: a saída do circuito é inscrita dentro dos círculos que

representam os estados.

Sistemas Digitais (Part III)

Page 12 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 13 of 111

Análise de Circuito com Flip-flops D

Será que o circuito concebido segue mesmo o diagrama de estados desenhado inicialmente? Eis um passo que

de maneira nenhuma se deve omitir!

Essa “conferência” deve ser independente do método usado na síntese do circuito – e na prática suporta-se na

Equação característica dos flip-flops usados, como já se testemunhou algures e agora se volta a aplicar:

O circuito envolve três flip-flops D – cujos estados se designam de {Q2, Q1, Q0}. O primeiro passo na análise

do circuito é, a partir do respectivo logigrama, escrever as expressões algébricas que traduzem o comportamento

da saída do circuito e das entradas dos flip-flops, vidé ao lado.

O segundo passo é substituir as expressões das entradas dos flip-flops na equação característica do flip-flop D.

O resultado são expressões que exprimem o estado seguinte de cada flip-flop – em função dos estados dos flipflops e da entrada externa ‘X’ no instante em que ocorre o flanco descendente do relógio.

O terceiro passo é converter tais expressões nas assim denominadas Tabelas de Transições/Saída – que

indicam, para cada combinação das entradas internas {Q2, Q1, Q0} num instante ‘t’, a saída ‘Z’ do circuito nesse

instante, e, a ocorrer em ‘t’ o flanco descendente do relógio, os estados dos flip-flops no instante ‘t+1’ seguinte.

No total, existirão quatros Tabelas, para {Z, Q2, Q1 e Q0}:

– à esquerda, dispõem-se três colunas, representando outros tantos flip-flops, {Q2, Q1, Q0};

– e no topo dispõe-se uma linha representando a entrada externa ‘X’;

– estando envolvidos três flip-flops, e pois que cada um pode assumir dois valores {Q=0 e Q=1}, o circuito

poderá assumir oito estados distintos, que convirá identificar por códigos binários: {‘000’, ‘001’, ‘010’, etc.}.

O preenchimento das Tabelas não deverá provocar engulhos. As expressões de {Z, Q2, Q1 e Q0} são claras:

– Z=Q2, pelo que a coluna ‘Z’ será igual à coluna ‘Q2’;

– Q0(t+1) será ‘0’ quando X=0 ou Q1(t)=Q0(t)=1;

– Q1(t+1) será ‘1’ apenas quando Q0(t)=1 e X=0, ou Q1(t)=1 e Q0(t)=0 e X=1;

– Q2(t+1) será ‘1’ apenas quando Q1(t)=Q0(t)=X=1.

O passo seguinte será aglutinar as Tabelas dos estados seguintes dos flip-flops, {Q2, Q1, Q0}, numa única, dita

do estado seguinte do circuito, ‘Q2Q1Q0(t+1)’; veja-se o caso da primeira linha, em que, conforme X=0 ou X=1,

assim advém {Q2=0, Q1=0, Q0=0} ou {Q2=0, Q1=0, Q0=1}; aglutinar significa preencher a primeira linha da nova

Tabela com ‘000’ e ‘001’, respectivamente nas colunas ‘X=0’ e ‘X=1’. Para as outras linhas, o método é o mesmo.

A Tabela obtida pode reescrever-se (embora isso não se mostre ao lado) numa outra, dita de Tabela de Estados,

em que cada trio de bits {Q2 Q1 Q0} é entendido como o código binário de um número, e ele é substituído por um

nome como seja ‘S’ indexado pela representação desse número na base 10; essa Tabela descreve “para que Estado”

evoluem os Estados {S0, S1, S2, etc.} do circuito, à medida que se vai alterando a entrada ‘X’.

Resta desenhar o Diagrama de Estados: a cada estado, associa-se um círculo, etiquetado com um nome (ou

código binário); depois, traçam-se setas rotuladas, descrevendo graficamente a Tabela obtida.

Veja-se como exemplo a primeira linha, relativa ao estado ‘000’: a saída é Z=1, e o estado seguinte será ‘000’

ou ‘001’ conforme o valor de ‘X’; isso volve-se em duas setas: uma de ‘S0’ para ‘S0’ rotulada com X=0, ou,

conforme à lei do menor esforço, ‘0’; e uma outra de ‘S0’ para ‘S1’ rotulada com ‘1’. Para denotar que, no estado

‘000’, a saída é Z=0, o correspondente círculo é rotulado por /0.

É hora de se comparar o diagrama de estados obtido a partir do logigrama do circuito com o diagrama de

estados inicialmente concebido – e constatar que aquele está ok: se se confinar a comparação somente a cinco

estados {S0, S1, S2, S3, S4}, e afora os nomes, são idênticas as saídas e a interligação entre eles…

Há, entretanto, que inquirir: quando se faz o power-on ao circuito, qual o estado em que ele ingressa? A

resposta é: não se sabe! No Projecto entre mãos, isso tem importância: se, ao fazer-se o power-on, o circuito

ingressar no estado S5, S6 ou mesmo S7, o circuito assinalará, de imediato, erroneamente (porquanto ainda se não

recebeu a sequência ‘1011’), o valor ‘1’ na sua saída – pelo que convirá recorrer a entradas assíncronas (Clear)

para obrigar a que o estado inicial do circuito seja S0.

Sistemas Digitais (Part III)

Page 14 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 15 of 111

16cº Projecto

Esta sessão começou por um Projecto sem entradas externas, e progrediu para outro com uma entrada externa,

mas ambos com uma só saída; o aumento da complexidade propõe agora duas entradas externas e duas saídas…

Adivinha-se que, com estas poucas “novidades”, a síntese e análise do logigrama obtido seguirão pari passu a

etapas do 16bº Projecto – pelo que não será de estranhar a referência ao lado “Se sobrar tempo na aula…”.

Admita-se que a abertura da porta de uma garagem pode ser detonada por um dispositivo de controlo remoto: o

condutor clica-o, e ele emite um impulso de curta duração. A porta começará a subir, e assim continuará até um

sensor sinalizar “resistência”: a porta encontra-se então completamente aberta. Para a fechar, o condutor clica

novamente no comando… A porta começará a descer, e assim continuará até o sensor sinalizar “resistência”: a

porta encontra-se então completamente fechada. Em qualquer momento, poderá o condutor interromper o

movimento da porta – clicando no comando; quando, depois, voltar a clicar no comando, a porta regressará à

posição de fechada, independentemente do que estava fazendo no momento em que foi interrompida.

O ponto crítico para obter um Circuito sequencial síncrono é o desenho do seu Diagrama de Estados:

Antes de mais, há que codificar as entradas {C, S} e saídas {M, A} do circuito. Vidé o lado uma possibilidade:

– quando activados, tanto o comando ‘C’ como o sensor ‘S’ emitem impulsos curtos – que se poderão

compreender como um ‘1’ com a duração do período dos clocks, seguido de ‘0’s…

– a porta movendo-se é codificada com M=1, e abrindo-se é codificada com A=1.

1. Considere-se o momento anterior a ter o condutor clicado no seu dispositivo de controlo… A porta estará

fechada: o circuito encontrar-se-á num estado inicial em que o motor deverá estar parado. Esse estado representase por um círculo com um nome significativo, como seja ‘F’ - em cujo seio se indica, precedidas pelo símbolo ‘/’,

as saídas a assinalar, M=0 (que torna ‘A’ irrelevante), a ser mantidas até ao próximo "clock; o caracter inicial do

estado é denotado por uma seta dirigida da esquerda para o círculo ‘F’.

2. Admita-se, então, que o condutor clica no seu comando… Isto é, ocorre C=1 (e S=0, no sentido de que,

estando a porta então parada, o sensor não poderá então sinalizar “resistência”); o motor irá fazer subir a porta.

Essa situação representa-se por um círculo nomeado ‘A:2’ (significando algo como porta meio-aberta), em

cujo seio se indicam as saídas M=1 e A=1 (ou, conforme à lei do menor esforço, ‘11’), e uma seta do círculo ‘F’

para o círculo ‘A:2’, rotulada com C=1 e S=0 (ou, conforme à lei do menor esforço, ‘10’);

3. Algo mais tarde, o sensor sinalizará “resistência”… Isto é, irá ocorrer C=0 e S=1; o motor irá parar a porta.

Essa situação representa-se por um círculo nomeado ‘A’ (significando porta aberta), em cujo seio se indicam as

saídas ‘0X’ (isto é: M=0 e ‘A’ irrelevante), e uma seta do círculo ‘A:2’ para o círculo ‘A’, rotulada com ‘01’ (isto

é: C=0 e S=1);

4. Mais tarde, o condutor irá clicar no comando… Isto é, irá ocorrer C=1 e S=0; o motor irá fechar a porta.

Essa situação representa-se por um círculo nomeado ‘F:2’ (significando porta meio-fechada), em cujo seio se

indicam as saídas ‘10’, e uma seta do círculo ‘A’ para o círculo ‘F:2’, rotulada com ‘10’;

5. Algo mais tarde, o sensor sinalizará “resistência”… Isto é, ocorrerá C=0 e S=1; o circuito irá retornar ao

estado inicial.

Essa situação representa-se por uma seta do círculo ‘F:2’ para o círculo ‘F’, rotulada com ‘01’;

6. Enquanto a porta está abrindo ou fechando, o condutor poderá clicar no comando: poderá ocorrer C=1 e S=0

nos estados ‘A:2’ ou ‘F:2’; o motor deverá parar.

Essa situação pode representar-se por um círculo nomeado ‘P’ (significando porta parada), em cujo seio se

indicam as saídas ‘0X’, e setas dos círculos ‘A:2’ ou ‘F:2’ para o círculo ‘P’, rotuladas com ‘10’ (A menção “pode

representar-se” significa que é possível fazer de outra maneira mais simples, que adiante se aborda)

7. Quando o condutor voltar a clicar no comando, isto é, ocorrer C=1 e S=0, o motor irá fechar a porta.

Essa situação representa-se por uma seta do círculo ‘P’ para o círculo ‘F:2’, rotulada com ‘10’

As transições acima enumeradas encontram-se explicitadas no Diagrama de Estados ao lado – mas muitas mais

combinações das entradas se poderiam congeminar – que todavia lá não estão: o Diagrama está incompletamente

especificado! Pois que as entradas são duas, a sua especificação cabal poderia volver-se em quatro setas “saindo”

de cada estado (isto é: originando um total de 20 setas) – o que tornaria o Diagrama algo como uma ilegível sopa

de esparguete… O mais recomendado será suspender o desenho do Diagrama, e passar directamente à construção

da Tabela de Estados e Saídas: é o que se fará de imediato…

Sistemas Digitais (Part III)

Page 16 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 17 of 111

Síntese Clássica com Flip-Flops D

Considere-se então a porção do Diagrama de Estados já traçada; a partir dela, poder-se-á dar início ao

preenchimento da Tabela de Estados e Saídas, vidé ao lado – onde estão definidas as células correspondentes às

setas naquele traçadas: falta preencher treze células. O resto do preenchimento não deverá provocar engulhos…

1. Quando C=0 e S=0 (isto é, nem o comando nem o sensor sinalizam actividade), o que corresponde à coluna

da Tabela mais à esquerda, intui-se que o estado do circuito não se deve alterar: nomeadamente, se a porta estava

abrindo), continua abrindo e se estava fechada, assim continua… Essa coluna será então uma cópia da coluna ‘Qt’;

2. A ocorrência de S=1 nos estados ‘F’, ‘A’ e ‘P’ (isto é: com a porta imóvel, o sensor sinaliza “resistência”),

deve ser considerada impossível – pelo que devem preencher-se as correspondentes (6) células com ‘X’;

3. Resta preencher duas células – correspondentes aos casos em que C=1 e S=1 quando a porta se encontra

movendo. Ora, S=1 significa “resistência” – pelo que a porta se deve imobilizar; e¸ quando a porta se encontra

movendo, C=1 significa o mesmo: o condutor pretende interromper o movimento da porta… Ou seja: naquelas

duas células, o circuito deve ingressar num estado em que a porta esteja imóvel – mas quanto a isso há três

possibilidades, a saber: ‘F’, ‘A’ e ‘P’. Qual delas deve ser a eleita?

Para o caso em que a porta se está abrindo (em ‘A:2’), será pacífico que a interrupção do seu movimento

conduza o circuito ao estado ‘P’ (mas a escolha do estado ‘A’ seria igualmente válida).

Já para o caso em que a porta se está fechando (em ‘F:2’), a escolha não será tão pacífica… pelo se deverá

considerar o enunciado incompletamente especificado – e acrescentar-lhe: deve ser ignorado o clicar no comando

(para interromper o movimento da porta) se ocorrer exactamente quando ela está a acabar de se fechar.

(Abra-se um parêntesis: esta é uma prática comum; eventualmente, em provas de avaliação, o próprio estudante

será confrontado com ela: poderão elas conter algum enunciado incompletamente especificado, no sentido de ser

omisso relativamente a alguns detalhes - cabendo-lhe então completá-lo, com algumas assunções razoáveis…)

Construída a Tabela de Estados e de Saídas, e optando por recorrer a flip-flops D, os subsequentes passos no

sentido de lograr o correspondente circuito seguirão pari passu o que se fez a propósito do 16bº Projecto…

Porém, e antes de o fazer, convirá olhar cuidadosamente para a Tabela a que se chegou. E desde logo sobressai

a quase igualdade entre as linhas respeitantes aos estados ‘A’ e ‘P’: ambos geram as saídas {M=0 e A=X}, e as

células com os estados seguintes contêm exactamente o mesmo para todas as combinações de {C, S} excepto para

{C=0 e S=0} – e mesmo neste caso o comportamento do circuito em ambos os estados vem a ser o mesmo: o

estado não se altera. Pelo que é lícita deduzir que os estados ‘A’ e ‘P’ são equivalentes: em termos práticos, podem

ser colapsados em um único estado, como seja o próprio ‘A’. Aliás, isso mesmo já poderia ter sido decidido

aquando do traçado do Diagrama de Estados: se o condutor clica no comando quando a porta se está abrindo ou

fechando, o motor deverá parar – mas, em vez de se congeminar um novo estado, ‘P’, poder-se-ia ao invés ter

aproveitado um estado já definido, ‘A’ – que ademais tem a propriedade de, quando se clicar no comando, dele se

transitar para o estado em que a porta se estará fechando, como requerido no enunciado…

Adiante, observar-se-ão outros Projectos em que o desenho do Diagrama de Estados conduz a mais estados do

que os estritamente necessários – no sentido de que envolve estados equivalentes, que por isso mesmo deverão ser

colapsados…

Formalmente, poder-se-ão colapsar dois estados (por isso dito de equivalentes) em um único se, para qualquer

sequência de entradas, as saídas forem rigorosamente as mesmas. Esse colapso pode ser vantajoso, e o Projecto

entre mãos manifesta-o: o Diagrama de Estados envolve 5 estados, o que conduz a um mínimo de 3 flip-flops –

mas a Tabela final a que se chega (após a substituição do nome ‘P’ por ‘A’, e a remoção da linha ‘P’) já só exibe 4

estados, o que se basta em 2 flip-flops! Menos um flip-flop, portanto…

As etapas subsequentes vêm a ser, vidé ao lado:

– a codificação dos 4 estados da Tabela de Estados; ao lado, optou-se pelo CBN (Código Binário Natural);

– o preenchimento da Tabela de Transições do circuito, pela substituição dos nomes dos estados pelos seus

códigos; prevendo o subsequente uso do método de Karnaugh, convirá organizá-la de modo a que a ordem das

combinações das entradas (internas e externas) siga o código binário reflectido;

– a obtenção da Tabela de Excitações do circuito: para tal, começa-se por desdobrar a Tabela de Transições em

duas Tabelas, uma por cada um dos estados seguintes de {Q1, Q0}…

– a dedução das expressões das entradas {D1 e D0} dos flip-flops…

Sistemas Digitais (Part III)

Page 18 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 19 of 111

Análise de Circuito com Flip-flops D

Será que o circuito concebido segue mesmo o diagrama de estados desenhado inicialmente?

A resposta deve ser por um método independente daquele usado na síntese do circuito – e na prática suporta-se

na Equação característica dos flip-flops usados, como já se testemunhou algures e agora se volta a aplicar:

O circuito envolve dois flip-flops D – cujos estados se designam de {Q1, Q0}. O primeiro passo na análise do

circuito é, a partir do respectivo logigrama, escrever as expressões algébricas que traduzem o comportamento das

saídas do circuito e das entradas dos flip-flops, vidé ao lado.

O segundo passo é substituir as expressões das entradas dos flip-flops na equação característica do flip-flop D.

O resultado são expressões que exprimem o estado seguinte de cada flip-flop – em função dos estados dos flipflops e das entradas externas {C, S} no instante em que ocorre o flanco descendente do relógio.

O terceiro passo é converter tais expressões nas assim designadas Tabelas de Transições/Saída – que indicam,

para cada combinação das entradas internas {Q1, Q0} num instante ‘t’, as saídas {M, A} do circuito nesse

instante, e, a ocorrer em ‘t’ o flanco descendente do relógio, os estados dos flip-flops no instante ‘t+1’ seguinte.

No total, existirão três Tabelas, para {Z, Q1 e Q0}:

– à esquerda, dispõem–se duas colunas, representando outros tantos flip-flops, {Q1, Q0};

– e no topo dispõem-se duas linhas representando as entradas externas {C, S};

– estando envolvidos dois flip-flops, e pois que cada um pode assumir dois valores {Q=0 e Q=1}, o circuito

poderá assumir quatro estados distintos, que convirá identificar por códigos binários: {‘00’, ‘01’, ‘10’, etc.}.

O preenchimento das Tabelas não deverá provocar engulhos. As expressões de {Z, Q1 e Q0} são claras:

– M=Q0, pelo que a coluna ‘M’ será igual à coluna ‘Q0’;

– A é o complemento de ‘Q1’, pelo que a coluna ‘A’ será o complemento da coluna ‘Q1’;

– quanto a ‘Q1(t+1)’ e ‘Q0(t+1)’, deixa-se ao leitor conferir o seu preenchimento…

O passo seguinte será aglutinar as Tabelas dos estados seguintes dos flip-flops, {Q1(t+1), Q0(t+1)}, numa única,

dita do estado seguinte do circuito, ‘Q1Q0(t+1)’.

A Tabela obtida pode reescrever-se (embora isso não se mostre ao lado) numa outra, dita de Tabela de Estados,

em que cada par de bits {Q1 Q0} é entendido como o código binário de um número, e ele é substituído por um

nome como seja ‘S’ indexado pela representação desse número na base 10; essa Tabela descreve “para que Estado”

evoluem os Estados {S0, S1, S2, S3} do circuito, à medida que se vão alterando as entradas {C, S}.

Resta desenhar o Diagrama de Estados: a cada estado, associa-se um círculo, etiquetado com um nome (ou

código binário); depois, traçam-se setas rotuladas, descrevendo graficamente a Tabela obtida.

Veja-se como exemplo a primeira linha, relativa ao estado ‘00’: as saídas são {M=0, A=1}, e o estado seguinte

será ‘00’, ‘10’, ‘01’ ou ‘11’ conforme os valores de {C, S}; isso volve-se em quatro setas, respectivamente de ‘S0’

para ‘S0’ (rotulada com ‘00’), de ‘S0’ para ‘S2’ (rotulada com ‘01’), de ‘S0’ para ‘S1’ (rotulada com ‘10’) e de ‘S0’

para ‘S3’ (rotulada com ‘11’). Para denotar que, no estado ‘00’, as saídas são {M=0, A=1}, o correspondente

círculo é rotulado por /01.

Atente-se que no Diagrama há setas com vários rótulos; em particular, a seta de ‘S1’ para ‘S2’ comporta três

rótulos, a saber ‘01’, ‘10’ e ‘11’: isso é preferível a traçar três setas de ‘S1’ para ‘S2’, cada uma com um desses três

rótulos…

É hora de se comparar o diagrama de estados obtido a partir do logigrama do circuito com a Tabela de estados

inicialmente concebida – e constatar que aquele está ok: afora os nomes, são “idênticas” as saídas e a interligação

entre os estados… as aspas em “idênticas” querendo significar que as indiferenças na Tabela se volveram agora em

valores concretos (o que é irrelevante, pois as indiferenças significam situações a não ter em conta).

Há, entretanto, que inquirir: quando se faz o power-on ao circuito, qual o estado em que ele ingressa? A

resposta é: não se sabe! No Projecto entre mãos, isso tem importância: a porta deve inicialmente considerar-se

fechada, isto é, o estado inicial deve ser ‘S0’ – pelo que convirá recorrer a entradas assíncronas (Clear) para

obrigar a que o estado inicial do circuito seja mesmo S0.

Sistemas Digitais (Part III)

Page 20 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Moore)/

Page 21 of 111

Forma Canónica de Moore

Após três exemplos de síntese de circuitos sequenciais síncronos, é hora de abstrair das particularidades…

Um relance aos logigramas obtidos descortina uma arquitectura comum, esquematizada ao lado:

à esquerda, encontram-se as entradas, a saber:

– se existentes, as entradas primárias ou externas, como seja ‘X’ ou {C, S} (ou outras);

– as entradas secundárias ou internas, que são as saídas dos flip-flops usados: T ou D (ou mesmo SR e JK);

– as entradas assíncronas (Preset e Clear), destinadas a inicializar o circuito a um estado específico;

– uma entrada Clock, por onde se recebem os impulsos de relógio – e que alimenta directamente todos os

flip-flops: trata-se de um circuito sequencial síncrono.

Conforme à convenção seguida neste itinerário, as entradas externas localizam-se por cima das entradas

internas: estas são consideradas as entradas de maior peso.

à direita, encontra-se a lógica das saídas, isto é: uma malha combinatória, alimentada pelas entradas

internas, que gera as saídas do circuito.

A dedução das suas expressões algébricas passa por preencher as Tabelas de Verdade (ou, preferivelmente,

Mapas de Karnaugh) das saídas em função das entradas internas – que são as saídas dos flip-flops.

A tal lógica das saídas está associado um certo tempo de propagação, seja ‘TZ’, que é o intervalo de tempo que

medeia entre a mudança nos estados dos flip-flops e as mudanças nas saídas.

entre ambos, encontra-se a lógica do estado seguinte, isto é: uma malha combinatória, alimentada pelas

entradas (externas e internas), que gera os novos valores a aplicar às entradas dos flip-flops, para que eles evoluam

como deve ser.

A dedução das respectivas expressões algébricas passa por preencher as Tabelas de Verdade (ou Mapas de

Karnaugh) das entradas dos flip-flops em função das entradas (externas e internas).

A tal lógica do estado seguinte está associado um certo tempo de propagação, seja ‘TNovasEntradas’, que é o

intervalo de tempo que decorre entre a mudança nos estados dos flip-flops (ou nas entradas externas) e a mudança

nas entradas dos flip-flops.

Os flip-flops são temporalmente caracterizados por um certo tempo de preparação, tsu, e um certo tempo de

propagação, tpHL e tpLH.

Notável nesta arquitectura é que, em cada momento, as saídas dependem directamente só dos estados dos flipflops, que não das entradas externas nesse momento. Ela reflecte o facto de o seu desenho ter seguido o que se

denomina de Modelo de Moore: em termos do Diagrama de estados, ele é caracterizado pelo fato de as saídas

ficarem inscritas dentro dos círculos que representam os estados – por conseguinte independentemente das

entradas externas do circuito, vidé ao lado.

Isso tem uma consequência óbvia: como as saídas dos flip-flops podem mudar somente no próximo flanco de

comutação do relógio, também as saídas dos circuito somente poderão mudar então: elas permanecem inalteradas

durante todo um período de relógio.

Como testemunho disso, veja-se o diagrama temporal da evolução do 16cº Projecto:

– inicialmente, a porta encontra-se fechada: o circuito encontra-se no estado ‘F’, gerando a saída M=0;

– quando o condutor clica no comando, este sinaliza-o forçando C=1 – sem qualquer consequência imediata;

– a consequência só se manifesta no próximo clock: pois que se verifica C=1, o estado do circuito, e após um

certo tempo de propagação {tpHL ou tpLH}, passa a ser ‘A:2’ – gerando, após um tempo de propagação tZ, as saídas

{M=1, A=1};

– quando o sensor assinala “resistência”, ele sinaliza-o forçando S=1 – sem qualquer consequência imediata;

– a consequência manifesta-se no próximo clock: pois que se verifica S=1, o estado do circuito, e após um certo

tempo de propagação {tpHL ou tpLH}, passa a ser ‘A’ – gerando, após um tempo de propagação tZ, a saída M=0.

Moral do Modelo de Morre: ainda que uma entrada mude, as saídas só mudarão após se alterar o estado de

algum flip-flop (e isso somente sucederá no próximo clock); e, depois de mudarem, manter-se-ão assim até ao clock

seguinte.

Sistemas Digitais (Part III)

Page 22 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 23 of 111

17aº Projecto

Abordada já a síntese de circuitos sequenciais síncronos seguindo o denominado modelo de Moore, é hora de

abordar um outro modelo, dito de Mealy – caracterizado por as saídas do circuito, em cada momento, dependerem

dos estados dos flip-flops, e também das entradas externas nesse momento. Tal como as demais sessões, irá

desenrolar-se a partir de um Projecto concreto, que, não por acaso, tem o mesmo enunciado que o 16bº Projecto…

O ponto crítico para obter um Circuito sequencial síncrono é o desenho do seu Diagrama de Estados:

1. Considere-se o momento em que se faz o power-on… O circuito nada “sabe” então do que se passou antes –

pelo que será pacífico forçá-lo a assumir um estado inicial – que se representa por um círculo identificado por um

nome significativo, ‘S0’; o seu caracter inicial é denotado por uma seta dirigida da esquerda para o círculo ‘S0’.

2. Recorde-se, entretanto, que tal circuito está recebendo, do receptor de RF, uma sucessão de ‘0’ e ‘1’s…

– seja ‘0’ ou ‘1’ o primeiro bit a ser recebido, não se pode concluir que se detectou o padrão ‘1011’ – pelo que

a saída será, em qualquer caso, Z=0. Relativamente ao estado que o circuito deverá adquirir após o próximo clock:

se esse primeiro bit for ‘1’, o circuito pode “julgar” que ele é já o primeiro bit do padrão ‘1011’, pelo que irá

transitar para um novo estado – o que se representa por um círculo nomeado ‘S1’ e uma seta do círculo ‘S0’ para o

círculo ‘S1’; mas se for ‘0’, o circuito irá permanecer em ‘S0’ – o que se representa por uma seta de ‘S0’ para ‘S0’.

Em consequência, de ‘S0’ “saem” duas setas. Para distinguir o que motiva aquela dirigida para ‘S1’ e qual a

correspondente saída, ela é rotulada por X=1/Z=0, ou, conforme à lei do menor esforço, ‘1/0’; intui-se que a seta

dirigida para ‘S0’ é rotulada por ‘0/0’.

3. “Resolvido” o estado ‘S0’, considere-se, então, que o circuito se encontra no estado ‘S1’. Qual será a sua

saída, e como evolui ele, quando receber, do receptor de RF, um ‘0’ ou um ‘1’?

– pois que não chega para decidir que se detectou o padrão ‘1011’, a saída será, em qualquer dos casos, Z=0;

– se receber um ‘0’, o circuito pode “julgar” que é o segundo bit do padrão ‘1011’, pelo que transitará para um

novo estado – o que se representa por um círculo nomeado ‘S10’ e uma seta de ‘S1’ para ‘S10’, rotulada por ‘0/0’;

– se, porém, receber um ‘1’, irá concluir que estava errada a suposição de que o ‘1’ precedente era o primeiro

bit do padrão ‘1011’ – mas talvez o ‘1’ que acaba de receber o seja; isso remete para uma seta de ‘S1’ para ‘S1’,

rotulada por ‘1/0’;

4. Considere-se, agora, que o circuito se encontra no estado ‘S10’. Que sucederá quando receber outro bit?

– pois que não chega para decidir que se detectou o padrão ‘1011’, a saída será, em qualquer dos casos, Z=0;

– se receber um ‘1’, o circuito pode “julgar” que ele é o terceiro bit do padrão ‘1011’ – pelo que irá transitar

para um novo estado – o que se representa por um círculo ‘S101’, e uma seta rotulada por ‘1/0’ de ‘S10’ para ‘S101’;

– se, porém, receber um ‘0’, concluirá que afinal os bits ‘10’ precedentes não eram o começo do padrão ‘1011’:

tem que regressar ao início – o que remete para uma seta rotulada por ‘0/0’ de ‘S10’ para ‘S0’.

5. Considere-se, agora, que o circuito se encontra no estado ‘S101’. Que sucederá quando receber outro bit?

– se receber um ‘1’, o circuito conclui que ele é o quarto bit do padrão ‘1011’ – pelo que a saída volver-se-á ‘1’.

E, no próximo clock, irá regressar ao início – o que remete para uma seta rotulada por ‘1/1’ de ‘S101’ para ‘S0’…

– se, porém, receber um ‘0’, concluirá que afinal os bits ‘101’ precedentes não eram o começo do padrão ‘1011’

– mas talvez os últimos ‘10’ o sejam, o que remete para uma seta rotulada por ‘0/0’ de ‘S101’ para ‘S10’.

Com isso, fica completo o Diagrama de Estados – a converter numa Tabela de Estados/Saída, vidé ao lado – em

que ambas as Tabelas, de ‘Q(t+1)’ e ‘Z(t)’, se organizam em duas colunas, correspondentes a X=0 e X=1.

Abra-se um parêntesis: o enunciado afirma “Não se consideram sequências sobrepostas”. Quer dizer: só depois

de findo um padrão ‘1011’ é que pode começar um outro ‘1011’. Se o enunciado admitisse sequências sobrepostas,

então, ‘1011011’ deveria ser entendido como sobreposição de dois padrões: um começando no primeiro bit,

‘1011011’ e outro começando no quarto bit: ‘1011011’ – com o que a saída deveria ser ‘1’ no 4º e no 7º bits! No

diagrama de estados, isso levaria a uma modificação: recebido o quarto bit do padrão, o circuito não retornaria ao

estado inicial ‘S0’, ingressaria, sim, no estado em que “julga” que se recebeu já o primeiro bit, ‘S1’, vidé ao lado.

O leitor poderá agora comparar os diagramas de estado logrados para o mesmíssimo enunciado:

– no modelo de Moore, seguido no 16bº Projecto, ele expande-se por cinco círculos: ‘S0’, ‘S1’, ‘S10’, ‘S101’ e

‘S1011’; a saída que eles forçam é explicitada no seio desses círculos;

– no modelo de Mealy, seguido no 17aº Projecto, ele expande-se por só quatro círculos: ‘S0’, ‘S1’, ‘S10’ e ‘S101’;

as saídas são associadas a setas, isto é, aos pares “estado de onde a seta provêm” e “entrada externa que a motiva”.

Sistemas Digitais (Part III)

Page 24 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 25 of 111

Síntese Clássica com Flip-Flops JK

De posse da Tabela de Estados/Saída, a sua concretização segundo o método de desenho dito clássico

acompanha pari passu as etapas seguidas na precedente sessão; em particular, e porquanto a Tabela apresenta

quatro estados, deduz-se que serão necessários, e suficientes, dois flip-flops, designem-se eles de {Q1, Q0}.

Isso decidido, o passo seguinte é proceder à codificação dos estados – isto é, estabelecer uma correspondência

biunívoca entre cada estado e uma combinação particular de dois bits {Q1 Q0}. Aquela que se elegeu ao lado usa o

CBR (Código Binário Reflectido)…

A etapa seguinte é transformar a Tabela de Estados/Saída na assim designada Tabela de Transições e Saídas –

ou preferivelmente, já antevendo o que seguirá, num Mapa de Karnaugh, vidé ao lado: cada nome designando um

estado é substituído pelo par de bits {Q1 Q0} que o codifica…

Obtida essa Tabela de Transições e Saídas, a aplicação do método de Karnaugh habilita a escrever a expressão

simplificada da saída ‘Z’…

Resta determinar as expressões simplificadas das entradas dos flip-flops – e isso exige, é claro, precisar o tipo

de flip-flop a usar. Admita-se que, neste 17aº Projecto, se opta por flip-flops JK; como auxiliar de memória,

apresentam-se ao lado o diagrama de estados do flip-flop JK e a correspondente Tabela de Excitação.

O passo imediato será obter a Tabela de Excitações do circuito: para tal, começa-se por desdobrar a Tabela de

Transições em duas Tabelas, uma por cada um dos estados seguintes de {Q1, Q0}. A seguir, dever-se-á proceder à

substituição dos valores nas colunas ‘Q1(t+1)’ e ‘Q0(t+1)’ pelos valores a impor nas entradas {J1, K1} e {J0, K0} para

lograr as transições de estado em causa …

Considere-se, por exemplo, a linha em que Q1=0 e Q0=0, e atente-se no que sucede quando X=0. O estado

seguinte de ‘Q1’ é ‘0’ e o estado seguinte de ‘Q0’ é ‘0’– e isso remete para a pergunta: para que aconteçam essas

“transições” em {Q1, Q0}, como se devem excitar as entradas dos flip-flops? A resposta da Tabela de Excitação do

flip-flop JK é: a transição ‘0’→‘0’ logra-se aplicando ‘0’ na entrada ‘J’ (sendo indiferente o que se aplica em ‘K’).

São precisamente os valores ‘0X’ o que se escreve nas Tabelas de {J1, K1} e {J0, K0} para o caso em que X=0.

A etapa final é deduzir as expressões simplificadas das entradas {J1, K1, J0, K0} dos flip-flops… Para tal,

convirá desdobrar cada uma das Tabelas de {J1, K1} e {J0, K0} em duas Tabelas, uma por cada uma das entradas

{J1, K1, J0, K0}.

Considere-se, por exemplo, a linha em que Q1=0 e Q0=0, e atente-se ao que sucede quando X=0: observa-se

{J1K1=0X}, isto é, {J1=0, K1=X}; então, na correspondente posição {Q1=0 e Q0=0 e X=0} a Tabela de ‘J1’ irá

conter ‘0’ e a de ‘K1’ irá conter ‘X’. Procedendo analogamente para as restantes combinações de {Q1 e Q0 e X},

ficarão preenchidas as Tabelas de {J1, K1, J0, K0} – a que depois será hora de aplicar o método de Karnaugh…

(Abra-se um parêntesis: com algum treino, o leitor ficará capaz de passar directamente da Tabela de Transições

do circuito para as Tabelas de {J1, K1, J0, K0})

Enfim, procede-se ao desenho do correspondente logigrama com a geografia habitual, vidé ao lado, em que se

pressupõe que os flip-flops são edge-triggered comutando no flanco descendente do relógio.

Uma peculiaridade deste circuito é que a saída, ‘Z’, depende dos estados dos flip-flops e da entrada, ‘X’! A isso

não será alheio, certamente, a decisão de, ao desenhar o Diagrama de Estados do circuito, seguir o assim

denominado modelo de Mealy: a saída do circuito é inscrita nas setas que representam as transições entre estados

(Em rigor, porém, pode suceder que o projectista tenha seguido o modelo de Mealy – mas pode dar-se o caso de,

para todos os estados, as setas que “saem” de cada um deles patentearem a mesma saída; a ser assim, o método de

Karnaugh conduzirá a uma expressão para a saída que não depende das entradas externas!).

Sistemas Digitais (Part III)

Page 26 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 27 of 111

Análise de Circuito com Flip-flops JK

Quando um projectista se engaja no desenho de um circuito, e antes de o materializar de facto, e para evitar

posteriores dissabores, há que “fazer a prova dos nove”: será que o circuito concebido segue mesmo o diagrama de

estados desenhado inicialmente? E este passo de maneira nenhuma se deve omitir!

Essa “conferência” deve ser independente do método usado na síntese do circuito – e na prática suporta-se na

Equação característica dos flip-flops usados, como já se testemunhou algures e agora se volta a aplicar:

O circuito envolve dois flip-flops JK – cujos estados se designam de {Q1, Q0}. O primeiro passo na análise do

circuito é, a partir do respectivo logigrama, escrever as expressões algébricas que traduzem o comportamento da

saída do circuito e das entradas dos flip-flops, vidé ao lado.

Tendo em mira o desenho do Diagrama de Estados, o segundo passo é substituir as expressões das entradas dos

flip-flops na equação característica do flip-flop JK. O resultado são expressões que exprimem o estado seguinte de

cada flip-flop – em função dos estados dos flip-flops e da entrada ‘X’ no instante em que ocorre o flanco

descendente do relógio.

O terceiro passo é converter tais expressões nas assim denominadas Tabelas de Estado/Saída – que indicam,

para cada combinação das entradas internas e externas {Q1, Q0, X} num instante ‘t’, a saída ‘Z’ do circuito nesse

instante, e, a ocorrer em ‘t’ o flanco descendente do relógio, os estados dos flip-flops no instante ‘t+1’ seguinte.

No total, existirão três Tabelas, para {Z, Q1 e Q0}:

– à esquerda, dispõem-se duas colunas, representando outros tantos flip-flops, {Q1, Q0};

– e no topo dispõe-se uma linha representando a entrada externa ‘X’;

– estando envolvidos dois flip-flops, e pois que cada um pode assumir dois valores {Q=0 e Q=1}, o circuito

poderá assumir quatro estados distintos, que convirá nomear por códigos binários: {‘S00’, ‘S01’, ‘S10’ e ‘S11’}.

O preenchimento das Tabelas não deverá provocar engulhos. As expressões de {Z, Q1 e Q0} são claras:

– ‘Z’ será ‘0’ apenas para a combinação Q1=1 e Q0=0 e X=1;

– quanto a ‘Q1(t+1)’ e ‘Q0(t+1)’, deixa-se ao leitor conferir o seu preenchimento…

O passo seguinte será aglutinar as Tabelas dos estados seguintes dos flip-flops, {Q1(t+1), Q0(t+1)}, numa única,

dita do estado seguinte do circuito, ‘Q1Q0(t+1)’.

A Tabela obtida pode reescrever-se (embora isso não se mostre ao lado) numa outra, dita de Tabela de Estados,

em que cada par de bits {Q1 Q0} é entendido como o código binário de um número, e ele é substituído por um

nome como seja ‘S’ indexado pela representação desse número na base 10; essa Tabela descreve “para que Estado”

evoluem os Estados {S0, S1, S2, S3} do circuito, à medida que se vai alterando a entrada {X}.

Resta desenhar o Diagrama de Estados: a cada estado, associa-se um círculo, etiquetado com um código

binário (ou pelo correspondente nome); depois, traçam-se setas rotuladas, descrevendo graficamente a Tabela.

Veja-se como exemplo a primeira linha, relativa ao estado ‘00’: conforme ‘X’ seja ‘0’ ou ‘1’, assim a saída será

Z=0 ou Z=1, e o estado seguinte será ‘00’ ou ‘01’, respectivamente; isso volve-se numa seta dirigida do círculo

‘00’ para o círculo ‘00’, rotulada com ‘X=0/Z=0’ (ou, conforme à lei do menor esforço, ‘0/0’) e numa outra

dirigida do círculo ‘00’ para o círculo ‘01’, rotulada com ‘1/0’.

É hora de o projectista comparar o diagrama de estados obtido a partir do logigrama do circuito com o diagrama

de estados que ele inicialmente concebeu – e ficar tranquilo, que o circuito a que chegou está ok: afora os nomes, o

número de estados, a interligação entre eles e as saídas são idênticos…

Há, entretanto, que inquirir: quando se faz o power-on ao circuito, qual o estado em que ele ingressa? A

resposta é: não se sabe! No Projecto entre mãos, isso tem importância: se, ao fazer-se o power-on, o circuito

ingressar no estado S10 e ocorrer X=1, o circuito assinalará, de imediato, erroneamente (porquanto ainda se não

recebeu a sequência ‘1011’), o valor ‘1’ – pelo que convirá recorrer a entradas assíncronas (Clear) para obrigar a

que o estado inicial do circuito seja S00.

Sistemas Digitais (Part III)

Page 28 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 29 of 111

17bº Projecto

O 17aº Projecto é um detector de um padrão específico de ‘0’s e ‘1’s – e nem que seja por serem os detectores

de padrões os tipos de circuitos a que muitos estudantes serão mais avessos, será de bom-tom levar por diante a

síntese de mais um circuito detector de padrões, desta feita com flip-flops SR…

Pretende-se um circuito sequencial síncrono que sinaliza ‘1’ se e só se os últimos três bits foram ‘101’.

O ponto crítico para obter um Circuito sequencial síncrono é o desenho do seu Diagrama de Estados:

1. Considere-se o momento em que se faz o power-on… O circuito nada “sabe” então do que se passou antes –

pelo que será pacífico forçá-lo a assumir um estado inicial – que se representa por um círculo identificado por um

nome significativo, ‘S0’; o seu caracter inicial é denotado por uma seta dirigida da esquerda para o círculo ‘S0’.

2. Recorde-se, entretanto, que tal circuito está recebendo uma sucessão de ‘0’ e ‘1’s…

– seja ‘0’ ou ‘1’ o primeiro bit a ser recebido, não se pode concluir que se detectou o padrão ‘101’ – pelo que a

saída será, em qualquer caso, Z=0. Relativamente ao estado que o circuito deverá adquirir após o próximo clock:

se esse primeiro bit for ‘1’, o circuito pode “julgar” que ele é já o primeiro bit do padrão ‘101’, pelo que irá

transitar para um novo estado – o que se representa por um círculo nomeado ‘S1’ e uma seta do círculo ‘S0’ para o

círculo ‘S1’, rotulada por ‘1/0’; mas se for ‘0’, o circuito irá permanecer em ‘S0’ – o que se representa por uma seta

de ‘S0’ para ‘S0’, rotulada por ‘0/0’.

3. Considere-se, agora, que o circuito se encontra no estado ‘S1’. Que sucederá quando receber outro bit?

– pois que não chega para decidir que se detectou o padrão ‘101’, a saída será, em qualquer dos casos, Z=0;

– se receber um ‘0’, o circuito pode “julgar” que é o segundo bit do padrão ‘101’, pelo que transitará para um

novo estado – o que se representa por um círculo ‘S10’ e uma seta de ‘S1’ para ‘S10’, rotulada por ‘0/0’;

– se, porém, receber um ‘1’, irá concluir que estava errada a suposição de que o ‘1’ precedente era o primeiro

bit do padrão ‘101’ – mas talvez o ‘1’ que acaba de receber o seja; isso remete para uma seta de ‘S1’ para ‘S1’,

rotulada por ‘1/0’;

4. Considere-se, agora, que o circuito se encontra no estado ‘S10’. Que sucederá quando receber outro bit?

– se receber um ‘1’, o circuito conclui que ele é o terceiro bit do padrão ‘101’ – pelo que a saída volver-se-á ‘1’.

E, no próximo clock, irá regressar a ‘S1’ – o que remete para uma seta rotulada por ‘1/1’ de ‘S10’ para ‘S1’…

– se, porém, receber um ‘0’, concluirá que afinal os bits ‘10’ precedentes não eram o começo do padrão ‘101’ –

pelo que deverá retornar ao estado inicial, o que remete para uma seta rotulada por ‘0/0’ de ‘S10’ para ‘S0’.

Com isso, fica completo o Diagrama de Estados – a converter numa Tabela de Estados/Saída, vidé ao lado – em

que ambas as Tabelas, de ‘Q(t+1)’ e ‘Z(t)’, se organizam em duas colunas, correspondentes a X=0 e X=1.

De posse da Tabela de Estados/Saída, e porquanto a Tabela apresenta três estados, deduz-se que serão

necessários, e suficientes, dois flip-flops, designem-se eles de {Q1, Q0}. O passo seguinte é proceder à codificação

dos estados. Aquela que se elegeu ao lado usa o CBN (Código Binário Natural)…

A etapa seguinte é transformar a Tabela de Estados/Saída na assim designada Tabela de Transições e Saídas –

ou preferivelmente, já antevendo o que seguirá, num Mapa de Karnaugh, vidé ao lado: cada nome designando um

estado é substituído pelo par de bits {Q1 Q0} que o codifica…

Obtida essa Tabela de Transições e Saídas, a aplicação do método de Karnaugh habilita a escrever a expressão

simplificada da saída ‘Z’…

Optando por flip-flops SR, o passo imediato será obter a Tabela de Excitações do circuito: para tal, começa-se

por desdobrar a Tabela de Transições em duas Tabelas, uma por cada um dos estados seguintes de {Q1, Q0}. A

seguir, dever-se-á proceder à substituição dos valores nas colunas ‘Q1(t+1)’ e ‘Q0(t+1)’ pelos valores a impor nas

entradas {S1, R1} e {S0, R0} para lograr as transições de estado em causa …

Considere-se, por exemplo, a linha em que Q1=0 e Q0=0, e atente-se no que sucede quando X=0. O estado

seguinte de ‘Q1’ é ‘0’ e o estado seguinte de ‘Q0’ é ‘0’– e isso remete para a pergunta: para que aconteçam essas

“transições” em {Q1, Q0}, como se devem excitar as entradas dos flip-flops? A resposta da Tabela de Excitação do

flip-flop SR é: a transição ‘0’→‘0’ logra-se aplicando ‘0’ na entrada ‘S’ (sendo indiferente o que se aplica em ‘R’).

São precisamente os valores ‘0X’ o que se escreve nas Tabelas de {S1, R1} e {S0, R0} para o caso em que X=0.

A etapa final é deduzir as expressões simplificadas das entradas {S1, R1, S0, R0} dos flip-flops, e desenhar o

correspondente logigrama Para tal, convirá desdobrar cada uma das Tabelas de {S1, R1} e {S0, R0} em duas

Tabelas, uma por cada uma das entradas {S1, R1, S0, R0} – e aplicar depois o método de Karnaugh…

Sistemas Digitais (Part III)

Page 30 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 31 of 111

Análise de Circuito com Flip-flops SR

Quando um projectista se engaja no desenho de um circuito, e antes de o materializar de facto, e para evitar

posteriores dissabores, há que “fazer a prova dos nove”: será que o circuito concebido segue mesmo o diagrama de

estados desenhado inicialmente? E este passo de maneira nenhuma se deve omitir!

Essa “conferência” deve ser independente do método usado na síntese do circuito – e na prática suporta-se na

Equação característica dos flip-flops usados, como já se testemunhou algures e agora se volta a aplicar:

O circuito envolve dois flip-flops SR – cujos estados se designam de {Q1, Q0}. O primeiro passo na análise do

circuito é, a partir do respectivo logigrama, escrever as expressões algébricas que traduzem o comportamento da

saída do circuito e das entradas dos flip-flops, vidé ao lado.

Tendo em mira o desenho do Diagrama de Estados, o segundo passo é substituir as expressões das entradas dos

flip-flops na equação característica do flip-flop SR. O resultado são expressões que exprimem o estado seguinte de

cada flip-flop – em função dos estados dos flip-flops e da entrada ‘X’ no instante em que ocorre o flanco

descendente do relógio.

O terceiro passo é converter tais expressões nas assim denominadas Tabelas de Estado/Saída – que indicam,

para cada combinação das entradas internas e externas {Q1, Q0, X} num instante ‘t’, a saída ‘Z’ do circuito nesse

instante, e, a ocorrer em ‘t’ o flanco descendente do relógio, os estados dos flip-flops no instante ‘t+1’ seguinte.

No total, existirão três Tabelas, para {Z, Q1 e Q0}:

– à esquerda, dispõem-se duas colunas, representando outros tantos flip-flops, {Q1, Q0};

– e no topo dispõe-se uma linha representando a entrada externa ‘X’;

– estando envolvidos dois flip-flops, e pois que cada um pode assumir dois valores {Q=0 e Q=1}, o circuito

poderá assumir quatro estados distintos, que convirá identificar por códigos binários: {‘S00’, ‘S01’, ‘S10’ e ‘S11’}.

O preenchimento das Tabelas não deverá provocar engulhos. As expressões de {Z, Q1 e Q0} são claras:

– ‘Z’ será ‘1’ apenas para a combinação Q1=1 e X=1;

– quanto a ‘Q1(t+1)’ e ‘Q0(t+1)’, deixa-se ao leitor conferir o seu preenchimento…

O passo seguinte será aglutinar as Tabelas dos estados seguintes dos flip-flops, {Q1(t+1), Q0(t+1)}, numa única,

dita do estado seguinte do circuito, ‘Q1Q0(t+1)’.

A Tabela obtida pode reescrever-se (embora isso não se mostre ao lado) numa outra, dita de Tabela de Estados,

em que cada par de bits {Q1 Q0} é entendido como o código binário de um número, e ele é substituído por um

nome como seja ‘S’ indexado pela representação desse número na base 10; essa Tabela descreve “para que Estado”

evoluem os Estados {S0, S1, S2, S3} do circuito, à medida que se vai alterando a entrada {X}.

Resta desenhar o Diagrama de Estados: a cada estado, associa-se um círculo, etiquetado com um código

binário (ou pelo correspondente nome); depois, traçam-se setas rotuladas, descrevendo graficamente a Tabela.

Veja-se como exemplo a primeira linha, relativa ao estado ‘00’: a saída será Z=0, mas, conforme ‘X’ seja ‘0’ ou

‘1’, assim o estado seguinte será ‘00’ ou ‘01’, respectivamente; isso volve-se numa seta dirigida do círculo ‘00’

para o círculo ‘00’, rotulada com ‘0/0’ e numa outra dirigida do círculo ‘00’ para o círculo ‘01’, rotulada com ‘1/0’.

É hora de se comparar o diagrama de estados obtido a partir do logigrama do circuito com o diagrama de

estados inicialmente concebido – e constatar que aquele está ok: se se confinar a comparação somente a três

estados {S0, S1, S2}, e afora os nomes, são idênticas as saídas e a interligação entre eles…

Há, entretanto, que inquirir: quando se faz o power-on ao circuito, qual o estado em que ele ingressa? A

resposta é: não se sabe! No Projecto entre mãos, isso tem importância: se, ao fazer-se o power-on, o circuito

ingressar nos estados S10 ou S11 e ocorrer X=1, o circuito assinalará, de imediato, erroneamente (porquanto ainda

se não recebeu a sequência ‘101’), o valor ‘1’ – pelo que convirá recorrer a entradas assíncronas (Clear) para

obrigar a que o estado inicial do circuito seja S00.

Sistemas Digitais (Part III)

Page 32 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 33 of 111

Forma Canónica de Mealy

Após dois exemplos de síntese de circuitos sequenciais síncronos, é hora de abstrair das particularidades…

Um relance aos logigramas obtidos descortina uma arquitectura comum, esquematizada ao lado:

à esquerda, encontram-se as entradas, a saber:

– as entradas primárias ou externas, como seja ‘X’ (ou outras);

– as entradas secundárias ou internas, que são as saídas dos flip-flops usados: SR e JK);

– as entradas assíncronas (Preset e Clear), destinadas a inicializar o circuito a um estado específico;

– uma entrada Clock, por onde se recebem os impulsos de relógio – e que alimenta directamente todos os

flip-flops: trata-se de um circuito sequencial síncrono.

Conforme à convenção seguida neste itinerário, as entradas externas localizam-se por cima das entradas

internas: estas são consideradas as entradas de maior peso.

à direita, encontra-se a lógica das saídas, isto é: uma malha combinatória, alimentada pelas entradas

(externas e internas), que gera as saídas do circuito.

A dedução das suas expressões algébricas passa por preencher as Tabelas de Verdade (ou, preferivelmente,

Mapas de Karnaugh) das saídas em função das entradas, externas e internas (que são as saídas dos flip-flops).

A tal lógica das saídas está associado um certo tempo de propagação, seja ‘TZ’, que é o intervalo de tempo que

medeia entre a mudança nos estados dos flip-flops (ou nas entradas externas) e as mudanças nas saídas.

entre ambos, encontra-se a lógica do estado seguinte, isto é: uma malha combinatória, alimentada pelas

entradas (externas e internas), que gera os novos valores a aplicar às entradas dos flip-flops, para que eles evoluam

como deve ser.

A dedução das respectivas expressões algébricas passa por preencher as Tabelas de Verdade (ou Mapas de

Karnaugh) das entradas dos flip-flops em função das entradas (externas e internas).

A tal lógica do estado seguinte está associado um certo tempo de propagação, seja ‘TNovasEntradas’, que é o

intervalo de tempo que decorre entre a mudança nos estados dos flip-flops (ou nas entradas externas) e a mudança

nas entradas dos flip-flops.

Os flip-flops são temporalmente caracterizados por um certo tempo de preparação, tsu, e um certo tempo de

propagação, tpHL e tpLH.

Notável nesta arquitectura é que as saídas, em cada momento, dependem directamente dos estados dos flip-flops

e das entradas externas nesse momento. Ela reflecte o facto de o seu desenho ter seguido o que se denomina de

Modelo de Mealy: em termos do Diagrama de estados, ele é caracterizado pelo fato de as saídas ficarem associadas

a setas, isto é, aos pares “estado de onde a seta provêm” e “entrada externa que a motiva”.

Isso tem uma consequência óbvia: as saídas do circuito poderão mudar no próximo flanco de comutação do

relógio ou aquando da alteração de algumas das entradas externas.

Como testemunho disso, veja-se o diagrama temporal da evolução do 17bº Projecto:

– inicialmente, o circuito encontra-se no estado ‘S0’, e, sendo X=0, está gerando a saída Z=0;

– quando ocorre X=1, não há qualquer consequência imediata;

– a consequência só se manifesta no próximo clock: pois que se verifica X=1, o estado do circuito, e após um

certo tempo de propagação {tpHL ou tpLH}, passa a ser ‘S1’; e, sendo X=1, continua gerando a saída Z=0;

– quando depois ocorre X=0, não há qualquer consequência imediata;

– a consequência manifesta-se no próximo clock: pois que se verifica X=0, o estado do circuito, e após um certo

tempo de propagação {tpHL ou tpLH}, passa a ser ‘S10’ ; e, enquanto X=0, continua gerando a saída Z=0;

– quando a seguir ocorre X=1, a saída, e após um tempo de propagação tZ, passa a ser Z=1.

– no próximo clock, e pois que se verifica X=1, o estado do circuito, e após um certo tempo de propagação

{tpHL ou tpLH}, passa a ser ‘S1’ ; e após um tempo de propagação tZ, fica gerando a saída Z=0…

Moral do Modelo de Mealy: as saídas poderão mudar após se alterar o estado de algum flip-flop (e isso

sucederá quando ocorrer o flanco de comutação do relógio); mas poderão não se manter assim até ao flanco de

comutação seguinte: quando uma entrada muda, elas poderão mudar de imediato.

Sistemas Digitais (Part III)

Page 34 of 111

Sistemas Digitais (Part III)

Síntese clássica (Modelo de Mealy)/

Page 35 of 111

17cº Projecto

Na síntese clássica de circuitos sequenciais síncronos sobressaem dois modelos: o de Moore e o de Mealy. Por

forma a avaliar das vantagens e desvantagens relativas, será natural finalizar esta sessão com a concretização de

um Projecto mediante ambos os modelos…

Considere que, para atravessar uma rua, e estando o semáforo vermelho para os peões, um transeunte clica num

botão (no semáforo); fá-lo durante um intervalo de tempo que é naturalmente variável… Pretende-se um circuito

que, em resposta a esse clicar, produza um impulso de curta duração: um ‘1’ com a duração do período do clock,

seguido de ‘0’s…

Ao lado, encontra-se o Diagrama de Estados seguindo o modelo de Moore:

1. Considere-se o momento do power-on… Será pacífico iniciar o circuito a um estado, seja ‘S0’, em que irá

assinalar ‘0’ na sua saída. O caracter inicial do estado é denotado por uma seta dirigida da esquerda para ‘S0’;

2. Enquanto não se clicar no botão, a entrada do circuito, ‘B’, mantém-se em ‘0’ – e o circuito continua em ‘S0’;

3. Quando o botão for clicado – mais precisamente, no primeiro flanco de comutação do relógio a seguir a esse

clicar -, o circuito ingressa num novo estado, ‘S1’, em que irá assinalar ‘1’ na saída.

4. Estando o circuito em ‘S1’, se o botão ainda continuar a ser clicado, o circuito ingressa, no flanco de

comutação do relógio seguinte, num novo estado, ‘S11’, em que assinalará ‘0’ na saída; e aí continuará até que o

botão deixe de ser clicado: no primeiro flanco de comutação do relógio que se lhe seguir, retornará ao estado

inicial, ‘S0’;

5. Estando o circuito em ‘S1’, se o botão já deixou de ser clicado, o circuito retornará ao estado inicial, ‘S0’.

Deixa-se ao leitor confirmar os vários passos que se seguem em ordem a obter o logigrama do circuito…

Ao lado, encontra-se também o Diagrama de Estados seguindo o modelo de Mealy:

1. Considere-se o momento do power-on… Será pacífico iniciar o circuito a um estado, seja ‘S0’. O caracter

inicial do estado é denotado por uma seta dirigida da esquerda para ‘S0’;

2. Enquanto não se clicar no botão, a entrada do circuito, ‘B’, mantém-se em ‘0’ – e o circuito continua em ‘S0’,

gerando a saída ‘0’;

3. Quando o botão for clicado, a saída do circuito advém ‘1’ imediatamente – e, no primeiro flanco de

comutação do relógio a seguir, o circuito ingressa num novo estado, ‘S1’, em que irá assinalar ‘0’ na saída.

4. Estando o circuito em ‘S1’, se o botão ainda continuar a ser clicado, o circuito mantém-se em ‘S1’,

continuando á assinalar ‘0’ na saída; e aí continuará até que o botão deixe de ser clicado: no primeiro flanco de

comutação do relógio que se lhe seguir, retornará ao estado inicial, ‘S0’;