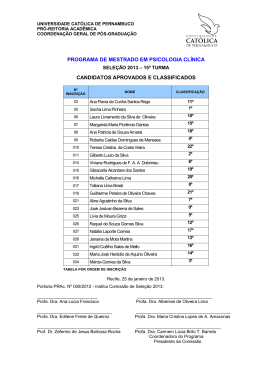

Aula Introdução a Sistemas Digitais Uso das placas de prototipação Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 1 Aula Placa de Prototipação Manual no site: http://www.digilentinc.com/Products/Detail.cfm?Prod=S3BOARD&Nav1=Products&Nav2=Programmable Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 2 Aula Componente FPGA • • • • • • 200,000-gate Xilinx Spartan-3 XC3S200 FPGA in a 256-ball thin Ball Grid Array package (XC3S200FT256) 4,320 logic cell equivalents Twelve 18K-bit block RAMs (216K bits) Usar no projeto ISE Twelve 18x18 hardware multipliers Four Digital Clock Managers (DCMs) Up to 173 user-defined I/O signals Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 3 Aula Placa de Prototipação Pressing a push button generates a logic High on the associated FPGA pin. To light an individual LED, drive the associated FPGA control signal High, which is the opposite polarity from lighting one of the 7-segment LEDs. Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 4 Aula Placa de Prototipação When in the UP or ON position, a switch connects the FPGA pin to VCCO, a logic High. When DOWN or in the OFF position, the switch connects the FPGA pin to ground, a logic Low. The switches typically exhibit about 2 ms of mechanical bounce and there is no active debouncing circuitry, although such circuitry could easily be added to the FPGA design programmed on the board. Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 5 Aula Debouncing Circuitry Registrador deslocamento (buffer) com comparador paralelo IN = ‘1’ IN = ‘1’ (OK) Filtrar o ruído mecânico IN Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 6 Aula Placa de Prototipação •The AN3 anode control signal is Low, enabling the control inputs for the leftmost character. •The segment control inputs, A through G and DP, drive the individual segments that comprise the character. • A Low value lights the individual segment, a High turns off the segment. • A Low on the A input signal, lights segment ‘a’ of the display. • The anode controls for the remaining characters, AN[2:0] are all High, and these characters ignore the values presented on A through G and DP. Ou seja, um display de 7 segmentos é ligado por vez! Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 7 Aula Placa de Prototipação • • Mas então, como podemos ver os 4 displays ligados? É porque acendemos cada display por vez em uma certa frequencia que para o nosso olho, parece que todos estão ligados ao mesmo tempo. Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 8 Aula Placa de Prototipação Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 9 Aula Placa de Prototipação • Programação JTAG Jumpers Paralel JTAG Done LED Cabo da alimentação Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 10 Placa de Prototipação Aula • Oscilador presente na placa (CLK) Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 11 Escolhendo os pinos no ISE Aula UCF file será criado Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 12 Xilinx PACE (pinos) Aula Colocar os pinos correspondentes UCF file será criado Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 13 ISE – programação do FPGA Aula Escolher o .bit file correto!!! Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 14 Aula Projeto: Jogo da Loto Pino T9 clk Sorteio Sistema digital reset FPGA Jogador 1 Jogador 2 Jogador 3 Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt Jogador 4 15 Projeto: Jogo da Loto Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt Aula 16 Projeto: Jogo da Loto • Cada jogador pressiona o botão correspondente para sortear um número. • Após todos os jogadores terem pressionado uma vez o seu botão correspondente, o jogo indica quem sorteou o maior numero (o vencedor). • Cada jogador so pode ter um número sorteado por rodada, ou seja, mesmo que um dos jogadores aperte o botão mais de uma vez por rodada, não será sorteado outro número. • Cada vez que o botão é apertado, no display de 7 segmentos aparece o número sorteado. • No final, o display mostra o vencedor Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt Aula 17 Aula Desafio 1 Geração de numeros aleatorios ou pseudo aleatorios Uso de LFSR: Linear Feedback Shift Register (LFSR) Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 18 Aula LFSR semente (seed) polinômio Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 19 Aula Desafio 2 Temporização: frequencia de atualização dos displays de 7 segmentos • Temos um clock de 50 MHz na placa, ou seja, de 20ns logo para termos valores de: • 1 s => temos que contar ate 50 milhões!!!! O que representa um contador de 26 bits. – Quando contador = “10111110101111000010000000” 26 bits Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 20 O refresh do display é dado… Aula pelo bit 6 do cont Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 21 Uso de flag • O uso do flag impossibilita que um novo número seja sorteado pelo mesmo jogador em uma mesma rodada. • Para iniciar uma nova jogada é preciso RESET. Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt Aula 22 Aula Exercício 1. Tente modificar o VHDL para que o jogador 2 possa sempre jogar duas vezes por rodada, tal que aumente suas chances de tirar um maior numero. 2. Tente modificar o VHDL para que os numeros sorteados sejam apenas de 0 a 15. Disciplina: Sistemas Digitais – Profa. Dra. Fernanda Gusmão de Lima Kastensmidt 23

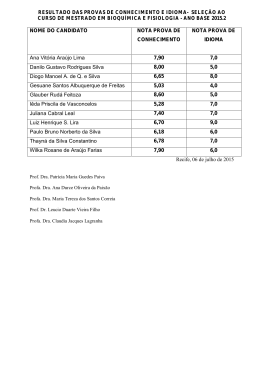

Download