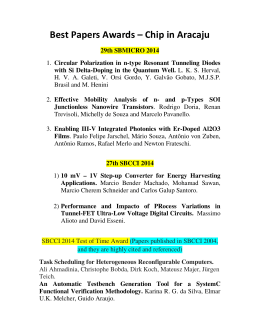

Preliminary Program - SBCCI 2014 - Tutorials Tuesday, September 2nd Chair: Sergio Bampi (UFRGS, Brazil) Tutorial 1 08:40-10:20 Sub-Threshold VLSI Digital Circuits and Systems: A Design Perspective Prof. Massimo Alioto National University of Singapore (NUS) Coffee Break 10:20-10:40 Tutorial 2 10:40-12:20 Ultra-Low Voltage Analog Circuits Prof. Peter Kinget Columbia University, USA Lunch 12:20-14:00 Tutorial 3 14:00-15:30 Computing Efficiently, and Approximately Prof. Anand Raghunathan Purdue University, USA Tutorial 4 15:30-17:00 Carbon Nanotube Imperfection-Immune Digital VLSI Prof. Subhasish Mitra Stanford University, USA Coffee Break 17:00-17:20 Visit to Exhibitors (booths) 17:20-18:20 Opening Ceremony 18:20-18:40 MSc and PhD Awards 18:40-19:00 SBMICRO Awards 19:00-19:20 Reception and Coktail 19:30-22:00 1 - Keynotes Wednesday, September 3rd Keynote SBCCI 09:00-10:20 Robust Systems: From Clouds to Nanotubes Prof. Subhasish Mitra Stanford University, USA Coffee Break 10:20-10:40 Keynote SBMicro 10:40-12:00 Device Design Considerations for 14nm Node, 10nm Node and Beyond Bruce Bennet Doris IBM, Albany (NY), USA Lunch 12:00-14:00 - Technical Sessions Wednesday, September 3rd Exhibitors (booths) 14:00-14:40 Session 1 – SoC, NoC and Embedded Systems I Room: Cotinguiba Chair: Martha Johanna Sepúlveda Flórez 14:40-15:00 Balanced Prefetching Aggressiveness Controller for NoC-Based Multiprocessor André Aziz, Maria Cireno, Edna Barros and Bruno Prado 15:00-15:20 Bee Colony Algorithm Applied to Memory Architecture Exploration Intended for Energy Reduction Crystal de Menezes Santos and Abel Guilhermino Silva-Filho 15:20-15:40 Designing Ultra-Low Power Systems with Non-Uniform Sampling and Event-Driven Logic Giuseppe Roa, Tugdual Le Pelleter, Agnès Bonvilain, Alejandro Chagoya and Laurent Fesquet 15:40-16:00 Worst-Case Delay Bounds in Deadlock-Free Wormhole Networks-on-Chip with Virtual Channels Yue Qian, Junhui Wang and Zhonghai Lu Coffee Break 16:00-16:20 Invited Talk I 16:20-17:00 3D Architectures: Promises and Design Challenges Prof. Pascal Vivet (CEA-Leti, France) 2 Session 2 – Analog & RF & Mixed Signal I Room: Cotinguiba Chair: Jacobus Swart 17:00-17:20 Design for Stability of Active Inductor with Feedback Resistance Gabriel R. Guerreiro and João Navarro 17:20-17:40 High Linearity and Large Output Swing Sub-Hz Pre-Amplifier for Portable Biomedical Applications Moacir F. C. Monteiro, Hamilton Klimach and Sérgio Bampi 17:40-18:00 Impact of ESD Protection and Power Supply Decoupling on 10 GHz Low Noise Amplifier Wilson J. Bortoletto Machado and Calvin Plett 18:00-18:20 Improved Charge Pump Circuits for Standard CMOS Technologies Carlos Augusto de Moraes Cruz, Carlos Alberto dos Reis Filho and Davies William de Lima Monteiro 18:20-18:40 System-Level Design of a Reconfigurable CT ∑Δ Modulator for Multi-Standard Wireless Applications Raphael Andreoni Viera, Cesar Augusto Prior, Jorge de La Cruz and João Baptista Martins Thursday, September 4th Session 3 – CAD, Verification and Test I Room: Cotinguiba Chair: André Inácio Reis 08:20-08:40 CLEVER: Cross-Layer Error Verification, Evaluation and Reporting Rafael Kioji Vivas Maeda and Frank Sill Torres 08:40-09:00 Determining Cases of Scenarios to Improve Coverage in Simulation-Based Verification Shuo Yang, Robert Wille and Rolf Drechsler 09:00-09:20 MogaMap and DynPack: Multi-Objective Mapping and Packing Algorithms for Optimization of Area, Performance and Power Consumption in FPGAs Viviane L. Souza and Abel G. Silva-Filho 09:20-09:40 Validating SystemC Implementations Against Their Formal Specifications Jannis Stoppe, Robert Wille and Rolf Drechsler 09:40-10:00 Verification of Hardware Implementations Through Correctness of Their Recursive Definitions in PVS Ariane Alves Almeida, Janier Arias-Garcia, Carlos Humberto Llanos Quintero and Maurício Ayala-Rincon Exhibitors (booths) 10:00-10:20 Coffee Break 10:20-10:40 3 Invited Talk II 10:40-11:20 Self-Verification as the Key Technology for Next Generation Electronic Systems Prof. Rolf Drechsler (Bremen University & DFKI, Germany) Session 4 – CAD, Verification and Test II Room: Cotinguiba Chair: Frank Sill Torres 11:20-11:40 Automated Synthesis of Cell Libraries for Asynchronous Circuits Matheus T. Moreira, Michel Arendt, Adriel Ziesemer Jr, Ricardo Reis and Ney L. V. Calazans 11:40-12:00 Reliability Analysis of a 130nm Charge Redistribution SAR ADC under Single Event Effects Alisson J. C. Lanot and Tiago R. Balen 12:00-12:20 A Fast Runtime Fault Recovery Approach for NoC-Based MPSoCs for Performance Constrained Applications Eduardo Wachter, Augusto Erichsen, Leonardo Juracy, Alexandre Amory and Fernando G. Moraes Lunch 12:20-14:00 Invited Talk III 14:00-14:40 An Overview of Radio Frequency Technologies and Their Influence on the Power Efficiency of Wireless Communication Systems Solon J. Spiegel (Rio Systems, Israel) Session 5 – Analog & RF & Mixed Signal II Room: Cotinguiba Chair: Sergio Bampi 14:40-15:00 A Compact and Power-Efficient CMOS Battery Charger for Implantable Devices Jader A. de Lima 15:00-15:20 A Low-Voltage Current Reference with High Immunity to EMI David Cordova, Pedro Toledo and Eric Fabris 15:20-15:40 Self-Biased CMOS Current Reference Based on the ZTC Operation Condition Pedro Toledo, Hamilton Klimach, David Cordova, Sergio Bampi and Eric Fabris 15:40-16:00 Sub-1 V Supply Nano-Watt MOSFET-Only Threshold Voltage Extractor Circuit Oscar E. Mattia, Hamilton Klimach and Sergio Bampi Coffee Break 16:00-16:20 Invited Talk IV 16:20-17:00 Dynamic/Self-Adaptive NoC Prof. Jean-Philippe Diguet (University Européenne de Bretagne - UBS, France) 4 Session 6 – Analog & RF & Mixed Signal III Room: Cotinguiba Chair: André Mariano 17:00-17:20 10 mV – 1V Step-up Converter for Energy Harvesting Applications Marcio Bender Machado, Mohamad Sawan, Marcio Cherem Schneider and Carlos Galup-Montoro 17:20-17:40 A 2-Transistor Sub-1V Low Power Temperature Compensated CMOS Voltage Reference Alfredo Olmos, Juan Pablo Martinez Brito, Fabrício Ferreira, Fernando Chavez and Marcelo S. Lubaszewski 17:40-18:00 A CMOS Down-Conversion Mixer with High IIP2 and IIP3 for Multi-Band and Multiple Standards David Cordova, Sergio Bampi and Eric Fabris 18:00-18:20 SiGe HBT mm-Wave DC Coupled Ultra-Wide-Band Low Noise Monolithic Amplifiers André F. Ponchet, Ezio M. Bastida, Stefan Tenenbaum, Roberto Panepucci and Jacobus W. Swart Exhibitors (booths) 18:20-18:40 PANEL – Industry and Goverment Strategies for Micro/Nanoelectronics in Brazil 18:20-19:40 Conference Dinner 20:00 Friday, September 5th Session 7 – Digital, Reconfigurable & Applications I Room: Cotinguiba Chair: Fernando Gehm Moraes 08:20-08:40 A Quantum-Dot Cellular Automata Processor Design Elverton C. Fazzion, Osvaldo L. H. M. Fonseca, Douglas Sales Silva, Jeferson F. Chaves, Antônio O. Fernandes, José A. M. Nacif and Omar Paranaiba Vilela Neto 08:40-09:00 An Efficient Parallel Yet Pipelined Reconfigurable Architecture for M-PLN Weightless Neural Networks Felipe Pereira da Silva, Alan Oliveira de Sá, Nadia Nedjah and Luiza de Macedo Mourelle 09:00-09:20 A Memory Energy Consumption Analysis of Motion Estimation Algorithms using Data Reuse in Video Coding Systems Lívia Amaral, Dieison Silveira, Guilherme Povala, Luciano Agostini, Marcelo Porto and Bruno Zatt 09:20-09:40 Performance and Impact of Process Variations in Tunnel-FET Ultra-Low Voltage Digital Circuits Massimo Alioto and David Esseni 09:40-10:00 Towards a Framework to Perform DPA Attack on GALS Pipeline Architectures Luciano Ludwig Loder, Marcelo Fay, Adão Antônio de Souza Junior and Rafael Iankowski Soares Exhibitors (booths) 10:00-10:20 5 Coffee Break 10:20-10:40 Session 8 – Digital, Reconfigurable & Applications II Room: Cotinguiba Chair: Altamiro Susin 10:40-11:00 A Real-Time 5-Views HD 1080p Architecture for 3D-HEVC Depth Modeling Mode 4 Gustavo Sanchez, Bruno Zatt, Marcelo Porto and Luciano Agostini 11:00-11:20 Design and Implementation of a Pipelined Decoder for Generalized Concatenated Codes Jens Spinner and Jürgen Freudenberger 11:20-11:40 Energy-Efficient Hadamard-Based SATD Architectures Luiz Henrique de Lorenzi Cancellier, André Beims Bräscher, Ismael Seidel and José Luís Güntzel 11:40-12:00 Hardware Design and FPGA Implementation for Road Plane Extraction Based on V-Disparity Approach Imad Benacer, Aicha Hamissi and Abdelhakim Khouas 12:00-12:20 VLSI Implementation of an OFDMA-WRAN Auto-Correlation João Carlos Nunes Bittencourt, Nelson Alves Ferreira Neto, Joaquim Ranyere S. de Oliveira and Wagner Luiz Alves de Oliveira Lunch 12:20-14:00 Invited Talk V 14:00-14:40 Fabless and IP Semiconductor Business: A Technical and Historical Prospective Victor Grimblatt (Twitter, LinkedIn, Synopsys Chile R&D Center) Session 9 – CAD, Verification and Test III Room: Cotinguiba Chair: Edna Barros 14:40-15:00 A Novel State Assignment Method for Extended Burst-Mode FSM Design using Genetic Algorithm Tiago Curtinhas, Duarte L. Oliveira, Lester A. Faria and Osamu Saotome 15:00-15:20 Deriving Reduced Transistor Count Circuits from AIGS Jody Maick Matos, Marcus Ritt, Renato Ribas and André Reis 15:20-15:40 Exploring Independent Gates in FinFET-Based Transistor Network Generation Vinicius N. Possani, André I. Reis, Renato P. Ribas, Felipe S. Marques and Leomar S. da Rosa Junior 15:40-16:00 Simulation Based Verification with Range Based Signal Representations for Mixed-Signal Systems Michael Kaergel, Markus Olbrich and Erich Barke Coffee Break 16:00-16:20 6 Session 10 – SoC, NoC and Embedded Systems II Room: Sergipe Chair: Cesar Albenes Zeferino 14:40-15:00 Runtime QoS Support for MPSoC: A Processor Centric Approach Marcelo Ruaro, Everton A. Carara and Fernando G. Moraes 15:00-15:20 Full-Virtualization on MIPS-Based MPSoCs Embedded Platforms with Real-Time Support Carlos Moratelli, Samir Zampiva and Fabiano Hessel 15:20-15:40 Hardware/Software Debugging of Large Scale Many-Core Architectures Stephanie Friederich, Jan Heisswolf and Jürgen Becker 15:40-16:00 Adaptive Shared Memory Control for Multimedia Systems-on-Chip Alexsandro Bonatto, Fábio Pereira, André Borin, Marcelo Negreiros and Altamiro Susin Coffee Break 16:00-16:20 Best Papers & Closing Ceremony 16:20-17:00 7

Download